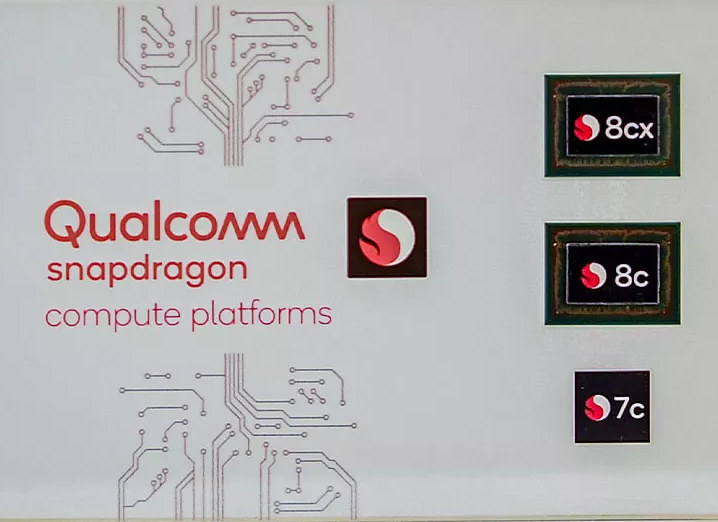

Nearly exactly one year ago, Qualcomm announced the Snapdragon 8cx processor for always-on always-connected PCs, and lateron Qualcomm and UL released PCMark 10 benchmark results showing Snapdragon 8cx had similar performance to a 15W Intel Core i5-8250U Kaby Lake-R processor, but with much better efficiency. The price of such laptops is still fairly high with Samsung Galaxy Book S announced in August for $1,000, and possibly canceled at this stage. Microsoft SQ1 powered Surface Pro X tablet is the only system based on Qualcomm Arm technology (customized version of Snapdragon 8cx) available now, and also sells for $1,000 and up. Qualcomm has now unveiled Snapdragon 7c and 8c arm processor to address the entry-level and mainstream markets of connected mobile PCs. Qualcomm Snapdragon 7c Specifications: CPU – Octa-core Kryo 468 processor @ up to 2.45 GHz GPU – Qualcomm Adreno 618 GPU DSP – Qualcomm Hexagon 692 DSP with Hexagon […]

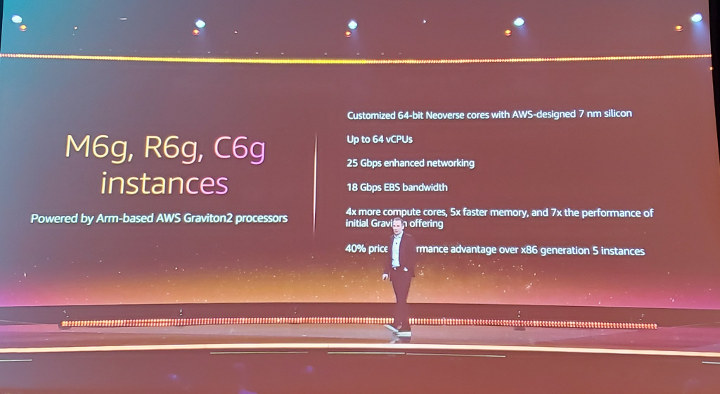

AWS EC2 6th Gen Instances are 7x Faster thanks to Graviton 2 Arm Neoverse N1 Custom Processor

Last year Amazon introduced their first 64-bit Arm-based ECS2 “A1” instances which were found to deliver up to 45% cost savings over x86 Instances for the right workloads. A few months ago, AWS (Amazon Web Services) provides a new offering with bare-metal A1 instances, and with re:invent 2019 now taking place the company has unveiled AWS ECS2 6th generation Arm instances (which they did not call A2 instances yet) powered by Graviton 2 processor comprised of custom Arm Neoverse N1 cores and promising up to 7x the performance of the original A1 instances. There will be three types of Graviton2-powered EC2 instances with the d suffix indicating NVMe local storage: M6g and M6gd for General Purpose workloads (application servers, mid-size data stores, microservices, and cluster computing) with 1 to 64 vCPUs and up to 256 GB of memory. C6g and C6gd for Compute-Optimized workloads (high-performance computing, video encoding, gaming, and […]

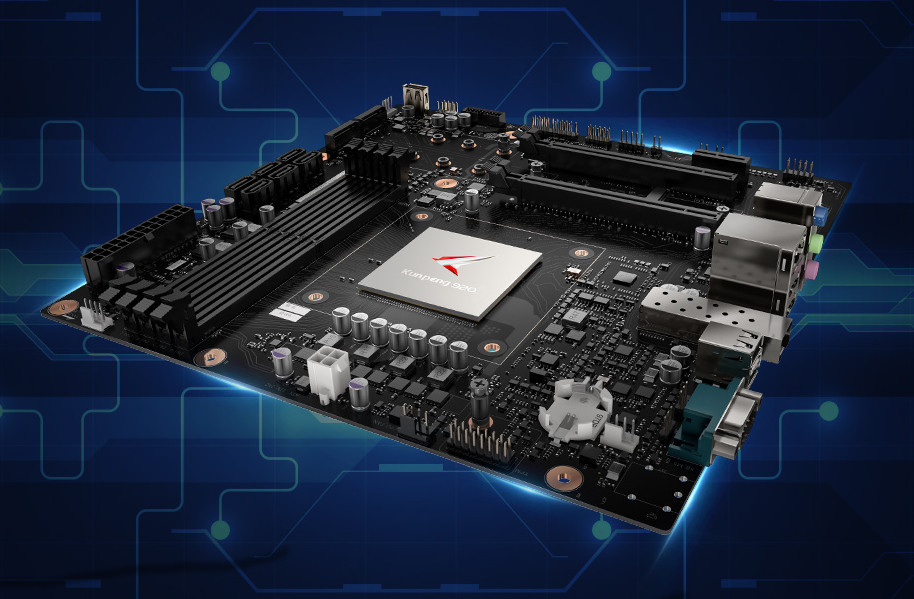

Huawei Kunpeng Desktop Board is Powered by Kunpeng 920 Armv8 Server Processor

Huawei Kunpeng 920 is an Armv8 server SoC with up to 64 cores that can be found in the company’s TaiShan series servers. But the company has now designed “Kunpeng Desktop Board” featuring the quad or octa-core version of Kunpeng 920 SoC, in order to create Arm-powered desktop computers. Kunpeng Desktop Board (model D920S10) preliminary specifications: Processor – Kunpeng 920 processor with 4/8 cores at up to 2.6 GHz System Memory – 4x DDR4-2400 UDIMM slots for up to 64 GB RAM Storage – 6x SATA 3.0 hard drive interfaces, 2x M.2 SSD slots Connectivity – 2x LOM (LAN on Motherboard) NIC supporting Gigabit Ethernet network ports or optical ports USB – 4x USB 3.0 and 4x USB 2.0 ports Audio – Combo with 3x 3.5mm audio jacks Serial – DB9 connector Expansions – 1x PCIe 3.0 x16, 1x PCIe 3.0 x4, and 1x PCIe 3.0 x1 slots LOM Network […]

Hacarus Embedded AI Computing Kit Leverages Sparse Modeling Technology

AI training often requires thousands of samples to become accurate, and it can be costly and time-consuming, for example, if you want to train a model to detect manufacturing defects you’d need to provide images with both defective samples and good samples. Japanese AI experts at Hacarus have been working on a solution called Sparse Modeling which requires about 50 samples or even less for training, and worked with Congatec to provides an embedded AI computing kit leveraging the technology. Sparse Modeling Technology Hacarus does not go into great detail but explains Sparse Modeling technology is using a data modeling approach that focuses on identifying unique characteristics, in a way that humans recognize friends and family without having to look at everything from feet to head. That means algorithms based on Sparse Modeling do not need as much data as traditional AI solutions, leading to much smaller AI footprint suitable […]

Linux 5.4 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.4: Not a lot happened this last week, which is just how I like it. And as expected, most of the pull requests I got were for the 5.5 merge window, which I’ll obviously start working through tomorrow. What little there is here is mostly some networking updates (mix of network drivers and core networking), and some minor GPU driver updates. Other than that it’s a small collection of random other things all over. The appended shortlog is small enough that you might as well just scroll through it. Anyway, this obviously opens the merge window for 5.5. It’s not ideal timing with Thanksgiving week coming up, but it hopefully shouldn’t be too much of an issue. If I fall behind (not because I’m all that big of a fan of the indiscriminate and relentless turkey-killing holiday) it’s because we’ve got […]

X96 Link 2-in-1 Android TV Box & Router Combines Arm and MIPS Processors

Most TV boxes come with WiFi and/or Ethernet to access the Internet or local network in order to stream videos, but there are a few rare exceptions with TV boxes also acting as router such as Zome ZMT-330A we covered way back in 2014 with two Ethernet ports. Shenzhen Tomato informed me about another TV box router product dubbed Nut Link powered by Amlogic S905W processor and equipped with not two but three Ethernet ports. A quick web search reveals the device is better known as X96 Link and sells for as low as $39 shipped on sites like GearBest or Aliexpress. X96 Link specifications: SoC – Amlogic S905W quad-core Arm Cortex-A53 processor with penta-core Mali-450MP GPU System Memory – 2GB DDR3 Storage – 16GB eMMC flash, MicroSD card slot Video & Audio Output – HDMI 2.0a port up to 4K @ 60 Hzm AV port for composite video and […]

Giveaway Week Winners – November 2019

We just had another of our yearly “Giveaway week” on CNX Software with 7 prizes including Arm and RISC-V development boards, NB-IoT tracker, USB-C hub, as well as development kits based on ESP32 or ESP8266 WiSoCs. People just had to comment within a 48 hours period, and we would randomly select a winner each day. We now have all confirmed winners with a strong start from Europe, Asia catching up mid-week, before with Poland and Brazil taking the week-end prizes: Balena Fin Developer Kit – Laurent H, FRANCE WisCellular NB-IoT & eMTC GPS Tracker – Jimmy, SWEDEN MINIX NEO S1 USB-C Hub with 120GB built-in SSD – Jeroen, BELGIUM Maixduino Sipeed M1 RISC-V AI Kit – Nguyen Tung, VIETNAM ANAVI Gas Detector Starter Kit – Bumsik Kim, SOUTH KOREA Particle Mesh IoT Development Kit – Wojciech Lubicz-Lapinski, POLAND NanoPi M4V2 SBC & Metal Case Kit – Thiago Tavares, BRAZIL I […]

$1,000 Microsoft Surface Pro X Tablet is Powered by Microsoft SQ1 Arm Processor

Arm Windows 10 laptops, tablets, and 2-in-1 hybrids have been around for a couple of years all powered by Qualcomm Snapdragon processors so far. Now Microsoft is launching Surface Pro X Windows 10 tablet powered by its own Microsoft SQ1 Arm processor. It sells for $999 with 8GB RAM, 128GB storage, and a 13″ 2880 x 1920 x pixel touchscreen display in the default configuration, but you can also customize your order with up to 16GB RAM, 512GB SSD storage, optional keyboard and stylus for over $2,000. Microsoft Surface Pro X Specification Microsoft Surface Pro X specification: SoC – Microsoft SQ1 Arm processor @ 3.0 GHz with Adreno 685 GPU System Memory – 8GB or 16GB LPDDR4x RAM at 3733Mbps (option for 16GB) Storage – Removable 128, 256, or 512GB M.2 SSD Display – 13” PixelSense Display with 2880 x 1920 resolution (3:2 aspect ratio), 10 point multi-touch, 450 nits […]