Qualcomm’s Snapdragon 7c Gen 2 SoC for entry-level laptops and Chromebooks follows the steps of the Snapdragon 7c processor with a slightly higher frequency for the Kryo 468 cores, leading to a 6% performance improvements. As we’ll see below, most of the specifications are exactly the same, except the built-in Snapdragon X15 LTE modem is now listed as supporting LTE Cat 14 up to 600 Mbps, instead of LTE Cat 15 up to 800 Mbps, and UFS downgraded to UFS 2.1 from UFS 3.0. Snapdragon 7c Gen 2 specifications: CPU – Octa-core Kryo 468 (Cortex-A76) processor up to 2.55 GHz GPU – Unnamed Qualcomm Adreno GPU (Note: Snapdragon 7c had Qualcomm Adreno 618 GPU) DSP – Qualcomm Hexagon 692 DSP Memory – 2x 16-bit LPDDR4x-4266 Storage – eMMC 5.1, UFS 2.1 Display On-device display up to QXGA (2048 x 1536) @ 60 Hz External display up to QHD (2560×1440) @ […]

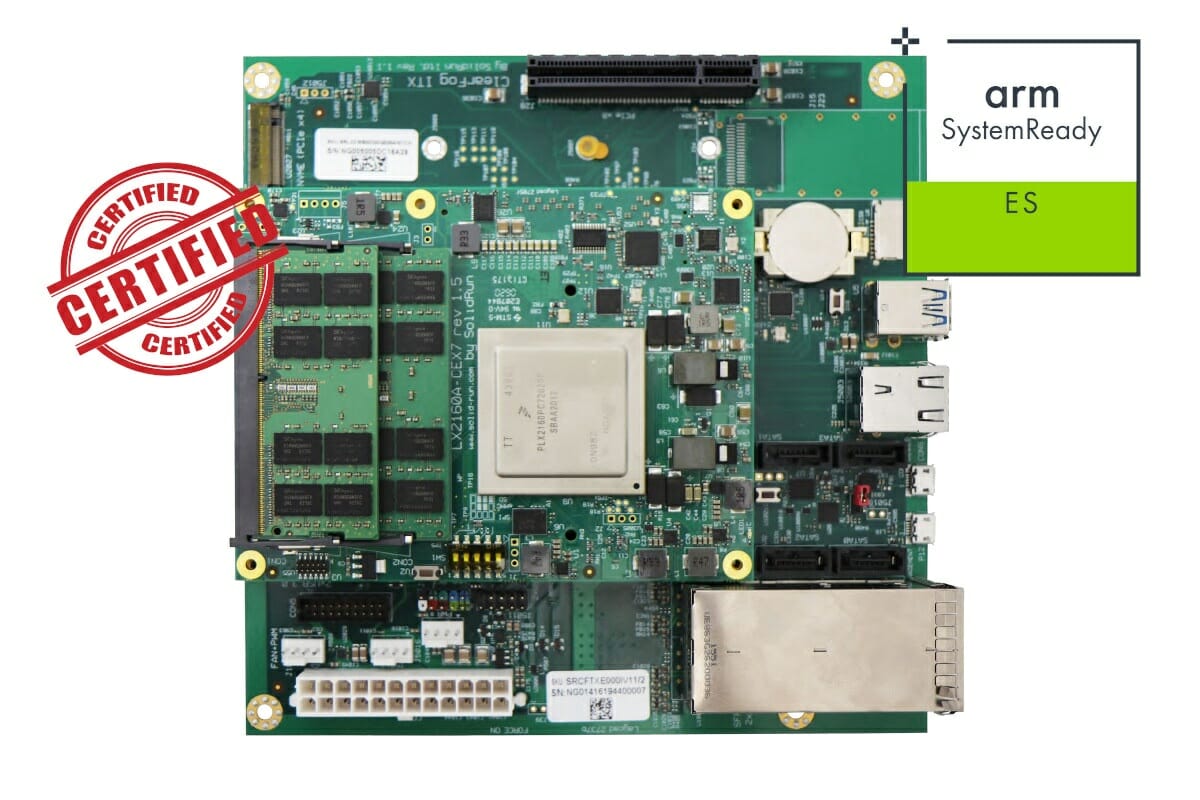

SolidRun HoneyComb LX2K becomes a certified Arm SystemReady ES platform

SolidRun HoneyComb LX2K is part of our list of the 5 most powerful Arm SBC’s in 2021. The mini-ITX board features an NXP LX2160A 16-core Arm Cortex-A72 processor, supports up to 64GB RAM, offers high-speed networking thanks to up to 4x SFP+ 10GbE cages and a Gigabit Ethernet port, as well as four SATA ports, a PCIe x8 slot, M.2 SSD slot and more. The board is ideal for networking applications and can be also be integrated into an Arm workstation for native application development. But just last month, we noted that while SolidRun talked about SBSA compliance a while ago, the status was unclear. The good news is that HoneyComb LX2K has just now become a certified Arm SystemReady ES (Embedded Server) compliant platform. Arm SystemReady is a set of standards and a compliance certification program that ensures systems just work with generic, off-the-shelf operating systems straight out of […]

Huawei Qingyun L410 Linux laptop is powered by Kirin 990 Arm processor

While it’s already possible to purchase an Arm Linux laptop like PineBook Pro, the Rockchip RK3399 processor, and 4GB RAM may be limiting to some, especially when wanting to multitask. But most likely out of necessity, Huawei has unveiled a more powerful Arm Linux laptop with Huawei Qingyun L410 powered by a 7nm Kirin 990 octa-core Cortex A76/A55 processor, coupled with 8GB RAM, up to 512GB of storage, and a 14-inch display. Huawei Qingyun L410(L410 KLVU-WDU0) preliminary specifications: SoC – Hisilicon Kirin 990 octa-core processor with 2x Cortex-A76 @ 2.86GHz, 2x Cortex-A76 @ 2.09GHz, 4x Cortex A55 @ 1.86GHz, Arm Mali-G76MP16 @ 700 MHz, DaVinci NPU System Memory – 8GB LPDDR4-4266 Storage – Up to 512 UFS of storage (SSD or UFS 3.0 TBC) Display – 14-inch 2K display with a 3:2 aspect ratio Camera – “hidden camera” Video – 4K 60fps video support Misc – Fingerprint sensor Dimensions – […]

JingPad A1 Arm Linux 2-in-1 tablet can run Android apps (Crowdfunding)

If you are looking for an Arm Linux tablet option are limited with, for instance, the Allwinner A64 powered 10.1-inch PineTab tablet or the CutiePi tablet with a Raspberry Pi CM4 module. If you’d like more performance, the upcoming JingPad A1 2-in-1 tablet might be an option worth looking into. The 11-inch 2K tablet features an octa-core Cortex-A75/A55 processor, coupled with 6GB RAM and 128GB storage, and can be transformed into a laptop with an optional detachable keyboard. JingPad A1 runs the company’s JingOS optimized for tablets, and which also happens to be able to run Android apps. JingPad A1 specifications: SoC – Unnamed octa-core processor with 4x Arm Cortex-A75 CPU cores @ 2 GHz, 4x Arm Cortex-A55 CPU cores @ 1.8 GHz, Imagination PowerVR GM9446 GPU @ 800 MHz. (I can’t find an exact match, but if it looks similar to MediaTek Helio P90 except the configuration is 2x […]

Linux 5.12 – Main Changes, Arm, MIPS and RISC-V Architectures

Linux 5.12 release was expected last Sunday, but Linus Torvalds decided to release one more release candidate, namely Linux 5.12-RC8, to “make sure things are all settled down“, so the latest Linux kernel is now expected this weekend. Tihs should not yield any significant changes, so we can check what’s new in Linux 5.12, notably with regards to Arm, MIPS, and RISC-V architectures often used in SoC’s found in embedded systems. Around two months ago, the release of Linux 5.11 added support for Intel’s software guard extensions (SGX) and Platform Monitoring Technology (PMT), AMD “Van Gogh” and “Dimgrey cavefish” graphics processors, MIPI I3C host controller interfaces, and much more. Some interesting changes in Linux 5.12 include: Added support for ACRN hypervisor designed for IoT & embedded devices Added support for Playstation DualSense & Nintendo 64 game controllers, as well as Nintendo 64 data cartridges Dynamic thermal power management via a […]

Top 5 most powerful Arm SBC’s & Devkits in 2021

While companies like Hardkernel, Raspberry Pi, Orange Pi, and FriendlyArm offers affordable, great little Arm Linux development boards that are suitable for many projects, in some cases, your requirements may lead you to spend a bit more for either extra CPU power, more memory, AI processing power, faster I/Os and so on. That’s why I did a list of the most powerful Arm single board computers in late 2017, but with over three years passed since then an update is warranted. The boards from the list must be easily purchasable from individuals (with the cash to spare) or small companies, so we’ll exclude hard-to-source hardware, as well as Arm server boards like Ampere eMAG motherboard, that do not really qualify as single board computers. Snapdragon 888 Mobile Hardware Development Kit While there are plenty of Cortex-A72/A73 development boards around, it’s much hardware to find one with more recent Cortex-X1 or […]

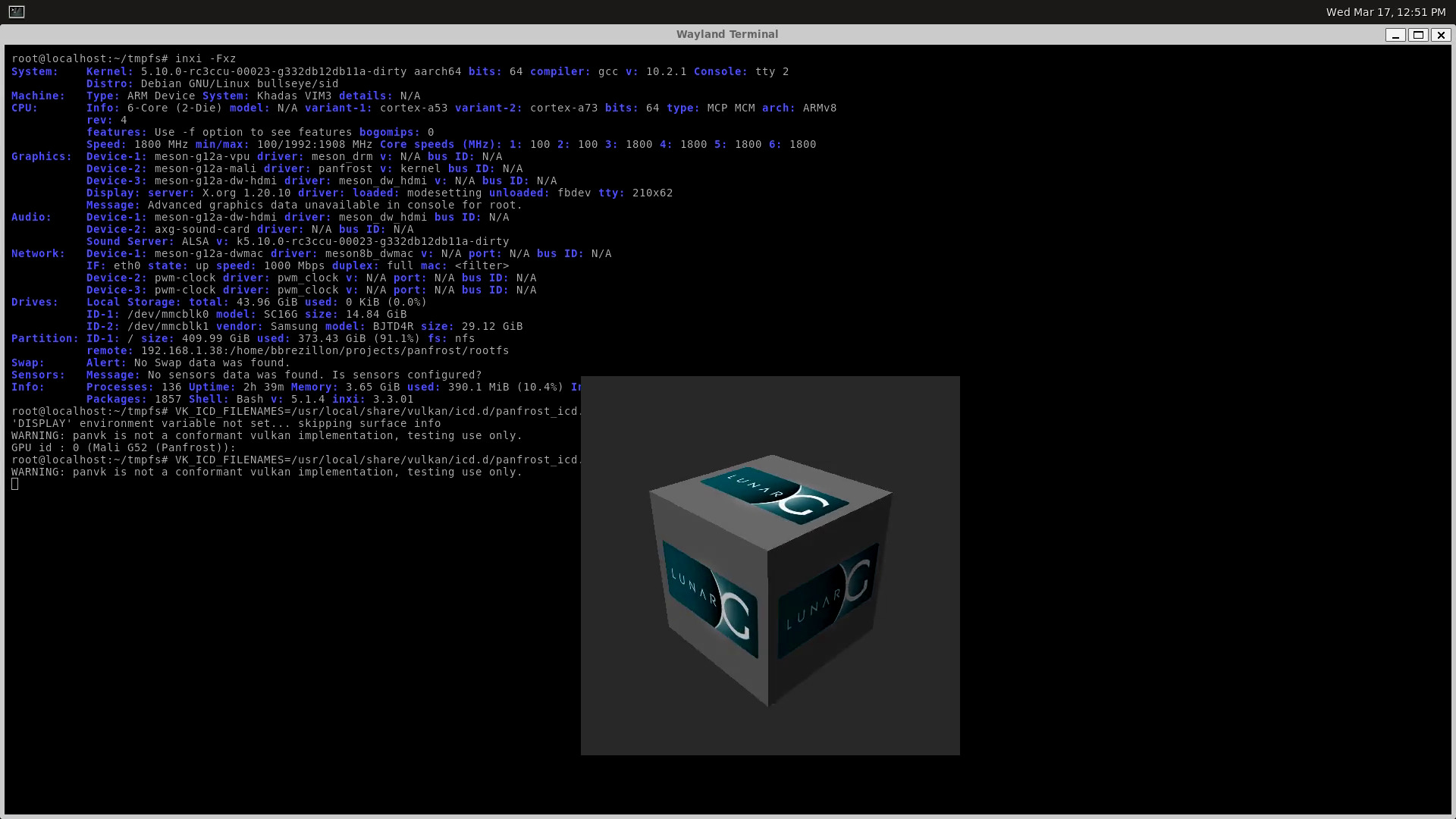

PanVk – Panfrost gets a Vulkan driver

We’ve followed with interest the progress of the Panfrost open-source driver for Arm Mali Midgard and Bifrost GPUs which has gotten more traction over time with official support from Arm and is getting closer to OpenGL ES 3.0 compliance with work on OpenGL ES 3.1 on the way. But Collabora has now started working on PanVk driver for the more recent Vulkan graphics API, as part of the Panfrost project. This is very early stage, but the 3D cube demo above appears to be rendered with Panfrost’s PanVk Vulkan driver on Wayland in a Khadas VIM3 board based on Amlogic A311D hexa-core Cortex-A73/A53 processor with a Mali-G52 GPU. As noted in the announcement, getting a useful Vulkan driver will take time as : The driver lacks almost all core features that would make it usable for real-world applications Optimizations are left on the side for now The code base is […]

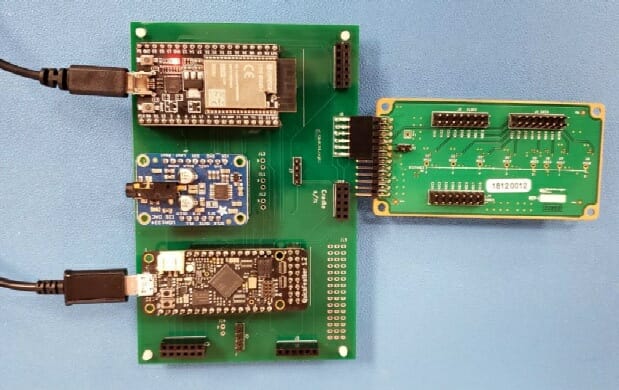

QuickLogic’s Hearable Reference Design enables Alexa Voice-Initiated Devices

Last year we saw QuickFeather board featuring EOS S3 Cortex-M4F MCU with embedded FPGA, which was a crowdfunding project. This year the company has launched its smart hearable reference design based on a similar processor by QuickLogic. The device is dedicated to “Voice-Initiated, Hands-Free, Alexa Built-In Devices with Close-Talk Support.” QuickLogic’s smart hearable reference design is based on the company’s Open Reconfigurable Computing (QORC) which supports a complete open-source set of development options for the MCU and FPGA devices. It is also built on the EOS S3 Voice Processor and the QuickFeather open source development kit. This can enhance the user experience with a longer battery life of the device. The EOS S3 Arm Cortex- M4 processor features Low Power Sound Detection (LPSD) technology along with DSP Concepts’ TalkTo noise suppression and beamforming technology for the directional transmission of signals. It also comes with Alexa Wake Word engine technology, an […]