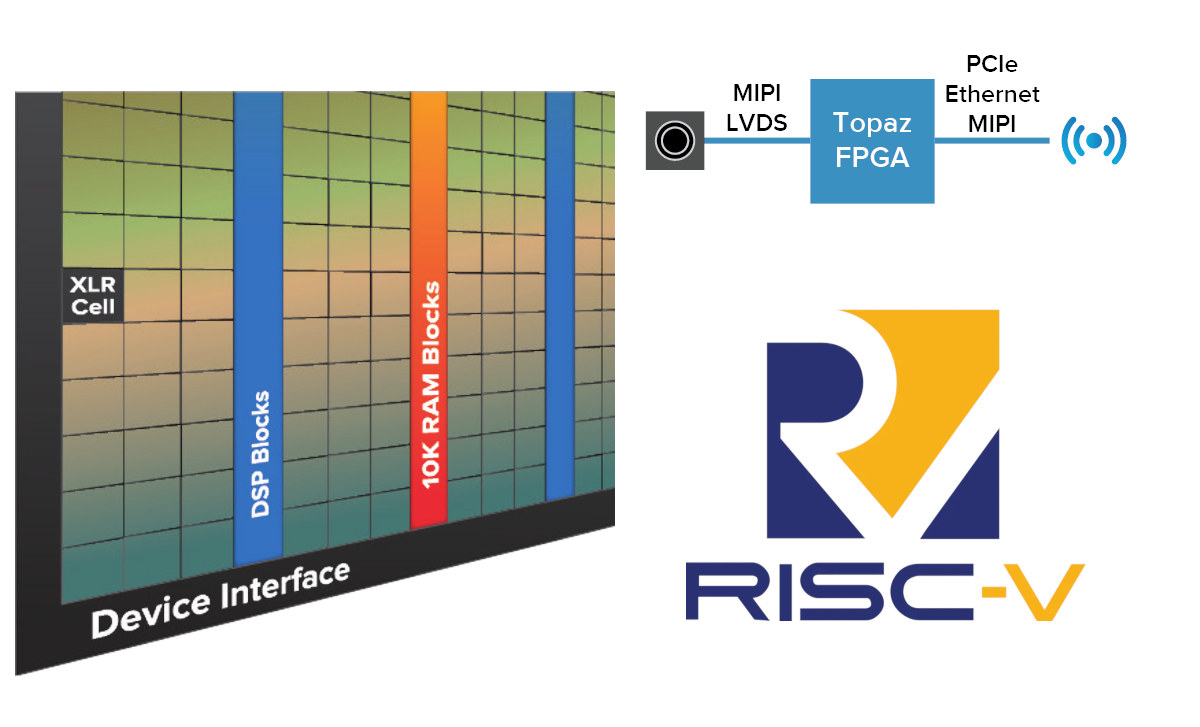

Efinix Topaz is a new low-power RISC-V SoC FPGA family manufactured with the same 16nm TSMC process as the Efinix Titanium SoC FPGA, but optimized for high-performance in a low-power footprint, and targetting high-volume, mass-market applications. The Topaz SoC FPGAs provide fewer features than the Titanium family but still offer up to four RISC-V hard cores, PCIe Gen3, MIPI interfaces, LPDDR4, LVDS, and 12.5 Gbps transmitter with most features being optional and depending on the exact SKUs selected. Efinix Topaz key features and specifications: FPGA compute fabric Up to 326,080 logic elements (LEs) Up to 19.22 Mbits embedded memory Up to 1,877 10-Kbit SRAM blocks Up to 1,008 embedded DSP blocks Memory – 10-kbit high-speed, embedded SRAM, configurable as single-port RAM, simple dual-port RAM, true dual-port RAM, or ROM FPGA interface blocks Optional 32-bit quad-core hardened RISC-V block (RISCV32I with M, A, C, F, and D extensions and six pipeline […]

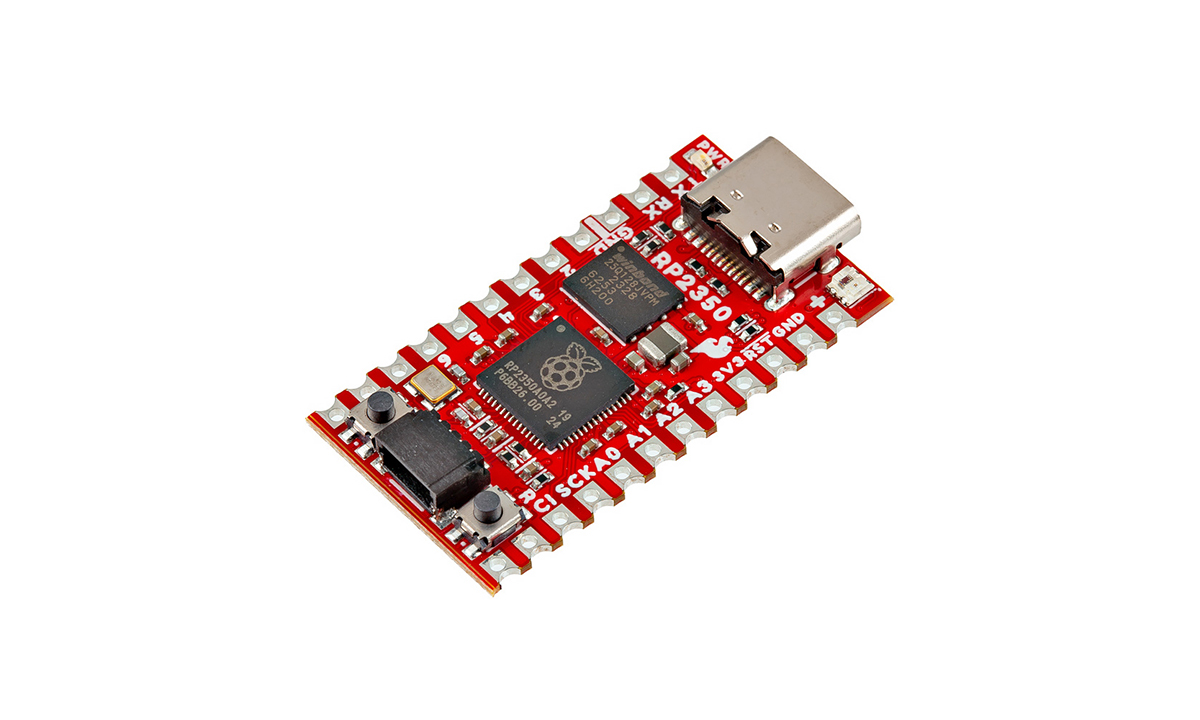

SparkFun Pro Micro – RP2350 development board comes with 16MB flash, 8MB PSRAM

The SparkFun Pro Micro – RP2350 is a compact and powerful development board built around the RP2350 chip from Raspberry Pi and equipped with 16MB flash and 8MB PSRAM. It follows the updated Pro Micro design and includes a USB-C connector, Qwiic connector, WS2812B RGB LED, Boot and Reset buttons, resettable PTC fuse, and both PTH and castellated solder pads. Last week, besides the Raspberry Pi Pico 2, we wrote about more boards with the Raspberry Pi RP2350, like the XIAO RP2350, Solder Party’s RP2350 Stamp, and Cytron MOTION 2350 Pro. Feel free to check them out if you are interested in these boards. SparkFun Pro Micro – RP2350 specification Microcontroller – Raspberry Pi RP2350A MCU CPU Dual-core Arm Cortex-M33 @150MHz with Arm Trustzone for secure boot Dual-core 32-bit Hazard3 RISC-V @ 150MHz Up to two cores can be used at the same time Memory – 520 KB on-chip SRAM […]

MILK-V Jupiter review – A RISC-V mini-ITX motherboard and PC tested with Ubuntu-based Bianbu OS

In this review or preview of the the Shenzhen Milk-V Jupiter RISC-V mini-ITX motherboard, I’ll assemble the motherboard into a mini-ITX chassis, before installing the Ubuntu 23.10 Mantic-based Bianbu OS optimized for RISC-V platforms, and testing the device to see how much progress has been done on RISC-V since I tested the StarFive VisionFive 2 SBC with Debian 12 about 18 months ago. In the first part of the review, we checked out the Radxa ROCK 5 ITX (Rockchip RK3588 Arm) and Jupiter (SpacemIT K1 RISC-V) mini-ITX motherboards with specifications and unboxing, and the Auriga 6-Bay NAS mini-ITX chassis used in this review. I planned to start with the Radxa ROCK 5 ITX, but due to logistics and technical issues, I went ahead testing the RISC-V motherboard first. Installing Bianbu OS to the Jupiter RISC-V motherboard The board does not come with storage, so no operating system is installed. So […]

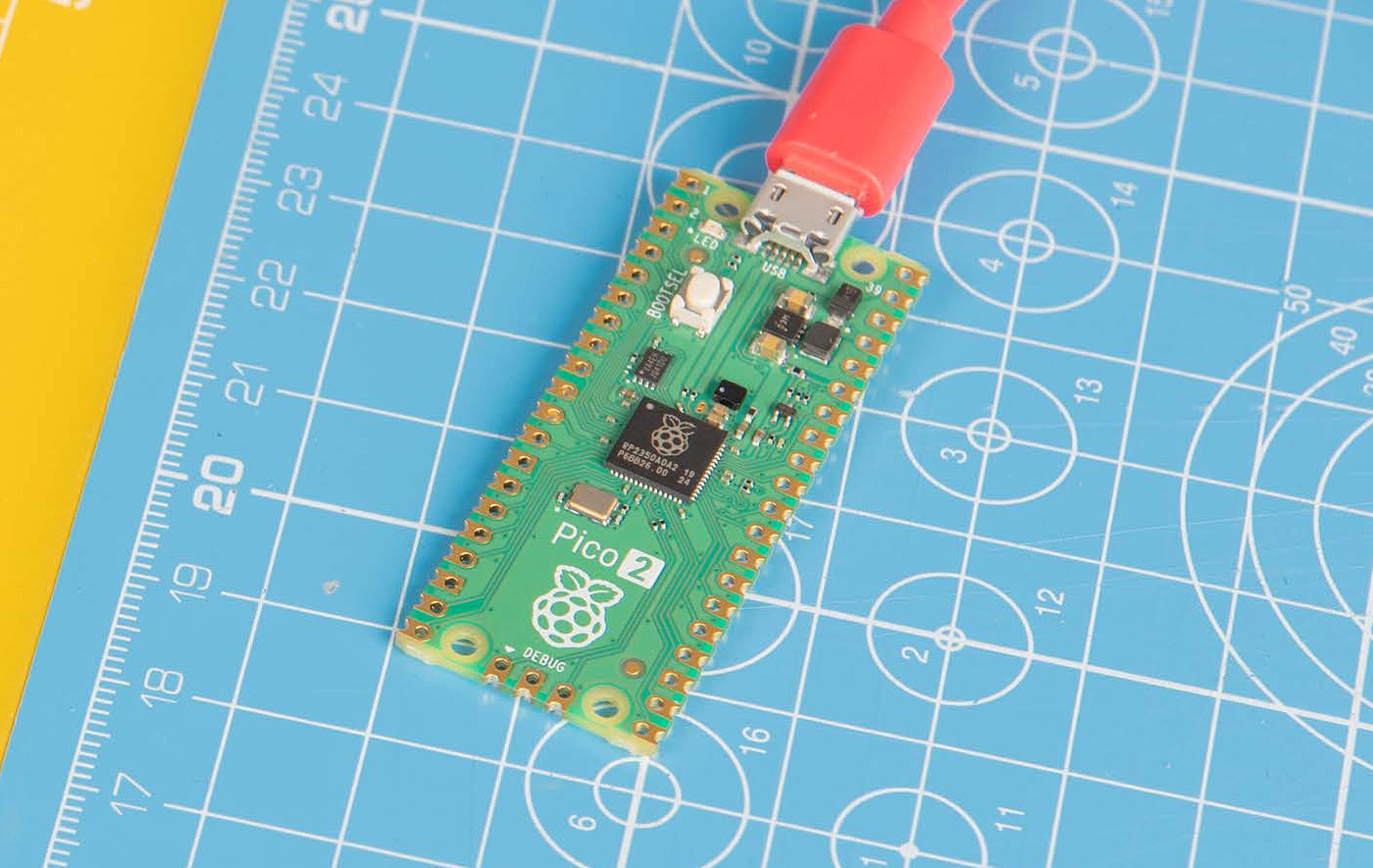

$5 Raspberry Pi Pico 2 launched with Raspberry Pi RP2350 dual-core RISC-V or Arm Cortex-M33 microcontroller

The Raspberry Pi Pico 2 is an MCU development board based on the new Raspberry Pi RP2350 dual-core RISC-V or dual-core Cortex-M33 microcontroller with 520 KB on-chip SRAM, a 4MB flash, a micro USB port for power and programming and the same GPIO headers as the Raspberry Pi Pico board with an RP2040 dual-core Cortex-M0+ microcontroller with 264KB SRAM. The RP2350 embeds both an open-source Hazard3 RISC-V dual-core CPU and a dual-core Cortex-M33, but only one cluster can be used at a given time. Apart from the faster MCU cores and higher SRAM capacity, the RP2350 is about the same as the RP2040, albeit it also adds one extra PIO block bringing the total to three. One important new feature is built-in security when using Arm Cortex-M33 cores with Trustzone and other security features. Raspberry Pi RP2350 microcontroller Let’s have a closer look at the RP2350 microcontroller, before checking out […]

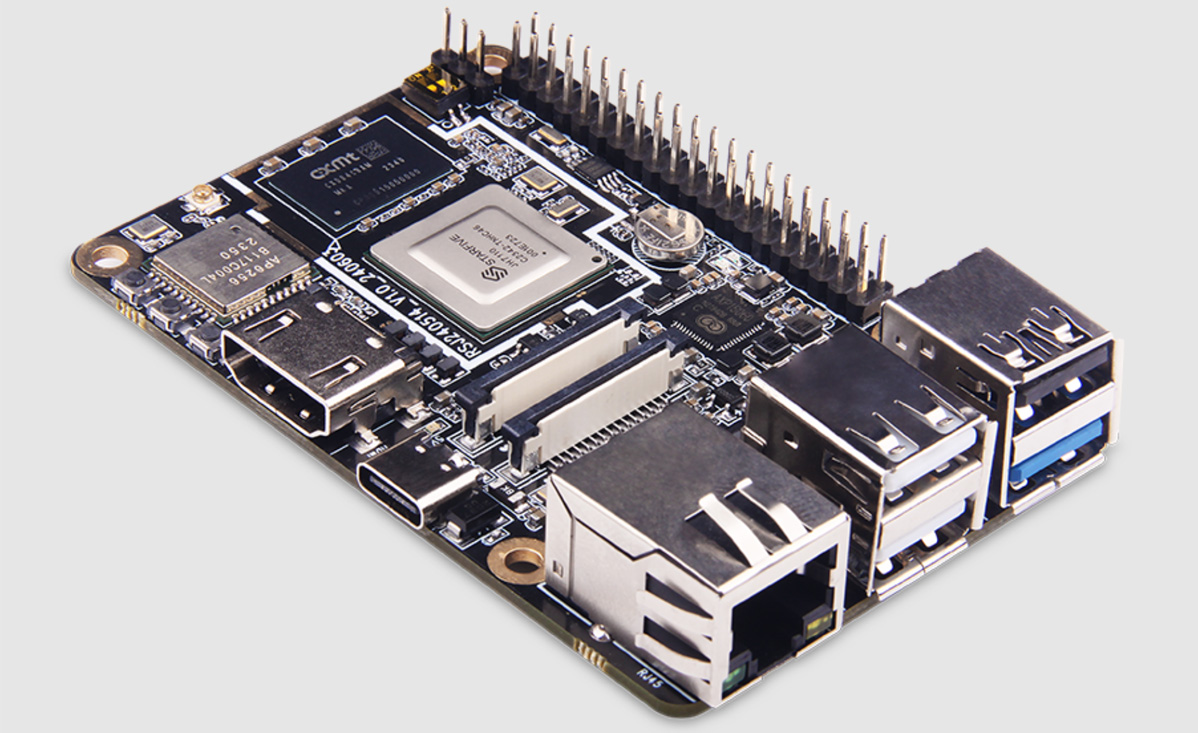

Geniatech XPI-7110 – A Raspberry Pi-sized RISC-V SBC based on StarFive JH7110 processor

Geniatech XPI-7110 is a RISC-V single-board computer (SBC) built on StarFive JH7110 with a form factor similar to that of a Raspberry Pi 3 and equipped with up to 8GB of RAM, 256GB of eMMC storage. It comes with various I/O options including USB ports, HDMI 2.0, GbE Ethernet, Wi-Fi/BT, GPIO, camera, display, and much more. The company also mentions that the board will be available in both commercial and industrial variants and will include a 10+ year lifecycle The new Geniatech board is very similar to the Milk-V Mars that we wrote about a few months ago. Additionally, we have written about PineTab-V, Pine64 Star64 SBC, and Milk-V Meles SBC all of which are built around the StarFive JH7110 or T-Head TH1520 RISC-V SoC, feel free to check those out if you are interested in the topic. Geniatech XPI-7110 SBC specifications: SoC – StarFive JH7110 CPU – Quad-core RISC-V processor […]

ESP32-P4-Function-EV-Board development board launched for $55 with 7-inch display and camera module

Espressif Systems “ESP32-P4-Function-EV-Board” – the official ESP32-P4 development board – is now available in limited quantities on Espressif’s AliExpress store for $55.44, and some other AliExpress stores at a premium as part of a kit with a 7-inch touchscreen display and a 2MP camera module. First unveiled in January 2023, the ESP32-P4 is the first general-purpose RISC-V microcontroller from Espressif Systems without any wireless connectivity. It’s a high-end microcontroller with two RISC-V cores clocked at 400 MHz, vector instructions for AI acceleration, a 2D graphics accelerator for smooth graphical user interfaces, and H.264 video encoding support. There’s been some buzz about it in recent months, and finally, it’s now possible to purchase an ESP32-P4 board for evaluation and software development. ESP32-P4-Function-EV-Board development board specifications: Microcontroller – Espressif Systems ESP32-P4 CPU Dual-core RISC-V HP (High-performance) CPU @ up to 400 MHz with AI instructions extension and single-precision FPU, 768KB of on-chip […]

Building a workstation with Radxa ROCK 5 ITX (Arm) or Milk-V Jupiter (RISC-V) mini-ITX motherboard – Part 1: The hardware

Radxa ROCK 5 ITX is a mini-ITX motherboard powered by a Rockchip RK3588 octa-core Cortex-A76/A55 processor, and the Shenzhen Milk-V Jupiter is another mini-ITX motherboard, but based on SpacemIT K1 octa-core 64-bit RISC-V processor instead. When Radxa contacted me about reviewing those, I thought it would be interesting to review a complete kit with a mini-ITX case since I had never built this type of system myself. Yesterday, I was surprised to receive two large packages and thought maybe a company sent me a 3D printer or laser engraver kit, but instead, I got one package with the two Arm and RISC-V mini-ITX motherboards and another with a mini-ITX NAS enclosure with 6x SATA bays. Radxa ROCK 5 ITX unboxing Let’s look at the ROCK 5 ITX motherboard and accessories first. The motherboard ships with a rear panel and two screws for the M.2 module. The motherboard features the Rorkchip […]

Linux 6.10 Release – Notable changes, Arm, RISC-V, and MIPS architectures

Linux Torvalds has announced the release of Linux 6.10 on LKML: So the final week was perhaps not quote as quiet as the preceding ones, which I don’t love – but it also wasn’t noisy enough to warrant an extra rc. And much of the noise this last week was bcachefs again (with netfs a close second), so it was all pretty compartmentalized. In fact, about a third of the patch for the last week was filesystem-related (there were also some btrfs latency fixes and other noise), which is unusual, but none of it looks particularly scary. Another third was drivers, and the rest is “random”. Anyway, this obviously means that the merge window for 6.11 opens up tomorrow. Let’s see how that goes, with much of Europe probably making ready for summer vacation. And the shortlog below is – as always – just the last week, not some kind […]