FreeRTOS is one of the most popular operating systems found in embedded systems, and RISC-V open architecture is getting more and more traction, so it should come as no surprise that Amazon has now added RISC-V to their recently acquired FreeRTOS kernel. Jeff Barr, Chief Evangelist for AWS, explains both 32-bit and 64-bit RISC-V cores are supported, and several RISC-V boards are already supported out of the box: The kernel supports the RISC-V I profile (RV32I and RV64I) and can be extended to support any RISC-V microcontroller. It includes preconfigured examples for the OpenISA VEGAboard, QEMU emulator for SiFive’s HiFive board, and Antmicro’s Renode emulator for the Microchip M2GL025 Creative Board. There’s no a lot of information on Amazon announcement post, but FreeRTOS website has plenty of resources to help you get started with RISC-V. The page also lists some of the key features of the RISC-V port: Supports machine […]

Linux 5.0 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just released Linux 5.0: Ok, so the last week of the 5.0 release wasn’t entirely quiet, but it’s a lot smaller than rc8 was, and on the whole I’m happy that I delayed a week and did an rc8. It turns out that the actual patch that I talked about in the rc8 release wasn’t the worrisome bug I had thought: yes, we had an uninitialized variable, but the reason we hadn’t immediately noticed it due to a warning was that the way gcc works, the compiler had basically initialized it for us to the right value. So the same thing that caused not the lack of warning, also effectively meant that the fix was a no-op in practice. But hey, we had other bug fixes come in that actually did matter, and the uninitialized variable _could_ have been a problem with another compiler. Regardless – all […]

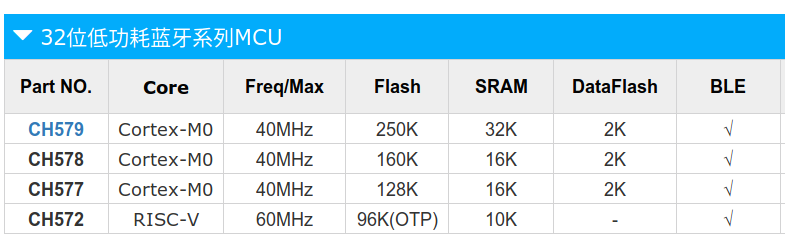

WCH CH572 is a RISC-V MCU with Bluetooth LE Connectivity

Jiangsu Qinheng Co., Ltd, better known as WCH, is famous for their USB to TTL chip such as CH340, but the company also offers various wireless MCUs, including some Arm Cortex-M0 based Bluetooth / Zigbee parts such as CH579. But today, I was informed a new Bluetooth MCU showed up on WCH website: CH572 with a RISC-V MCU core @ 60 MHz. We have limited information about the MCU, but here’s what we need so far about CH572 specifications: Core – RISC-V MCU @ up to 60 MHz System Memory – 10K SRAM Storage – 96KB OTP (One-Time Programming) flash Connectivity – Bluetooth LE USB – 1x USB host, 1x USB device Other Peripherals and I/Os 11-ch 12-bit ADC 3x 26-bit timers 11x PWM 2x UART, 1x SPI 23x GPIOs RTC and Watchdog Supply Voltages – 3.3V/2.5V Package – QFN28 The main downside is that’s an OTP flash, so you’d […]

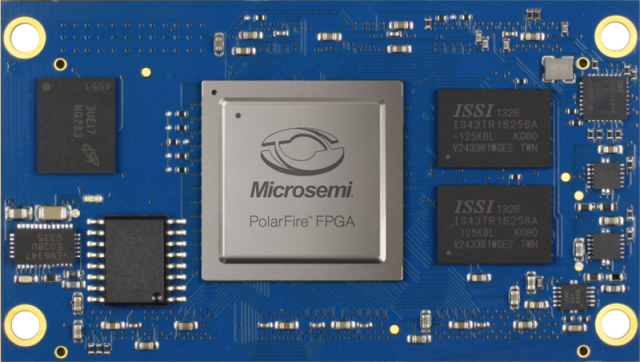

ARIES M100PF PolarFire FPGA System-on-Module Targets Industrial Applications, RISC-V Development

MicroSemi unveiled PolarFire RISC-V FPGA SoC at the end of last year, bringing an alternative to Xilinx Zynq (Arm Cortex-A9 + FPGA) and UltraScale+ (Cortex A53 + FPGA) SoCs. The system-on-chip is expected to be mass produced later in 2019, so development is done on HiFive Unleashed RISC-V board and its FPGA expansion board. In the meantime, MicroSemi PolarFire FPGAs (without RISC-V hard core) are available now, and ARIES Embedded planning to showcase what they claim is the first PolarFire FPGA system-on-module at Embedded World 2019 with their M100PF SoM targeting industrial applications. ARIES Embedded M100PF key features and specifications: A choice of 3 PolarFire FPGAs MPF100T – 109KLE, 336 Math Blocks (18x18MACC) MPF200T – 192KLE, 588 Math Blocks (18x18MACC) MPF300T – 300KLE, 924 Math Blocks (18x18MACC) System Memory – 512 MiB / 1 GiB / 2 GiB DDR3 RAM Storage – 256 MiB configuration device, 4 GiB eMMC flash […]

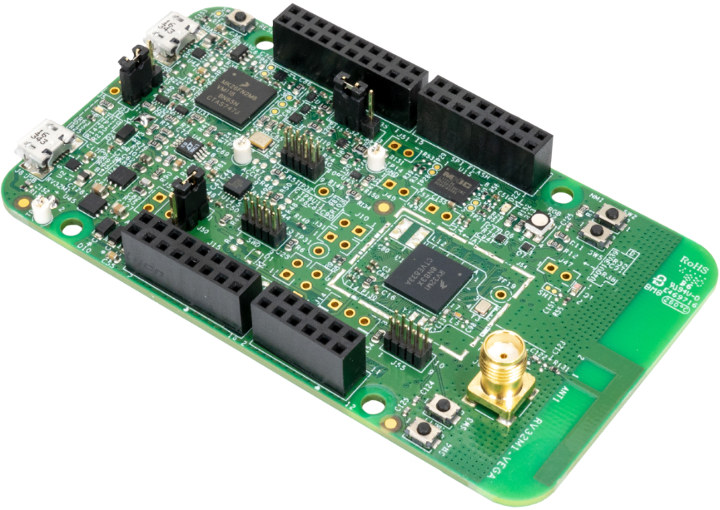

OpenISA VEGAboard Combines RISC-V and ARM Cortex-M Cores

OpenISA has launched an Arduino compatible RISC-V development called VEGAboard that features RV32M1 wireless microcontroller with a RISC-V RI5CY core, a RISC-V ZERO-RISCY core as well as Arm Cortex-M4F and Cortex-M0 cores, and a radio operating in the 2.36 GHz to 2.48 GHz range. An external NXP Kinetis K26 Arm Cortex-M4 MCU is added to the board for OpenSDA (Open-Standard Serial and Debug Adapter) debugging over a single USB cable. The board was offered for free, I’m just not sure when, but they are already out of stock. Hopefully, they’ll start selling the board soon enough. VEGAboard (RM32M1-VEGA) board key features and specifications: Ultra-low-power RV32M1 Wireless MCU supporting BLE, Generic FSK, and IEEE Std 802.15.4 (Thread) platforms IEEE Std. 802.15.4-2006 compliant transceiver supporting 250 kbps O-QPSK data in 5.0 MHz channels, and full spread-spectrum encoding and decoding Fully compliant Bluetooth v4.2 Low Energy (BLE) Reference design area with small-footprint, low-cost […]

FOSDEM 2019 Open Source Developers Meeting Schedule

FOSDEM – which stands for Free and Open Source Software Developers’ European Meeting – is a free-to-participate event where developers meet on the first week-end of February to discuss open source software & hardware projects. FOSDEM 2019 will take place on February 2 & 3, and the schedule has already been published with 671 speakers scheduled to speak in 711 events themselves sorted in 62 tracks. Like every year, I’ll create a virtual schedule based on some of the sessions most relevant to this blog in tracks such as open hardware, open media, RISC-V, and hardware enablement tracks. February 2 10:30 – 10:55 – VkRunner: a Vulkan shader test tool by Neil Roberts A presentation of VkRunner which is a tool to help test the compiler in your Vulkan driver using simple high-level scripts. Perhaps the largest part of developing a modern graphics driver revolves around getting the compiler to […]

Fomu FPGA board fits inside a USB port, Supports Python, RISC-V Softcore

Sutajio Ko-usagi launched Tomu, a tiny open source hardware USB board that fits inside a USB port at the very beginning of this year. The company is back with a similarly shaped board, but instead of featuring a Silicon Labs EFM32 Arm Cortex-M0+ microcontroller, Fomu is equipped with a Lattice ICE40 UltraPlus FPGA. Fomu specifications: FPGA – Lattice ICE40UP5K FPGA with 5280 logic cells System Memory – 128 kB RAM for a soft CPU Storage – 1 or 2 MB SPI flash Clock – 48 MHz crystal oscillator USB – 1x USB 2.0 FS (12 Mbps) port Misc – 4x buttons, 1x RGB LED The default Fomu firmware exposes a USB bootloader running a RISC-V softcore, and the platform is powerful enough to run a port of Python. It’s also possible to experiment with LM32 and OpenRISC softcores on the platform. Using the board is pretty straightforward as just you […]

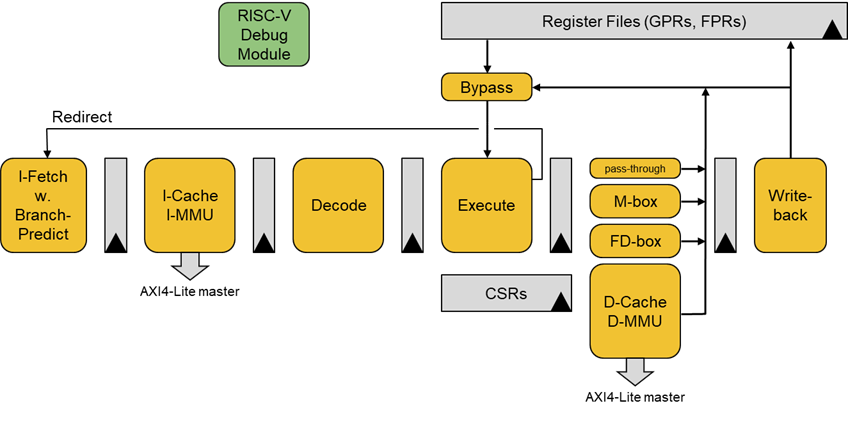

Bluespec Flute is a 5-Stage Open Source RISC-V Processor

Bluespec is a US company that provides RISC-V processors and development tools that “speed integration, debugging and verification of embedded systems”. Their first RISC-V release was the Piccolo 3-stage in-order processor targeting low end embedded systems and IoT applications. The company has now announced Bluespec Flute a 5-stage in-order open source RISC-V processor with the release of a synthesizable Verilog for a bare metal RV32IMA core and a supervisor level RV64IMA core. Bluespec Flute key features: RV32IMU with ‘M’ extension (integer multiply/divide) RV64IMASU with ‘A’ extension (atomic memory ops) and ‘M’ extension (integer multiply/divide) AXI4-Lite interface 5-stage pipeline 100 MHz (Xilinx UltraScale) < 5000 LUTs (Xilinx UltraScale) 4KB Instruction & Data caches Hardware multiply-divide RISC-V Debug Module You’ll find the source code in BSV (Bluespec SystemVerilog) and instructions to get started in Github. Bluespec Flute core has been tested in Xilinx UltraScale/UltraScale+ boards so far. In the future, the company […]