I may have just written about Linaro Connect San Diego 2019 schedule, but there’s another interesting event that will also take place this fall: the Embedded Linux Conference Europe on October 28 -30, 2019 in Lyon, France. The full schedule was also published by the Linux Foundation a few days ago, so I’ll create a virtual schedule to see what interesting topics will be addressed during the 3-day event. Monday, October 28 11:30 – 12:05 – Debian and Yocto Project-Based Long-Term Maintenance Approaches for Embedded Products by Kazuhiro Hayashi, Toshiba & Jan Kiszka, Siemens AG In industrial products, 10+ years maintenance is required, including security fixes, reproducible builds, and continuous system updates. Selecting appropriate base systems and tools is necessary for efficient product development. Debian has been applied to industrial products because of its stability, long-term supports, and powerful tools for packages development. The CIP Project, which provides scalable and […]

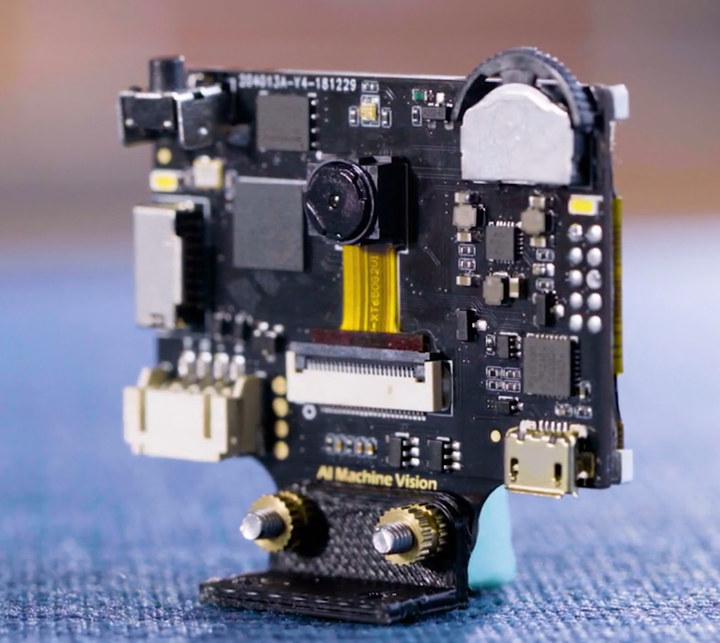

HuskyLens AI Camera & Display Board is Powered by Kendryte RISC-V Processor (Crowdfunding)

A couple of years ago, I reviewed JeVois-A33 computer vision camera powered by Allwinner A33 quad-core Cortex-A7 processor running Linux. The tiny camera would implement easy-to-use software for machine vision with features such as object detection, eye tracking, QR code and ArUco marker detection, and so on. The camera could handle the tasks at hand, but since it relied on purely software computer vision, there were lag for some of the demo applications including 500ms for single object detection, and up to 3 seconds for YOLO test with multiple object types using deep learning algorithms. That’s a bit slow for robotics project, and software solutions usually consume more than hardware accelerated ones. Since then, we’ve started to see low-cost SoC and hardware with dedicated hardware AI accelerators, and one of those is Kendryte K210 dual-core RISC-V processor with a built-in KPU Convolutional Neural Network (CNN) hardware accelerator and APU audio […]

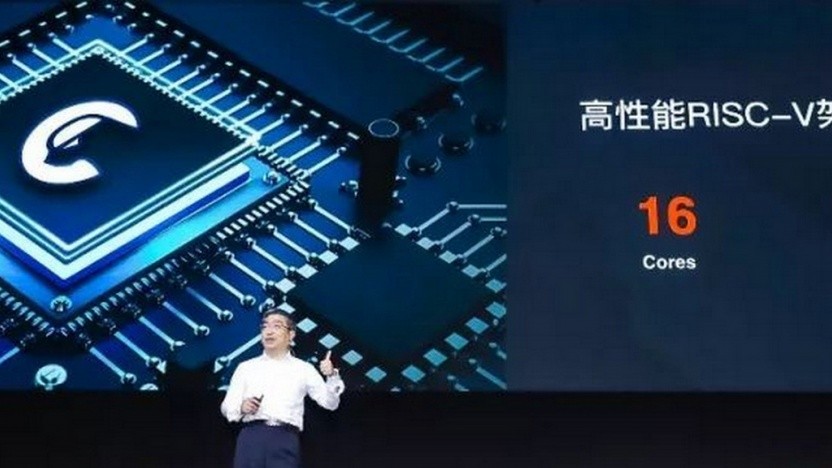

Alibaba Unveils XuanTie 910 16-core RISC-V Processor

When Pingtou Ge (Brother Pingtou) Semiconductor Co. was founded by Alibaba in September 2018, the vision was to create groundbreaking chips for production. The company had once been Zhongtianwei, a chip company, which was acquired by Alibaba in April 2018 along with team Aha. On July 25, 2019, it was announced that Brother Pingtou had released the XuanTie 910 (Black Iron 910) 16-Core RISC-V Processor. The company has reported that the processor will be integrated into high-performance end to end 5G chips, AI, and autonomous driving applications. There are conflicting reports that the processor is also known as T-Head, although its name means Black Iron. There has been no firm release date or price as of yet. Open-source technologies are being adopted on a regular basis in China, and the XuanTie 910 is being offered to developers with encouragement to use Berkeley-based open-source ISA with very few intellectual property restrictions. […]

Linux 5.2 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds announced the release of Linux 5.2 last Sunday: So I was somewhat pre-disposed towards making an rc8, simply because of my travels and being entirely off the internet for a few days last week, and with spotty internet for a few days before that [*]. But there really doesn’t seem to be any reason for another rc, since it’s been very quiet. Yes, I had a few pull requests since rc7, but they were all small, and I had many more that are for the upcoming merge window. Part of it may be due to the July 4th week, of course, but whatever – I’ll take the quiet week as a good sign. So despite a fairly late core revert, I don’t see any real reason for another week of rc, and so we have a v5.2 with the normal release timing. There’s no particular area that stands […]

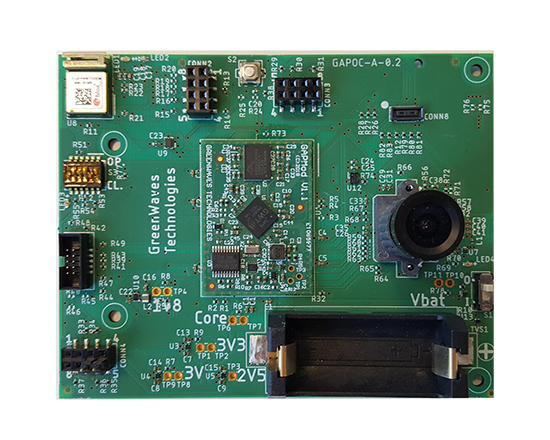

GAPPoc AI development boards based on the GAP8 RISC-V Chip

GreenWaves has developed a development board based on the GAP8 chip which can be evaluated from a GAPuino board, a generic board that can run off a low power external power source or USB and is compatible with the Arduino ecosystem. Recently the company moved beyond the generic board to the GAPPoc, platform which stands for GAP8 Proof of Concept. The GAPPoc is focused on a class of applications which can be embedded on a single board and able to carry hardware such as crystal or external memory, sensors, a radio fit, and a battery. The board will be geared towards a set of low power functions for a particular class of applications. This is a family of boards designed to increase the range of abilities in edge Artificial Intelligence. At this time there is only a single board with a platform to enhance AI, targeting Computer Vision in the […]

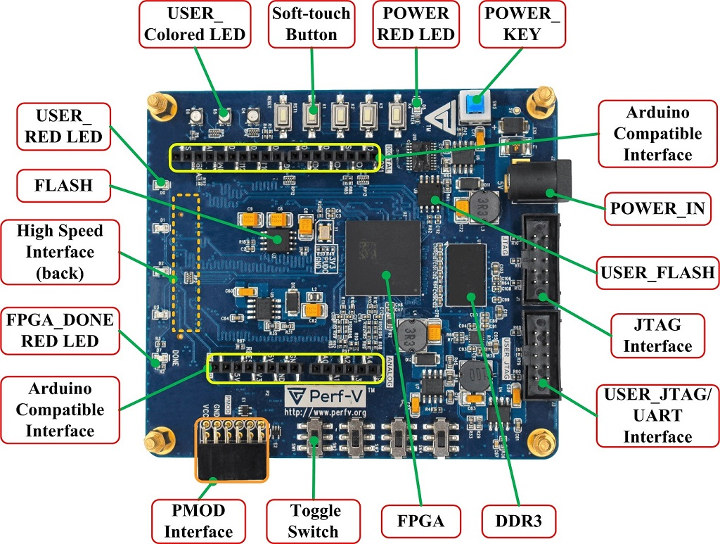

Perf-V is another FPGA based RISC-V Development Board

There are already some RISC-V development boards with silicon featuring RISC-V instruction set such as SiFive’s HiFive1 or Kendryte KD233 board. But beauty of RISC-V is that you can customize the instructions set, and if that’s your goal, an FPGA board provides the flexibility you need. While in theory you could use pretty much any FPGA board with enough logic elements, it may help to get started with boards that are designed for this purpose since the company already ported a RISC-V core to their platform and you can start from there. We’ve already covered a few of those including LicheeTang and Fomu boards, as well as ARIES M100PF PolarFire FPGA system-on-module. Today, I’ve come across another of those RISC-V FPGA board. Meet Perf-V board with the following specifications: FPGA – Xilinx Artix-7 XC7A35T-1FTG256C with 33280 Logic Cells, 90 DSP, 41600 CLBs, 1800 Kbit Block RAM, and 5 CMTs; Optional […]

Kazan Software Vulkan Implementation is Optimized for RISC-V Processors

More and more people want to run fully open source systems due to philosophical, privacy and security concerns, but on embedded systems with a GPU is often hard to achieve due to closed-source binary blobs. Projects such as Freedreno and Etnaviv have freed Qualcomm Adreno and Vivante GPUs, but it takes years to implement workable reverse-engineered open source GPU drivers. One solution to get an open source graphics driver from the get-go is to implement the rendering into the CPU, but the problem is that it’s usually really slow, and GPU’s are much faster thanks to their ability to quickly handle parallel tasks. Kazan is a software-rendering Vulkan implementation, but it may be eventually end up as a low-end soft-GPU in some RISC-V SoCs thanks to specific instructions. I found out about Kazan through the Libre RISC-V M-Class chip project that aims to be a low-power, mobile-class, 64-bit quad-core SoC […]

More Investments into RISC-V – Qualcomm Backs SiFive, OpenHW Group Created

Some may doubt RISC-V will ever challenge Arm at least in some markets, but the industry is investing in solutions based on the royalty-free open source ISA, with this week SiFive securing $65.4 Million from various investors including Qualcomm Ventures LLC, and the announcement of the launch of the OpenHW Group, a new not-for-profit global organization aims to boost the adoption of open-source processors currently backed by 13 companies, and aiming to reach 25 sponsors by year’s end. SiFive gets more interest from investors Here’s the main part of the announcement of SiFive’s new series D funding: SiFive, Inc., the leading provider of commercial RISC-V processor IP and silicon solutions, today announced it raised $65.4 million in a Series D round led by existing investors Sutter Hill Ventures, Chengwei Capital, Spark Capital, Osage University Partners and Huami, alongside new investor Qualcomm Ventures LLC. This Series D round brings the total […]