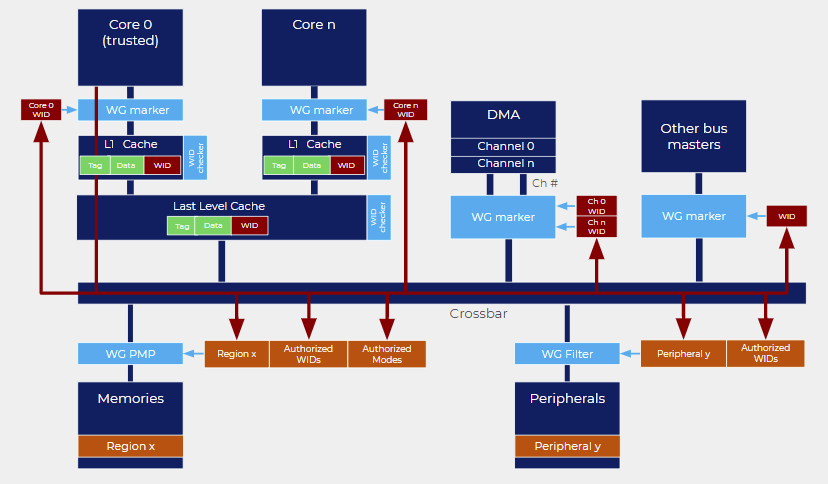

Most Arm processors and Armv8-M microcontrollers support Arm TrustZone security with hardware-enforced isolation built into the CPU. But so far, I had not read anything about equivalent solutions for RISC-V processors. It turns out Hex-Five’s MultiZone security is one of the RISC-V hardware-security providing an answer to Arm TrustZone, and besides checking out the presentation slides, you can also watch the video filmed at RISC-V Workshop Taiwan last March. But what brought me to write about RISC-V security is SiFive announcement for their Shield open security platform for RISC-V processors SiFive Shield Overview SiFive Shield is an open, scalable security platform designed for RISC-V processors. It supports root-of-trust, customizations, and offers per-memory protected memory regions and multi-core privilege modes. Combined with SiFive WorldGuard, SiFive Shield enables greater isolation. SiFive WorldGuard Isolation SiFive WorldGuard is a fine-grain security model for isolated code execution and data protection. It offers core-driven and process-id […]

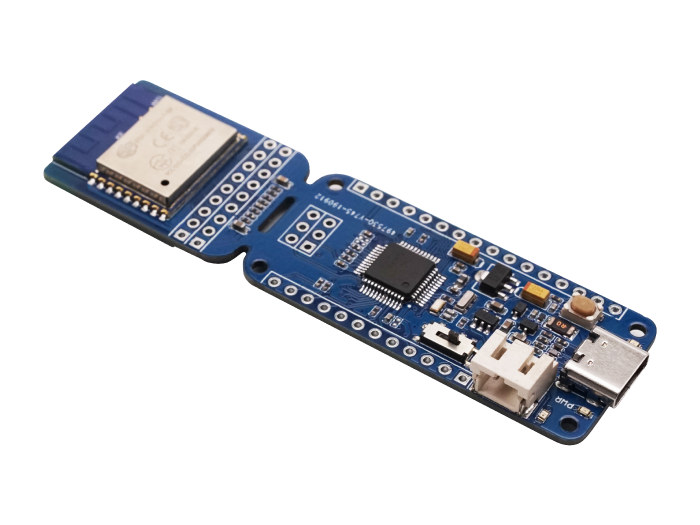

Wio Lite RISC-V WiFi Board with ESP8266 Module Launches for $6.9

Released this summer, GigaDevice GD32V generated a lot of buzz, as a cheap general-purpose 32-bit RISC-V MCU, and soon after the $5 Longan Nano development board with LCD display and enclosure was launched to the market. However, many applications benefit or require some network connectivity with WiFi. Espressif Systems is a founding member of the RISC-V Foundation, so RISC-V WiSoCs (Wireless SoCs) are coming, but AFAIK none of those are available yet. In the meantime, Seeed Studio has launched Wio Lite RISC-V board which brings WiFi connectivity to GD32V MCU through an ESP8266 WiFi module. Wio Lite specifications: MCU – Gigadevice GD32VF103CBT6 RISC-V (rv32imac) microcontroller @ 108 MHz with 128KB Flash, 32KB SRAM Wireless Module – ESP8266 WiFi Wio Core with 802.11b/g/n/ WiFi 4 connectivity Storage – MicroSD card slot USB – 1x USB Type-C port for power and programming Expansion – I/O headers for GD32 MCU, I/O header for […]

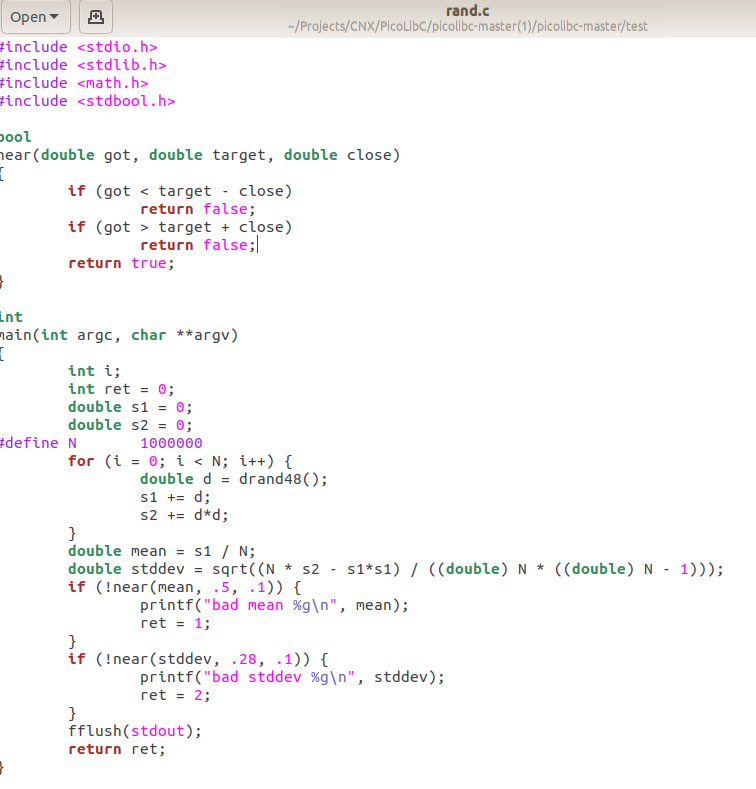

PicoLibC is a Lightweight C library for Embedded Systems

Well-known developer, Keith Packard has recently announced the launch of “picolibc” through his blog. Picolibc is a C Library for embedded systems which is suitable for small micro-controllers, and this standard C library API’s allows to run even in low memory (RAM) devices. This is an upgraded version of “newlib-nano” with few interesting changes which includes replacement of “stdio” lib with ATMEL-specific printf code adopted from avrlibc. As part of this library, Keith also launched picocrt, which is responsible for initializing memory and invoking various constructors before calling its own C program, the main function. Features picolibc is a revised version of newlibc, without full-fledged stdio lib and uses lightweight stdio lib from avrlibc, which is more suitable to low memory embedded devices. Meson build-system eases the build process of picolibc source tree for various target platform and hardware. Updated the math test suite to use Glibc as a reference […]

Linux 5.3 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.3: So we’ve had a fairly quiet last week, but I think it was good that we ended up having that extra week and the final rc8. Even if the reason for that extra week was my travel schedule rather than any pending issues, we ended up having a few good fixes come in, including some for some bad btrfs behavior. Yeah, there’s some unnecessary noise in there too (like the speling fixes), but we also had several last-minute reverts for things that caused issues. One _particularly_ last-minute revert is the top-most commit (ignoring the version change itself) done just before the release, and while it’s very annoying, it’s perhaps also instructive. What’s instructive about it is that I reverted a commit that wasn’t actually buggy. In fact, it was doing exactly what it set out to do, and did it […]

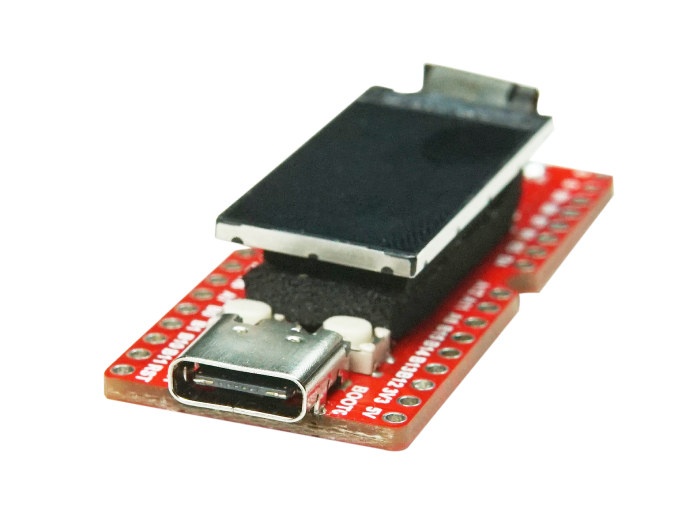

$5 Longan Nano GD32V RISC-V Development Board Comes with LCD Display and Enclosure

There’s been some exciting news about RISC-V microcontrollers recently with Gigadevice announcing GD32V, one of the first RISC-V general-purpose microcontrollers, which outperforms its Arm Cortex-M3 equivalent in terms of performance and power consumption. The company also announced some development boards, but they are not quite that easy to purchase being listed on Tmall website in China. The good news is that Sipeed has introduced Longan Nano development board powered by GD32VF103CBT6 microcontroller, and it’s up for sale on Seeed Studio for $4.9. Longan Nano board specifications: MCU – Gigadevice GD32VF103CBT6 32-bit RISC-V (rv32imac) microcontroller @ 108 MHz with 128KB Flash, 32KB SRAM Storage – MicroSD card slot Display – 0.96″ 160×80 IPS RGB LCD connected via SPI USB – 1x USB Type-C port for power and programming Expansion – 2x 16 through holes (2.54mm pitch) exposing 3x USART, 2x I2C, 3x SPI, 2x I2S, 2x CAN, 1x USBFS (OTG), 2x […]

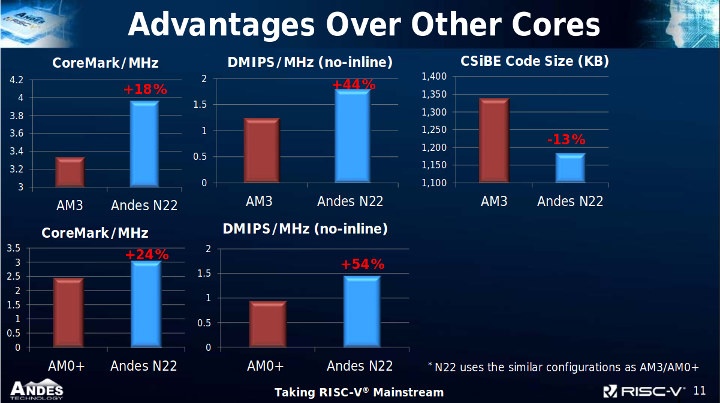

AndesCore N22 RISC-V Core Supports RV32IMAC or RV32EMAC Instruction Sets

We covered Gigadevice GD32V general-purpose microcontroller with a RISC-V “Bumblebee” core last week, and I was informed that Andes Technology had recently introduced AndesCore N22 RISC-V “Bumblebee” IP core capable of supporting either RV32IMAC or RV32EMAC instruction sets. A web search did not reveal any specific information about what “Bumblebee” RISC-V cores are exactly, or maybe it’s in reference that many can be coupled in parallel. But that’s just a small detail, let’s check out in some details what AndesCore N22 core has to offer. The RISC-V core is designed for entry-level MCUs found in IoT devices and wearables, and is capable of deeply embedded protocol processing for I/O control, storage, networking, AI and AR/VR. Highlights of AndesCore N22: AndeStar V5 (RV32IMAC) / V5e (RV32EMAC) Instruction Set Architecture (ISA), compliant to RISC-V technology plus Andes extensions architectured for performance and functionality enhancements 32-bit, 2-stage pipeline CPU architecture 16/32-bit mixable instruction […]

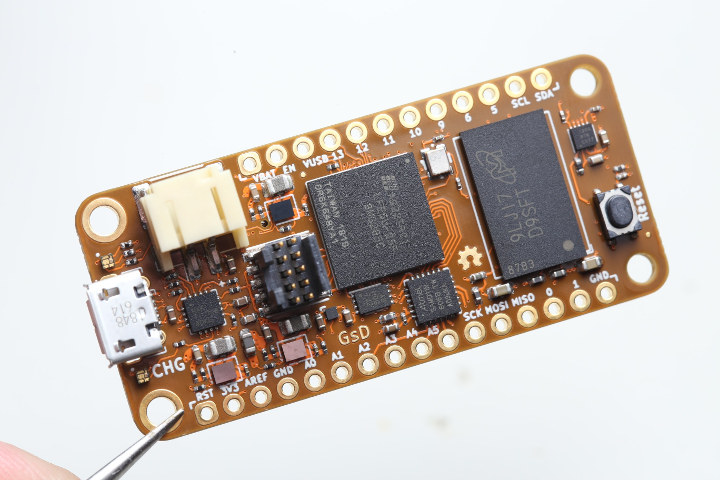

OrangeCrab is an Open Source Hardware, Feather-Compatible Lattice ECP5 FPGA Board

Lattice ECP5 FPGA powered OrangeCrab is the work of Greg Davill who designed the Adafruit Feather-compatible board in KiCAD, crowdsourced schematics/PCB checking and published his progress on Twitter, and published the files of the open source hardware board on Github. OrangeCrab board hardware specifications: FPGA – Lattice ECP5 25/45/85 variants System Memory – Up to 8Gbit DDR3 Memory (x16) Storage – 128Mbit QSPI FLASH Memory (Bitstream + User storage), 4-bit MicroSD socket USB – Micro USB connector, full-speed direct USB connection to FPGA Programming – 10-pin FPGA programming header Expansion – I/O’s broken out via 30 through holes: GPIO, SPI, I2C, Analog, … 7x diff pairs, 1x single ended only Misc – Reset Button, charge LED (Green: external power, Yellow: when charging, No color: when running off battery), 48MHz Oscillator Power Supply – 5V via USB port, battery header for LiPo battery + battery charger chip Dimensions – Adafruit Feather […]

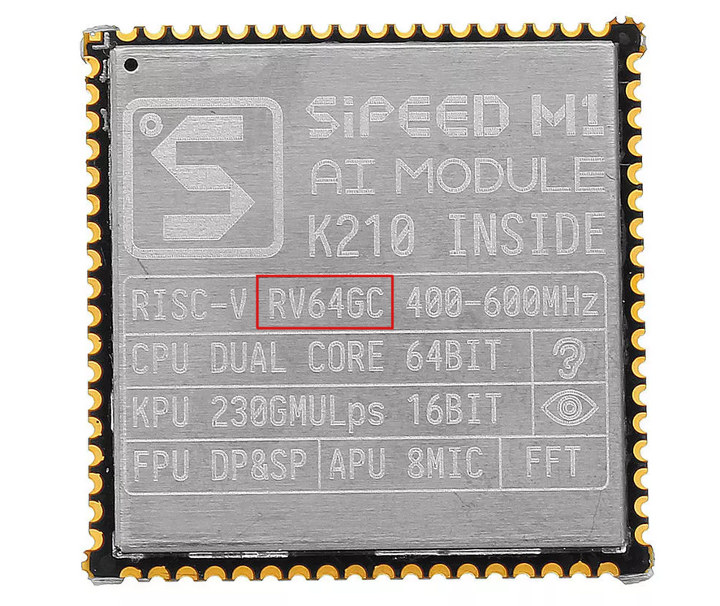

RISC-V Bases and Extensions Explained

The other day we reported about GigaDevice GD32V general-purpose 32-bit RISC-V microcontroller, and one of the commenters asked whether it was rv32imac or rv32emac, and it turned out to be the former. In most cases, silicon vendors report whether they are using 32-bit, 64-bit, or the upcoming 128-bit RISC-V processors, but rarely go into details, so I asked why it mattered and got the following answer: RISC-V is a federation of ISA extensions — from the baseline rv{32|64|128}I, to an arbitrary combination of a handful of extensions. There are combinations which are dubbed ‘application-processor level’ (the G subset), but implementations can and often are not G-compliant, which is naturally the case with MCUs. Difference between rv32i and rv32e is 32-strong vs 16-strong GPR file, respectively. In the case of GD32VF103, rv32imac stands for a ‘full-size GPR file, integer mul/div, atomics, compressed (16bit) ISA’ set. What is missing from ‘application-processor level’ […]