We are seeing more and more RISC-V microcontrollers and processors hitting the market, but so far they all lacked a GPU for 3D graphics acceleration. Think Silicon, the make of NEMA GPU for IoT and wearables, has now announced it will demonstrate NEOX|V GPU, the first RISC-V ISA based 3D, at the RISC-V Summit at the San Jose Convention Center, on December 10-12, in San Jose, California. NEOX|V key features: Parallel multi-core and multi-threaded architecture based on the RISC-V64GC ISA instruction set with adaptive NoC (Networks-on-Chip) Configurable from 4 to 64 cores Variety of cache sizes and thread counts organized in 1 to 16 cluster elements Variety of cluster/core configurations with compute power ranging from 12.8 to 409.6 GFLOPS at 800 MHz Support for FP16, FP32, and FP64 plus SIMD instructions Beside 3D graphics, the RISC-V GPU can also be used for machine learning, vision/video processing, and open GPGPU compute […]

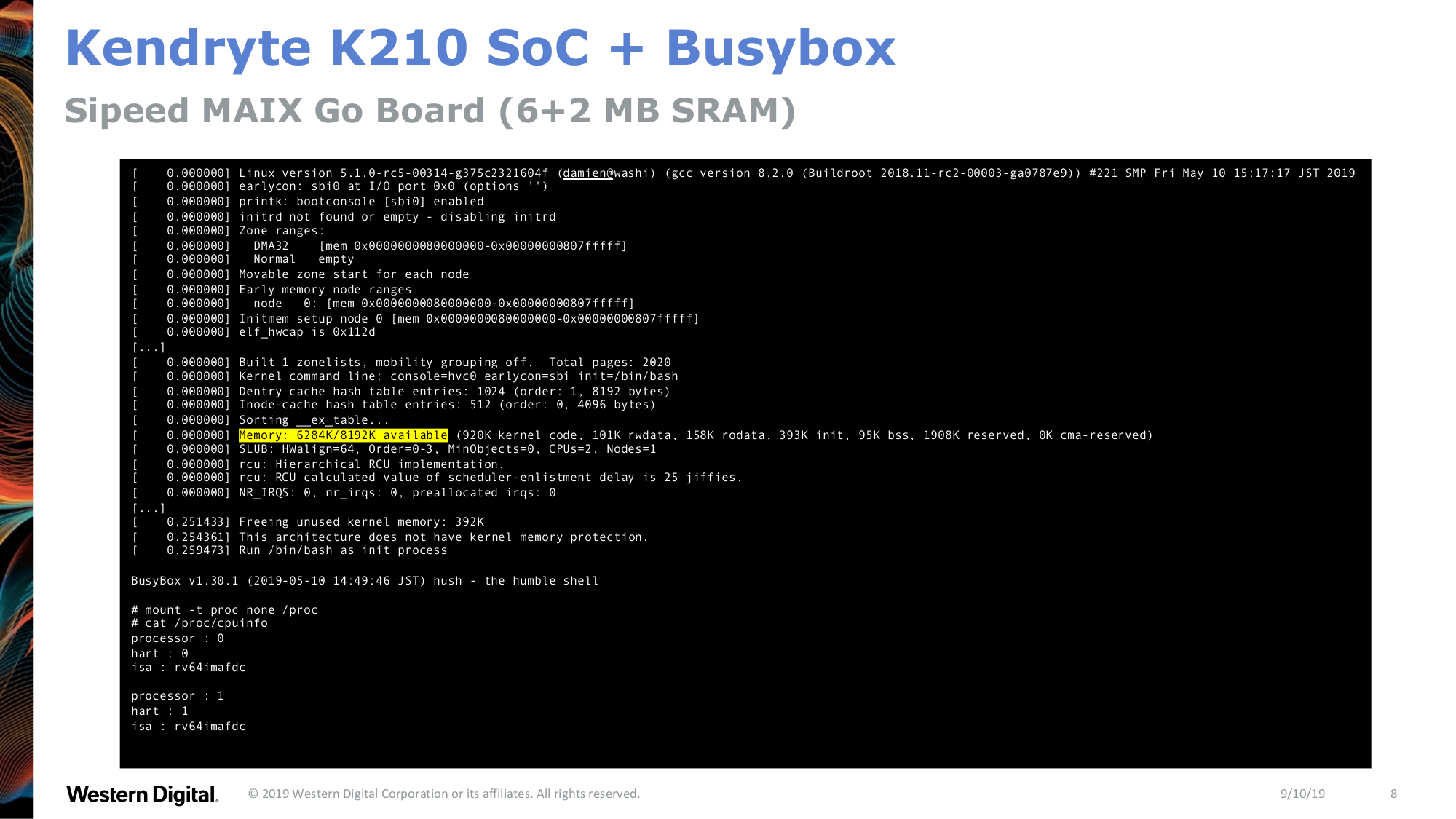

Western Digital Made RISC-V Linux & BusyBox Boot on Sipeed Maix Go Board

The other day we wrote about Getting Started with Embedded Linux on RISC-V in QEMU emulator and noted that Linux capable RISC-V hardware is currently fairly expensive. We also mentioned there was work on porting uCLinux to Kendryte K210 RISC-V processor on boards such as Sipeed Maix board. The processor only comes with 8MB RAM, and does not feature an MMU (Memory Management Unit) so what you’d be able to do on the board would be limited, and for instance, a desktop environment is clearly impossible on the platform. NOMMU support also requires some extra work, and in Linux 5.4 we saw only of the changes was “SiFive PLIC IRQ chip modifications, in preparation for M-mode Linux”. The slide above is extracted from the “RISC-V NOMMU and M-Mode Linux” presentation by Damien Le Moal, Western Digital at the Linux Plumbers Conference 2019 last September. It explains M-mode support is better […]

Linux 5.4 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.4: Not a lot happened this last week, which is just how I like it. And as expected, most of the pull requests I got were for the 5.5 merge window, which I’ll obviously start working through tomorrow. What little there is here is mostly some networking updates (mix of network drivers and core networking), and some minor GPU driver updates. Other than that it’s a small collection of random other things all over. The appended shortlog is small enough that you might as well just scroll through it. Anyway, this obviously opens the merge window for 5.5. It’s not ideal timing with Thanksgiving week coming up, but it hopefully shouldn’t be too much of an issue. If I fall behind (not because I’m all that big of a fan of the indiscriminate and relentless turkey-killing holiday) it’s because we’ve got […]

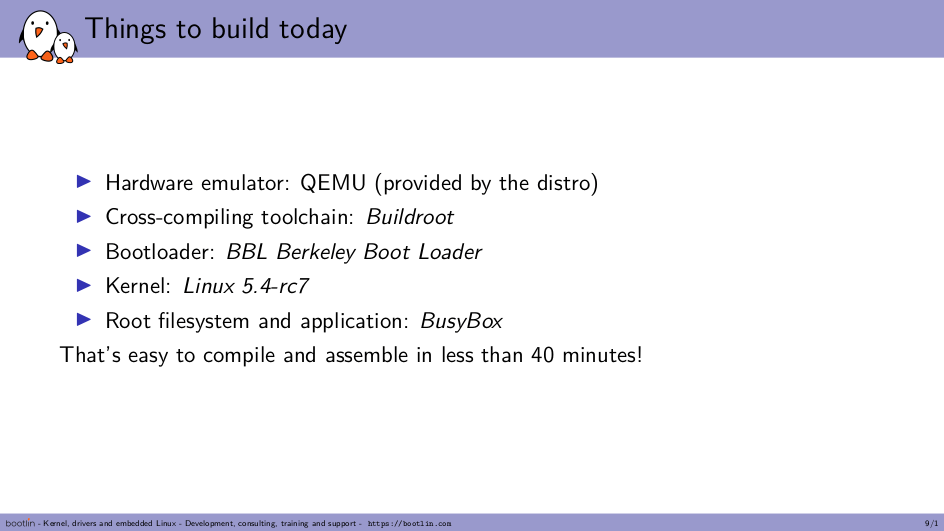

Getting Started with Embedded Linux on RISC-V in QEMU

RISC-V is getting more and more popular, but if you want to run Linux on actual hardware it’s currently fairly expensive since you either need to rely on HiFive Unleashed SBC ($999), or expensive FPGAs. Another solution is running Linux RISC-V via QEMU emulator, and I showed how to do this using BBL (Berkeley Boot Loader), Linux 4.14, and busybear rootfs. If you check the comments section of that earlier post you could also try out Fedora RISC-V images in QEMU. Bootlin has now published a presentation showing how to run embedded Linux on RISC-V in QEMU with many of the same components as in the previous instructions, but with a more up-to-date Linux kernel (5.4), and using Buildroot to build everything from scratch including the toolchain, BBL, the Linux kernel, and a Busybox based root file system. They explain each step in detail in the 45-page presentation to allow […]

Giveaway Week Winners – November 2019

We just had another of our yearly “Giveaway week” on CNX Software with 7 prizes including Arm and RISC-V development boards, NB-IoT tracker, USB-C hub, as well as development kits based on ESP32 or ESP8266 WiSoCs. People just had to comment within a 48 hours period, and we would randomly select a winner each day. We now have all confirmed winners with a strong start from Europe, Asia catching up mid-week, before with Poland and Brazil taking the week-end prizes: Balena Fin Developer Kit – Laurent H, FRANCE WisCellular NB-IoT & eMTC GPS Tracker – Jimmy, SWEDEN MINIX NEO S1 USB-C Hub with 120GB built-in SSD – Jeroen, BELGIUM Maixduino Sipeed M1 RISC-V AI Kit – Nguyen Tung, VIETNAM ANAVI Gas Detector Starter Kit – Bumsik Kim, SOUTH KOREA Particle Mesh IoT Development Kit – Wojciech Lubicz-Lapinski, POLAND NanoPi M4V2 SBC & Metal Case Kit – Thiago Tavares, BRAZIL I […]

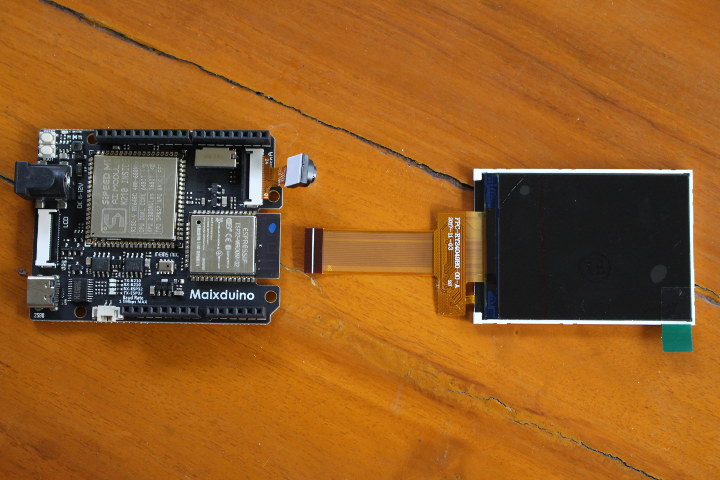

Giveaway Week – Maixduino Sipeed M1 RISC-V AI Kit

For the fourth day of Giveaway Week, I’ll give out a kit comprised of Maixduino a RISC-V development board with an AI accelerator in Arduino form factor, a camera, and a 2.4″ color LCD. I tested the Maixduino kit with MicroPython, but it can also be programmed with the Arduino IDE, or Kendryte SDK. It basically allows you to run low-power AI workloads at the edge, i.e. without access to the cloud, such as face detection. To enter the draw simply leave a comment below. Other rules are as follows: Only one entry per contest. I will filter out entries with the same IP and/or email address. Contests are open for 48 hours starting at 10 am (Bangkok time) every day. Comments will be closed after 48 hours. If comments are open, the contest is still going on. Winners will be selected with random.org and announced in the comments section […]

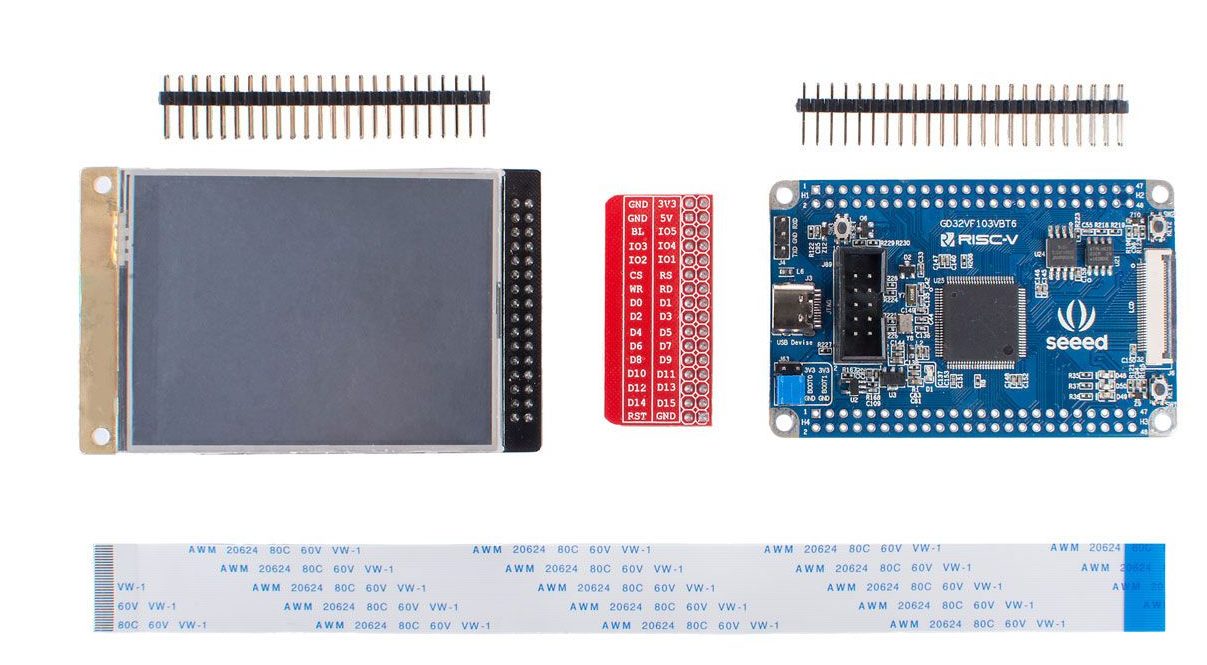

Another GD32 RISC-V Development Kit with LCD By Seeed Studio

Recently we highlighted the $5 Longan Nano, a development kit released by Sipeed for the Gigadevice GD32V RISC-V family of microcontrollers. The Sipeed Longan Nano is powered by the GigaDevice’s GD32VF103CBT6, based on Nucleisys Bumblebee kernel (support RV32IMAC instruction sets and ECLIC rapid interrupt). Seeed Studio is currently on this quest for expanding the Gigadevice GD32V RISC-V ecosystem with the launch of the SeeedStudio GD32 RISC-V kit with LCD. The Seeed Studio development kit is based on the SeeedStudio GD32 RISC-V Dev Board and a 2.8 inch 240×320 pixel resistive LCD screen. The Seeed Studio GD32 RISC-V Dev Board is based on the 32-bit general-purpose GD32VF103VBT6 MCU, which can run at up to 108MHz. It comes with a 128KB on-chip Flash memory, and a 32KB SRAM memory. The development board comes with a total of 80 GPIOs, an onboard 8MB Flash and 256 Byte EEPROM, a staggering amount resources for this […]

SiFive U8-Series Out-of-Order RISC-V Core IP Takes on Arm Cortex-A72 Core

Earlier this week, we wrote about SiFive Shield open security platform as the equivalent of Arm TrustZone security technology, but the company had had another important announcement this week with the introduction of SiFive U8-Series Out-of-Order (OoO) RISC-V Core IP with much higher performance than the company’s earlier U7-series core and competing with Arm Cortex A72 core. At first, the company will offer two standard cores with SiFive U84 RISC-V core optimized for power efficiency and area efficiency, and the SiFive U87 RISC-V core with vector processing. SiFive U84 Performance & Efficiency We do not have much information about U87, but SiFive already published some interesting details about U84 cores. SiFive U84 core offers about 3.1 times higher performance compared to their earlier U74 standard core thanks to a 2.3x increase in IPC combined with a 1.4x increase in maximum frequency. Compared to SiFive U54, U84 delivers 5.3x higher performance […]