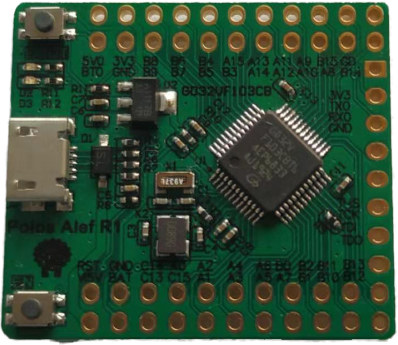

We first found out about GigaDevice GD32V 32-bit RISC-V MCU last summer, as an update/alternative to the earlier STM32 compatible GD32 Arm Cortex-M3 microcontroller from the company with higher performance and lower power consumption, while keeping the price identical. The first low-cost GD32V development board we covered was Longan Nano going for $5 with an OLED display and an acrylic case. If you don’t need either or want to access all pins from the 48-pin MCU, you can now order an even cheaper GD32V RISC-V MCU board with Polos GD32V Alef going for $2.99 on Analoglamb website. Polos GD32V Alef board specifications: MCU – Gigadevice GD32VF103CBT6 32-bit RISC-V (rv32imac) microcontroller @ 108 MHz with 128KB Flash, 32KB SRAM USB – 1x micro USB OTG port for power and programming Expansion – 52 through holes (2.54mm pitch) exposing all pins from the MCU including 3x USART, 2x I2C, 3x SPI, 2x […]

Year 2019 in Review – Top 10 Posts and Stats

2019 is closing to an end, or you may already be into 2020 while reading this post. In any case, that means it’s time to look back at 2019 and look forward to the events and new products to take place next year. While 2018 was a boring year for new processors, 2019 brought us some interesting new chips such as Amlogic S922X / A311D, or the first Arm Cortex-A55 only processors such as Amlogic S905X3. Rockchip RK3399Pro was promising when it was announced last year, but it never really took off. It was a pretty quiet year for Allwinner as well. RISC-V architecture has been ramping up with the first general-purpose RISC-V MCU: GD32V, WCH CH572 Bluetooth LE MCU, the launch of more SiFive RISC-V cores, and Kendryte K210 RISC-V AI processor announced last year has found its way into more and more boards. There have also been the […]

Some Interesting Talks from FOSDEM 2020 Schedule

We wrote about IoT devroom call for proposals for FOSDEM 2020 a little while ago, and as the free open-source developer meetup is getting closer, FOSDEM 2020 organizers released the schedule. So I’ll look at some of the talks in the relevant devrooms such as the Internet of Things, hardware enablement, Embedded, Mobile and Automotive, as well as RISC-V and others to compose my own little virtual schedule for the 2-day event. Saturday, February 1 10:30 – 10:50 – How lowRISC made its Ibex RISC-V CPU core faster – Using open source tools to improve an open-source core – by Greg Chadwick Ibex implements RISC-V 32-bit I/E MC M-Mode, U-Mode, and PMP. It uses an in-order 2 stage pipe and is best suited for area and power-sensitive rather than high-performance applications. However, there is scope for meaningful performance gains without major impact to power or area. This talk describes work […]

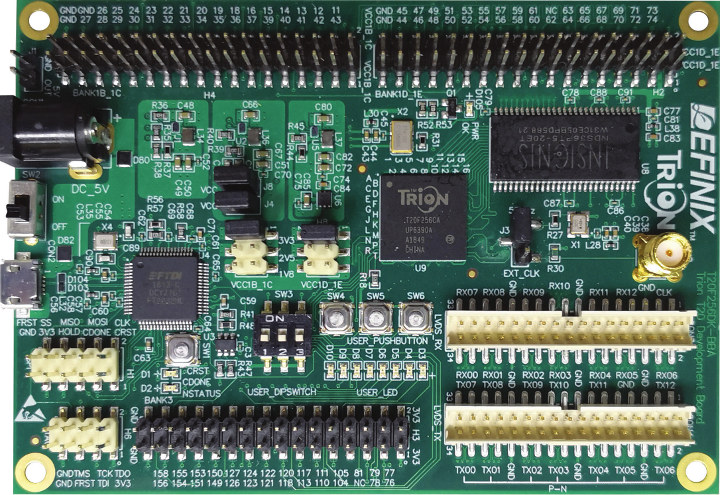

Trion T20 BGA256 FPGA Development Kit Supports “PulseRain Reindeer” RISC-V RV32IM soft CPU

A few months ago I wrote about FireAnt low-cost FPGA development board powered by Efinix Trion T8 FPGA, and it was the first time I personally heard about the company. Trion FPGA family range from the T4 with 3,888 logic elements up to the Trion T200 with 192,000 LE’s. A board more powerful than FireAnt, but not quite high-end, recently showed up on Digikey with Trion T20 BGA256 development kit going for $150. Trion T20 BGA256 Development Kit specifications: FPGA – Efinix Trion T20 FPGA with 19,728 LE’s, 1,044 Kbit embedded RAM, 36 18×18 multipliers, 7 PPL’s, up to 220 GPIO’s; 256-ball FBGA (13×13 mm) System Memory – 256 Mbit SDR SDRAM Storage – NOR flash USB – 1x Micro-USB port for programming Debug / Configuration – SPI and JTAG headers to facilitate configuration Expansion 3x I/O headers to connect to external devices LVDS TX header, LVDS RX & clock […]

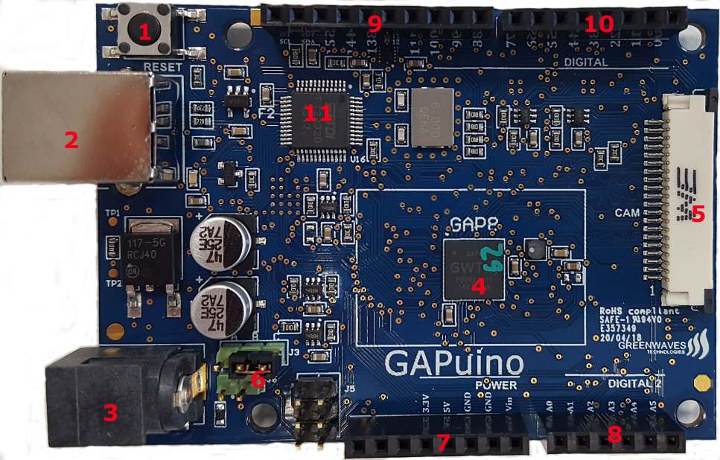

GreenWaves GAP9 IoT Application Processor Enables AI on Coin-cell Powered Devices

GreenWaves Technologies GAP8 multi-core RISC-V microcontroller was introduced last year for artificial intelligence (AI) at the edge at ultra-low power consumption. GAP8 AIoT SoC was shown to perform inference at 3.7mA against 60mA for the same workload on STM32F7 Arm Cortex-M7 MCU. The company has now expanded its GAP IoT application processor family with GAP9 that delivers five times lower power consumption compared to GAP8 microcontroller while enabling inference on neural networks 10 times larger. Greenwaves GAP9 will bring machine learning and signal processing capabilities to (coin cell) battery operated or energy harvesting devices such as IoT sensors in consumer and industrial markets, wearables, smart building, smart farming and so on. GAP9 is said to combine architectural enhancements with Global Foundries 22nm FDX process to achieve a peak cluster memory bandwidth of 41.6 GB/sec and up to 50 GOPS compute power while consuming only 50mW. The increased memory bandwidth (20x […]

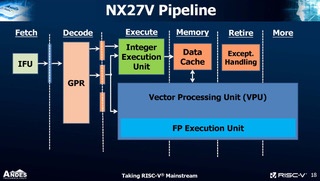

AndesCore 27-Series Linux RISC-V SoC Features a Vector Processing Unit

AndesCore 27-Series VPU Andes has developed a Linux capable RISC-V based SoC which runs on the first Vector Processing Unit (VPU) that is reported to be groundbreaking in its application ability, especially in the AI sector. The Andes 27 Series CPU has debuted in the RISC-V Summit in San Jose, to a great deal of talk in many quarters. The AndesCore 27-Series RVV The company reports that the AndesCore 27 offers a user-configurable vector-processing unit that has a scalable data size, flexible microarchitecture implementations and subsystem memory decisions open to system-level optimization. The use of the RISC-V Vector (RVV) instruction extension allows the CPU cores to deliver higher performance and versatility. The TimeTable and Offerings Andes is saying delivery of its first Andes 27 RISC-V based SoC will begin in Q1 2020. Already the earliest licensees have seen the delivery of the betas. Initial availability will center around a […]

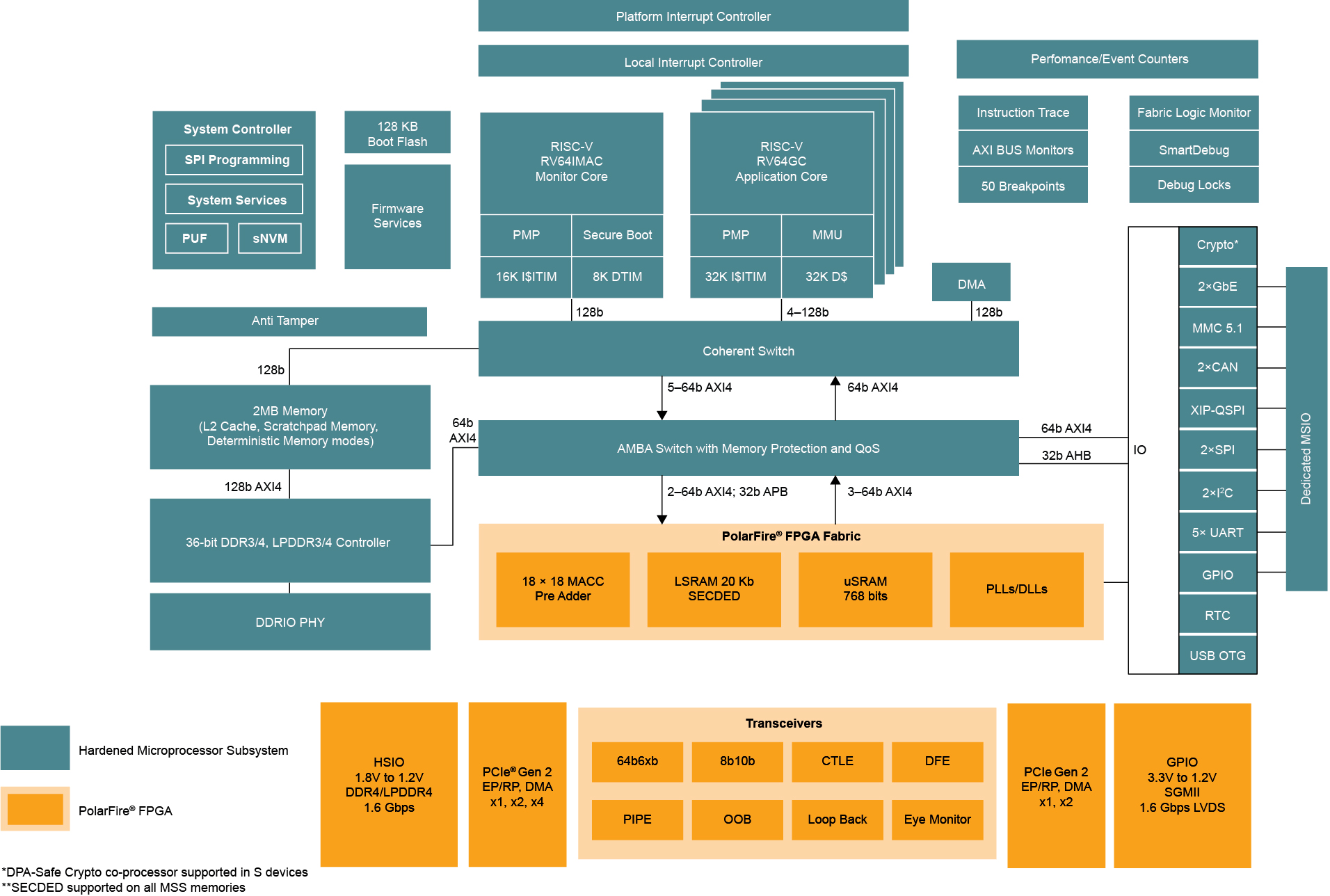

RISC-V based PolarFire SoC FPGA and Devkit Coming in Q3 2020

Microsemi unveiled PolarFire FPGA + RISC-V SoC about one year ago, but at the time, development was done on a $3,000 platform with SiFive U54 powered HiFive Unleashed board combined with an FPGA add-on board from Microsemi. I’ve now been informed that Microchip has announced its Linux-capable PolarFire FPGA+RISC-V SoC would start shipping in Q3 2020 at the RISC-V summit and that a development kit will be sold for a few hundred dollars. PolarFire SoC FPGA PolarFire SoC FPGA key features and specifications: Mid-Range FPGA optimized for Low Power High-speed serial connectivity with built-in multi-gigabit/multi-protocol transceivers from 250 Mbps to 12.7 Gbps Up to 461k logic elements consisting of a 4-input Look-Up Table (LUT) with a fracture-able D-type flip-flop Up to 31.6 Mb of RAM Power optimized transceivers Up to 1420 18 × 18 multiply-accumulate blocks with hardened pre-adders Integrated dual PCIe for up to ×4 Gen 2 Endpoint […]

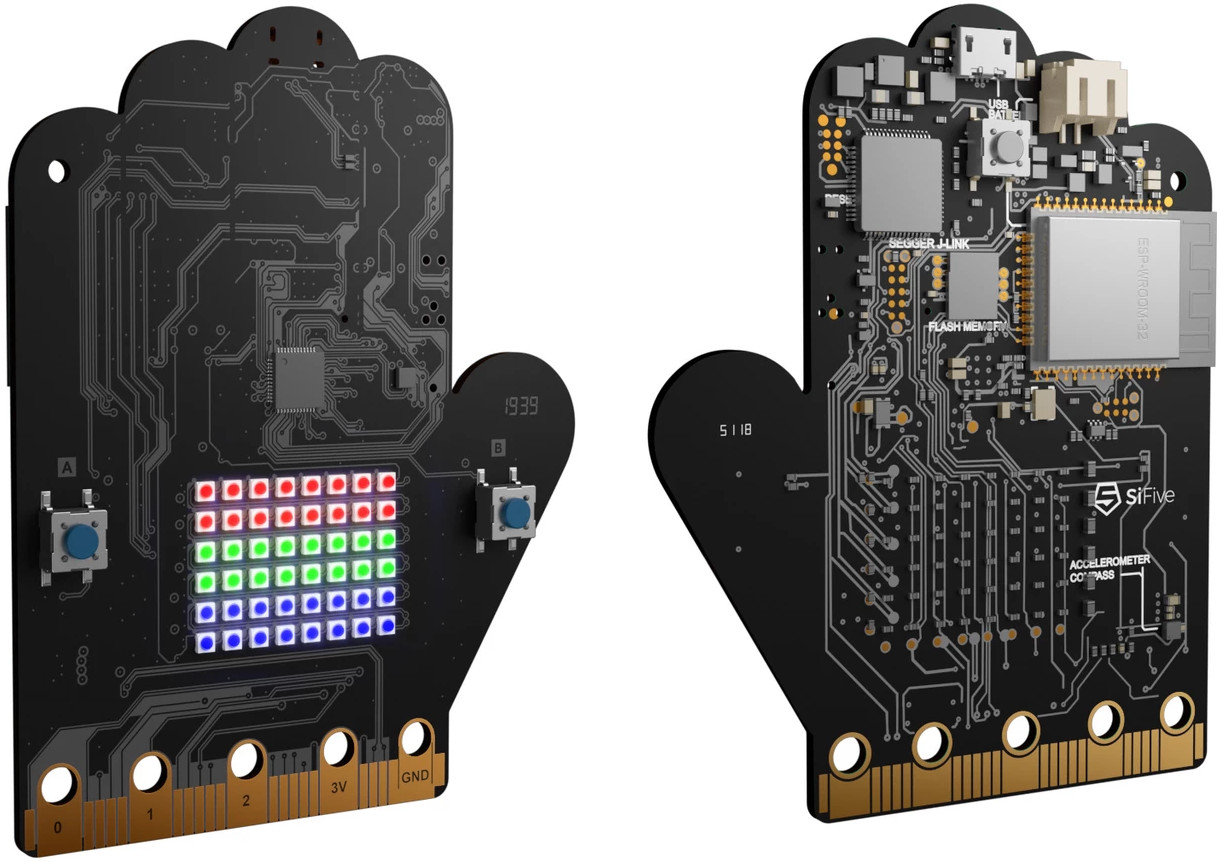

SiFive Learn Inventor is a Wireless RISC-V Development Kit Inspired by BBC Micro:bit

SiFive Learn Inventor is a RISC-V educational board partially inspired by BBC Micro:bit board with the same crocodile clip-friendly edge connector, and an LED matrix. The board is also fully qualified to work with the Amazon FreeRTOS real-time operating system. Shaped in the form of a hand, the board features SiFive FE310 RISC-V processor found in the SiFive HiFive1 board, as well as ESP-WROOM-32 WiFi + Bluetooth module. SiFive Learn Inventor specifications: SoC – SiFive FE310-G003 32-bit RISC-V (RV32IMAFC) processor @ 150 MHz with 64KB of internal SRAM Storage – 512 KB flash “Display” – 6×8 “widescreen” array of RGB LEDs with 262,000 colors each; LEDs can expand off-board onto external arrays via the edge connector Wireless Connectivity – 802.11b/g/n WiFi 4 (2.4GHz) and Bluetooth 4.2 LE via an ESP32 module (ESP-WROOM-32) USB – 1x Micro USB port for power and programming/debugging Expansion A/D Converters (four) accessed via on-board coprocessor […]