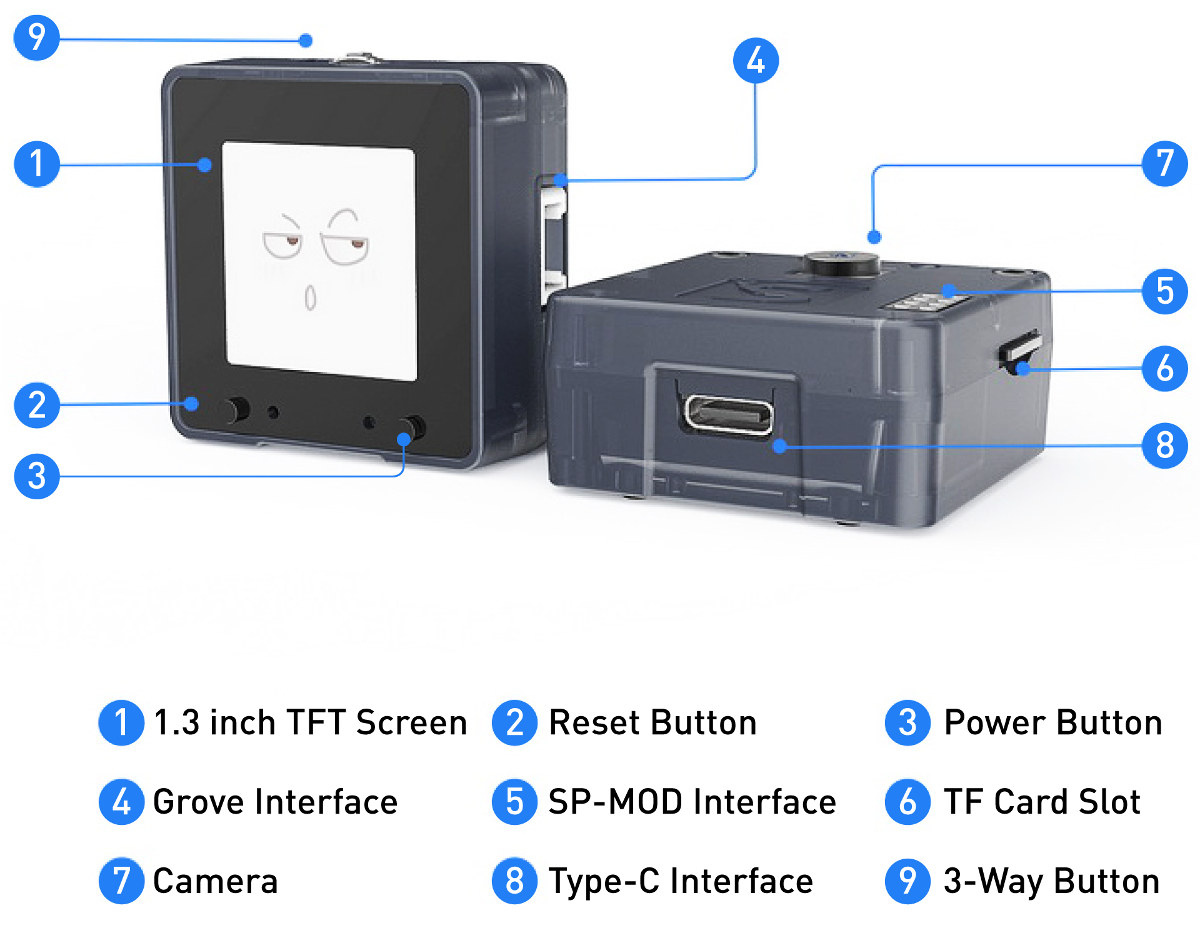

Sipeed has made several boards and kits based on Kendryte K210 RISC-V processor for low-power AI workloads such as face detection or object recognition including Maixduino board and Grove AI HAT that ship with camera and display. The company has now come up with MaixCube all-in-one development platform that houses Sipeed M1 module, a display, a camera, and a battery into a plastic case that’s somewhat similar to MStack M5StickV but with a larger display, and variations in the form factor and features. Sipeed MaixCube specifications: SoC – Kendryte K210 dual-core 64-bit RISC-V processor @ 400 MHz (overclockable to 600 MHz) with FPU, 8MB SRAM, KPU AI accelerator, APU audio processor, and FFT accelerator Storage – 128 Mbit flash, MicroSD card slot Display – 1.3″ TFT screen with 240×240 resolution Camera – OV7740 sensor (VGA camera) Audio – Built-in microphone, external speakers support; ES8374 audio codec USB – 1x USB […]

Linux 5.6 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.6 on the Linux Kernel Mailing List: So I’ll admit to vacillating between doing this 5.6 release and doing another -rc. This has a bit more changes than I’d like, but they are mostly from davem’s networking fixes pulls, and David feels comfy with them. And I looked over the diff, and none of it looks scary. It’s just slightly more than I’d have preferred at this stage – not doesn’t really seem worth delaying a release over. So about half the diff from the final week is network driver fixlets, and some minor core networking fixes. Another 20% is tooling – mostly bpf and netfilter selftests (but also some perf work). The rest is “misc” – mostly random drivers (gpio, rdma, input) and DTS files. With a smattering of fixes elsewhere (a couple of afs fixes, some vm fixes, etc). […]

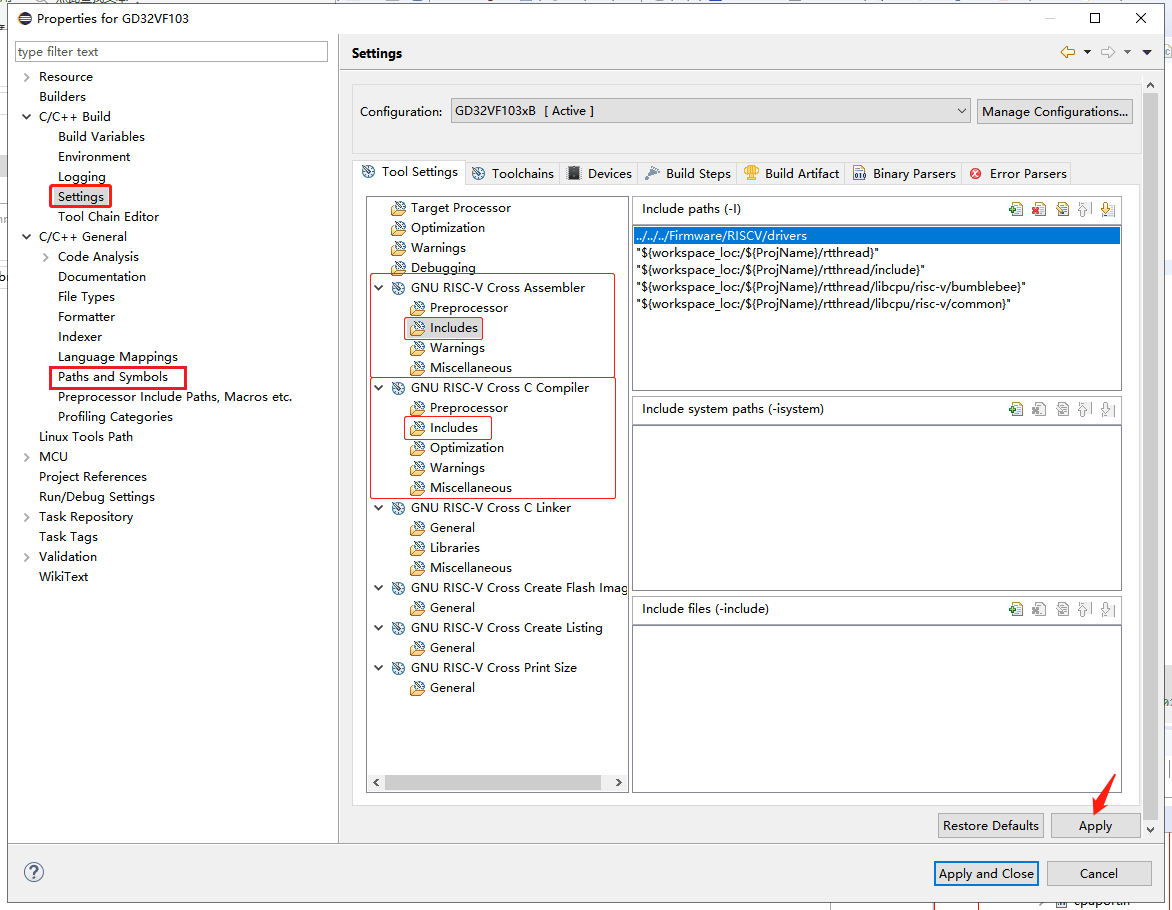

Getting Started with RT-Thread Nano RTOS on RISC-V Processors

CNXSoft: This is a guest post by RT-Thread explaining how to create your first program running on their real-time operating system using a GD32V RISC-V MCU board as an example. This article describes how to “port” RT-Thread Nano to the RISC-V architecture, using the Eclipse IDE, GCC toolchain, and a basic project for the Gigadevice GD32V103 MCU. Foreword RT-Thread is an open-source embedded real-time operating system. RT-Thread has a standard version and a Nano version. The standard version consists of a kernel layer, components and service layer, and IoT framework layer, while the Nano version has a very small footprint and refined hard real-time kernel, better suited to resource-constrained microcontroller units (MCU). The main steps for porting Nano are as follows: Prepare a basic Eclipse project and get the RT-Thread Nano source code. Add the RT-Thread Nano source code to the base project and add the corresponding header path. Modify […]

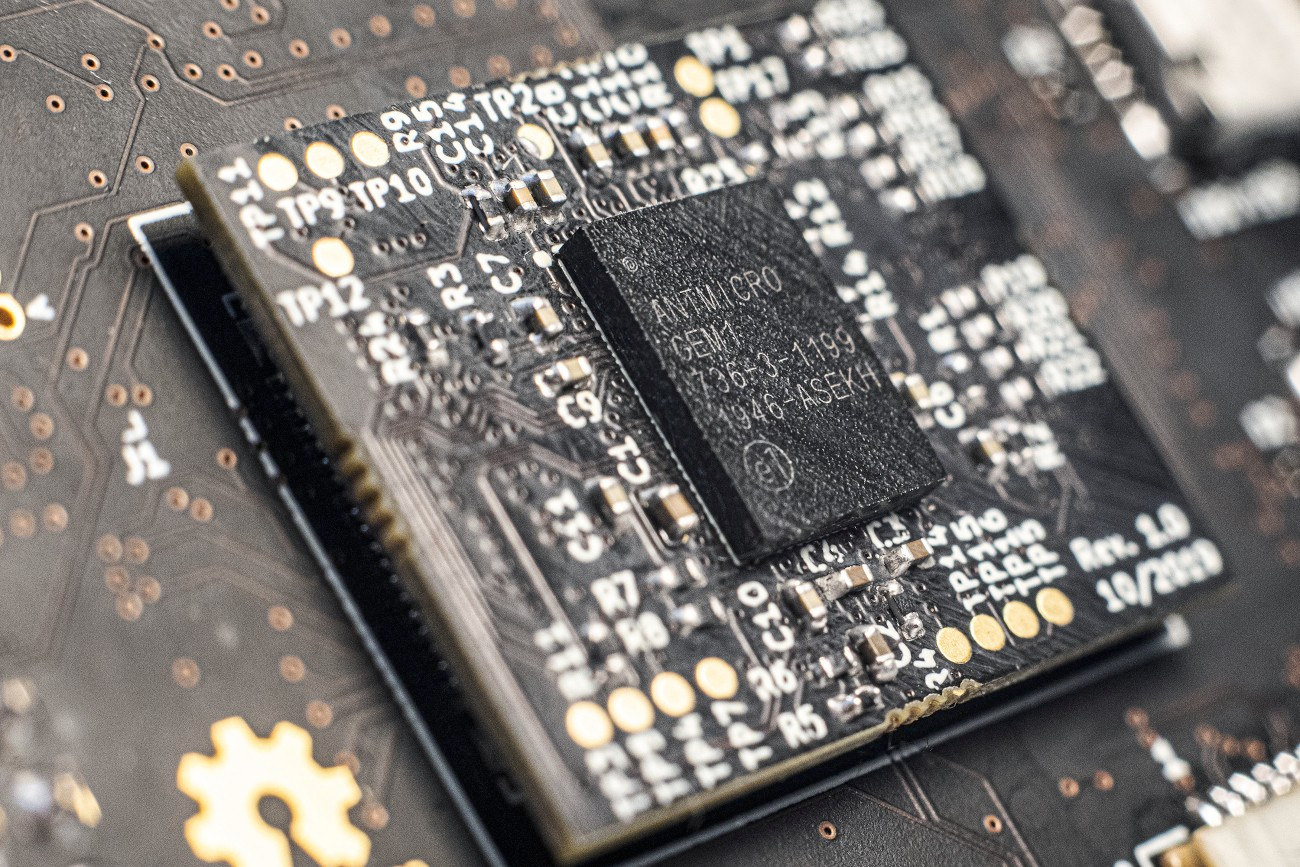

Antmicro GEM ASIC Leverages zGlue Technology to Quickly Bring Custom Arm/RISC-V SoC’s to Market

Introduced in 2018, ZiP (zGlue Integration Platform) chip-stacking technology aims to produce chips similar to Systems-in-Package (SiP) but at much lower costs and lead times. We first found it in a Bluetooth tracker featuring ZGLZ1BA custom chip manufactured with zGlue technology and integrating an Arm Cortex-M0 MCU, flash memory and sensors into a single package. But now the technology is back in the news with Antmicro announcing GEM chiplet-based ASIC last December. At the time of the announced the company’s GEM1 chip featured two Lattice iCE40 FPGAs with a MIPI CSI-2 switch, and they had started working on GEM2 chip combining a hard RISC-V processor and Lattice iCE40 FPGA. Those are so-called demonstrators chip as Antmicro customers will be able to easily and quickly design their own 6×9 mm chip(s) with RISC-V and/or ARM CPUs, FPGAs, sensors, radios and other functional elements to meet the requirements of their specific applications. […]

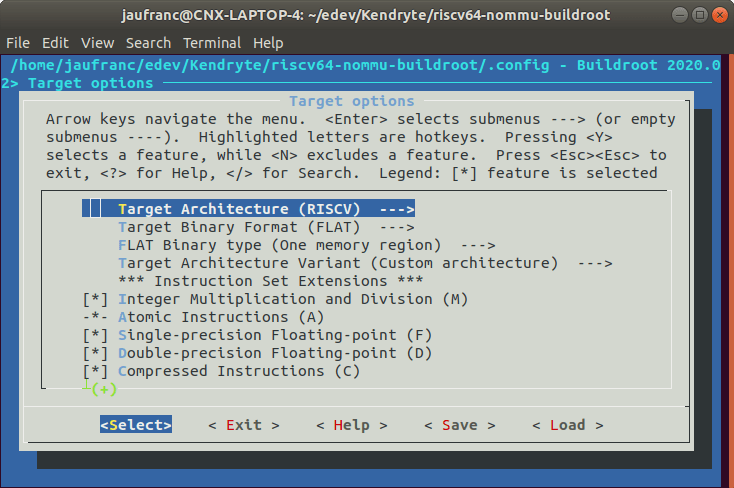

How to Build & Run Linux on Kendryte K210 RISC-V NOMMU Processor

A few months ago, we wrote that Western Digital was working on Linux & BusyBox RISC-V NOMMU, and managed to boot a minimal Linux OS on Kendryte K210 powered Sipeed Maix Go board. RISC-V NOMMU support was scheduled for Linux 5.5, and now that the new kernel has been released, Damien Le Moal has pushed the code allowing to build Linux and a busybox based roofs for RISC-V 64-bit NOMMU platforms using buildroot. I could start the build following the instructions on Github, but it failed as a Linux 5.6 RC1 tarball was missing. But I noticed “Vowstart” picked up on Damien’s work, and wrote detailed instructions. So let’s try the build out using a machine running Ubuntu 18.04. We’ll have to make sure dependencies are installed first:

|

1 2 |

sudo apt install build-essential device-tree-compiler bison \ flex file git curl wget cpio python unzip rsync bc texinfo |

Then we can retrieve the source code and do some preparations (e.g. extract Linux 5.6 RC1 tarball):

|

1 2 3 4 |

git clone https://github.com/vowstar/k210-linux-nommu.git cd k210-linux-nommu export PROJ_ROOT=$(pwd) sh ./prepare_buildroot.sh |

The next step […]

Linux 5.5 Release – Main Changes, Arm, MIPS and RISC-V Architectures

Linux 5.5 has just been released by Linus Torvalds: So this last week was pretty quiet, and while we had a late network update with some (mainly iwl wireless) network driver and netfilter module loading fixes, David didn’t think that warranted another -rc. And outside of that, it’s really been very quiet indeed – there’s a panfrost driver update too, but again it didn’t really seem to make sense to delay the final release by another week. Outside of those, it’s all really tiny, even if some of those tiny changes touched some core files. So despite the slight worry that the holidays might have affected the schedule, 5.5 ended up with the regular rc cadence and is out now. That means that the merge window for 5.6 will open tomorrow, and I already have a couple of pull requests pending. The timing for this next merge window isn’t optimal […]

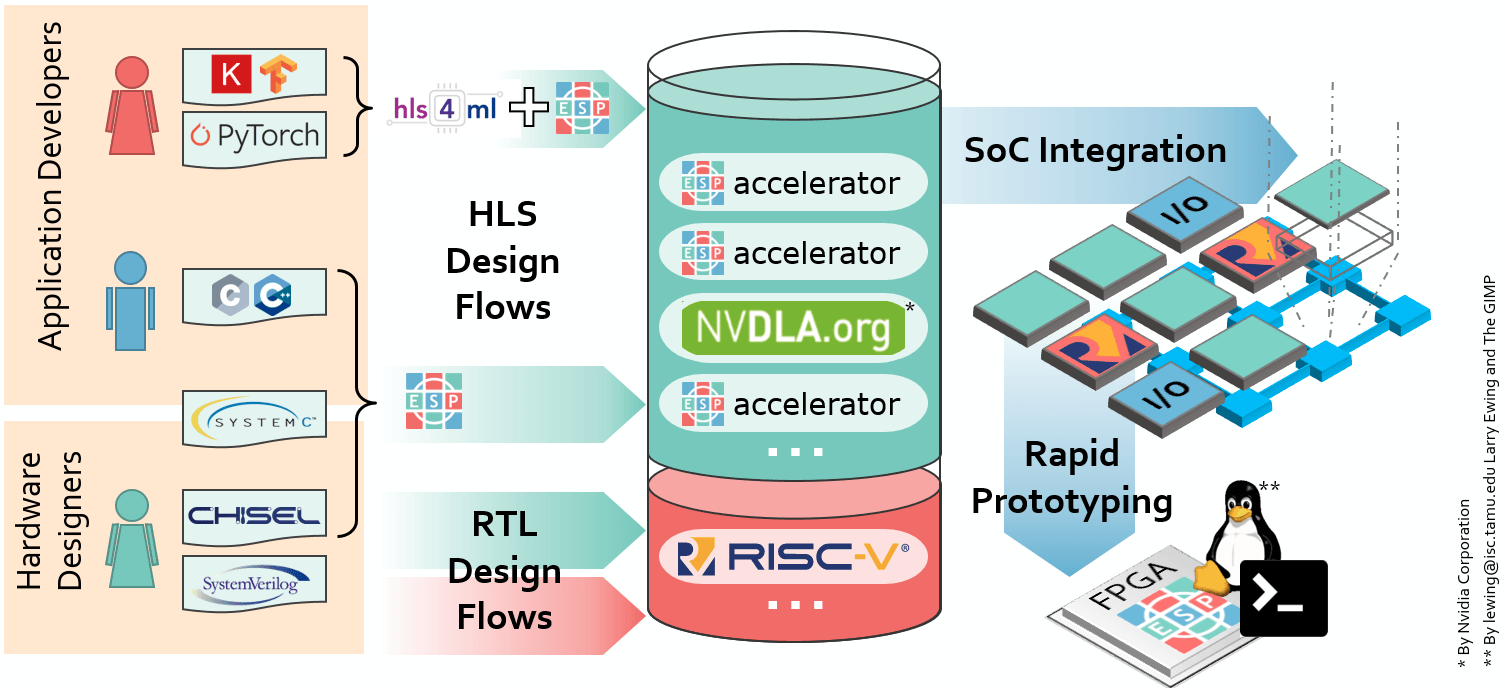

ESP Open Source Research Platform Enables the Design of RISC-V & Sparc SoC’s with Accelerators

FOSDEM 2020 will take place next week, and there will be several interesting talks about open-source hardware and software development. One of those is entitled “Open ESP – The Heterogeneous Open-Source Platform for Developing RISC-V Systems” with an excerpt of the abstract reading: ESP is an open-source research platform for RISC-V systems-on-chip that integrates many hardware accelerators. ESP provides a vertically integrated design flow from software development and hardware integration to full-system prototyping on FPGA. For application developers, it offers domain-specific automated solutions to synthesize new accelerators for their software and map it onto the heterogeneous SoC architecture. For hardware engineers, it offers automated solutions to integrate their accelerator designs into the complete SoC. If we go to the official website, we can see ESP (Embedded Scalable Platform) actually supports both 32-bit Leon3 (Sparc) and 64-bit Ariane (RISC-V) cores, and various hardware accelerators from the platform or third parties. Highlights: […]

ONiO.zero offers a RISC-V Microcontroller that runs without battery

Energy harvesting has been an exciting area people have tried to venture into mostly because of the possible applications that can arise from it. Newly invented energy-harvesting technologies accompanying low-power computing systems have pushed the boundaries of where embedded systems can be deployed. The demand for an increase in connected applications which require an underlying embedded system, and as we know, all electronic devices require a power source of some sort. This power source, batteries in most cases, comes with an accompanying buck regulator of some sort that will tend to increase the BOM. Aside from the BOM rise from the usage of batteries, there is also the shelf life and environmental aspects. The Norwegian specialist ONiO has introduced the ONiO.zero to address those issues. Having no battery means fewer components and a smaller design, which can easily be integrated into a wide range of solutions – be it fabrics, […]