SiFive may just have announced a mini-ITX motherboard for RISC-V PCs, but if you’d like a RISC-V Linux platform in a more compact form factor, Sundance PolarBerry may better fit your requirements, albeit the board will target different use cases. Powered by Microchip PolarFire RISC-V SoC FPGA, PolarBerry is both a single board computer with Gigabit Ethernet and 40-pin GPIO header, as well as a system-on-module thanks to three Samtec board-to-board connectors. PolarBerry specifications: SoC – Microsemi PolarFire FPGA MPFS250T-FCVG484 penta-core processor with 1x RV64IMAC monitor core, 4x RV64GC application cores, FPGA fabric with 254K x logic elements (4LUT + DFF), 784 x math blocks (18 x 18 MACC), and 16 x SERDES lanes at 12.5 Gbps; 12 W maximum power consumption System Memory – 4 GB of 32-bit wide DDR4 memory Storage – 4GB eMMC flash, 128 Mbit SPI Serial NOR flash for boot image Networking – Gigabit Ethernet […]

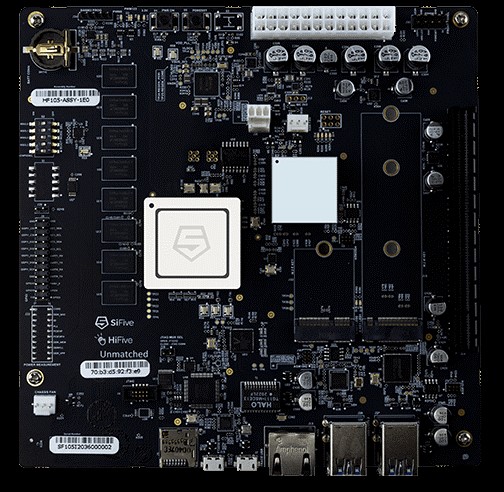

SiFive launches HiFive Unmatched mini-ITX motherboard for RISC-V PC’s

When it comes to RISC-V based SoC, SiFive has always set a benchmark in the RISC-V ecosystem. On 29th October 2020, SiFive confirmed the first-ever RISC-V PC. After an increased demand for AI-focused RISC-V microarchitecture, targeting all applications from artificial intelligence, the internet of things, high-performance computing, and now even desktop PCs. SiFive Freedom U740 powered HiFive Unmatched mini-ITX motherboard comes with a complete development environment which allows developers to create RISC-V based applications from bare-metal to Linux-based systems. “HiFive Unmatched ushers in a new era of RISC-V Linux development with a platform in a PC form factor. Powered by the SiFive Freedom U740, a high-performance multi-core, 64-bit dual-issue, superscalar RISC-V processor.”, SiFive says. It is the world’s fastest native RISC-V development platform. SiFive HiFive Unmatched Board At the heart of the SiFive board is a SiFive FU740 processor coupled with 8 GB DDR4 memory and 32 MB SPI Flash. It […]

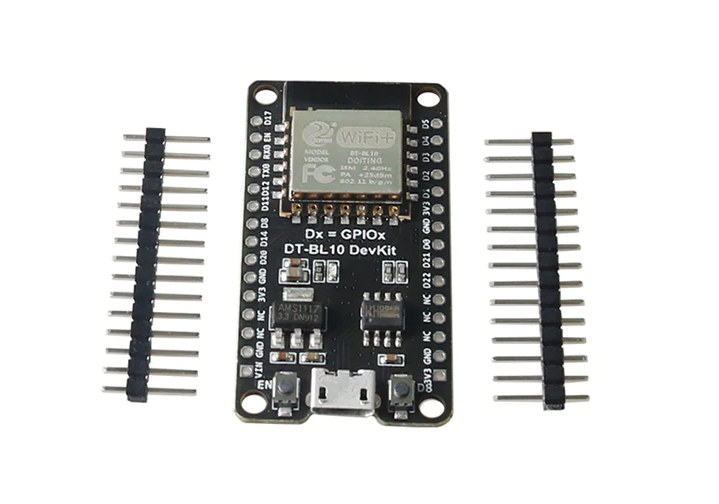

BL602 IoT SDK and $5 DT-BL10 WiFi & BLE RISC-V development board

Yesterday, we wrote about Bouffalo BL602 32-bit RISC-V WiFI and Bluetooth LE wireless SoC that should eventually compete with ESP8266 in terms of price but with more features, higher performance. and more resources like memory and storage. At the time, I noted I could not find any tools for the processor, but I was informed a BL602 SDK (Doiting_BL) and documentation had already been released on Github. The basic readme and a user manual are already available in English, but the main documentation is still in Chinese with various examples to configure GPIO, YART, WiFi, and Bluetooth. You’ll find the documentation in Github, as I could not find a website yet:

|

1 |

git clone https://github.com/SmartArduino/Doiting_BL |

Go to Doiting_BL/docs/html folder and then open index.html in your browser to access the documentation. The SDK works both in Windows and Linux and relies on either Eclipse & OpenOCD or Freedom Studio & OpenOCD. A graphical software […]

CloudBEAR BM-310 RISC-V MCU core for IoT applications

In the pool of 32-bit RISC-V microcontroller cores (E20 by SiFive, VEGA ET1031 by C-DAC), CloudBEAR showcased its 32-bit small and efficient MCU core – BM-310 at RISC-V GLOBAL FORUM 2020. CloudBEAR works on providing services like processor IP customization, support for RISC-V ISA extensions, product integration within a system-on-chip, and configurable instruction and data cache. Let’s first look into the CloudBEAR processor IP portfolio. It has three different product lines- BM series, BR series, and BI series. First, the BM series targets small and efficient MCUs cores. Second, the BR series targets fast and compact embedded cores. The third and most important BI series is about Linux capable application cores. In this article, we will look into the details of BM-310, which is the RISC-V MCU core for embedded and IoT solutions. BM-310 Architecture As RISC-V is a modular instruction set, extensions are optional for the developer. BM-310 architecture […]

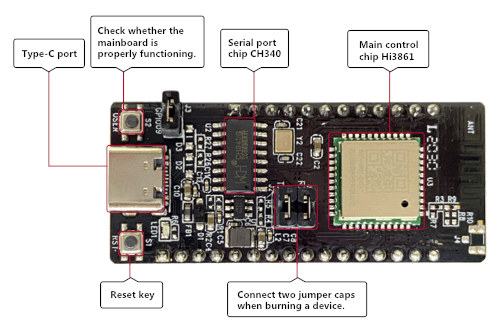

Hi3861 based HiSpark WiFi IoT development board supports LiteOS and HarmonyOS

HiHope HiSpark WiFi IoT development board features Hisilicon Hi3861 microcontroller with 2.4 GHz 802.11b/g/n WiFi 4 and supports Huawei LiteOS as well as HarmonyOS. Equipped with 2MB flash and 384KB SRAM, the board targets smart home applications, and ships with a baseboard to help with development. HiSpark board specifications: MCU – Hisilicon Hi3861 32-bit microcontroller @ up to 160 MHz with 352 KB SRAM and 288 KB ROM, 2 MB flash memory, and WiFI 4 connectivity; QFN-32 5x5mm package WiFi 802.11b/g/n standard up to 72 Mbps @ HT20 2.4 GHz frequency band (ch1-ch14). Station (STA) and access point (AP) modes with up to 6 clients for the latter WiFi mesh with up to 256 nodes Security – WPA, WPA2 personal, and WPS 2.0 PCB antenna USB – 1x USB Type-C port for power and programming via CH340 chip Expansion – 2x headers with up to 2x SPI, 2x I2C, 3x […]

Linux 5.9 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.9 on lkml: Ok, so I’ll be honest – I had hoped for quite a bit fewer changes this last week, but at the same time there doesn’t really seem to be anything particularly scary in here. It’s just more commits and more lines changed than I would have wished for. The bulk of this is the networking fixes that I already mentioned as being pending in the rc8 release notes last weekend. In fact, about half the patch (and probably more of the number of commits) is from the networking stuff (both drivers and elsewhere). Outside of that, the most visible thing is a reinstatement of the fbdev amba-clcd driver – that’s a noticeable patch, but it’s basically just mainly a revert. The rest is really really tiny (mostly some other minor driver updates, but some filesystem and architecture fixes […]

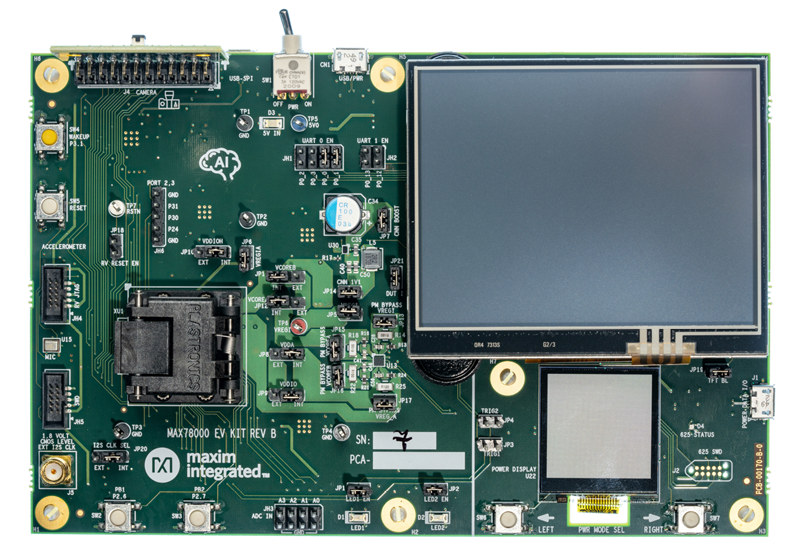

MAX78000 RISC-V & Cortex-M4F MCU enables IoT artificial Intelligence in battery-powered devices

Now even endpoints like sensors are capable of running basic artificial intelligence workloads thanks to microcontroller-class chips with built-in AI accelerators or instructions such as Kneron KL720 Arm Cortex-M4 AI SoC, GAP8 RISC-V IoT processor, or Cortex-M55 MCU core coupled with Ethos U55 MicroNPU. Maxim Integrated has now launched its own AI capable microcontroller with MAX78000 combining a Cortex-M4F core, a 32-bit RISC-V core, and a CNN accelerator enabling AI inferences at less than 1/100th the energy or 100 times the speed of software solutions making especially suited for battery-powered AI applications. MAX78000 specifications: Ultra-Low-Power microcontrollers Arm Cortex-M4F core with FPU Up to 100MHz with 512KB Flash and 128KB SRAM 32-Bit RISC-V ultra-low-power co-processor up to 60MHz Neural Network Accelerator optimized for Deep Convolutional Neural Networks (CNN) 442k 8bit Weight Capacity with 1,2,4,8-bit Weights Input Image Size up to 1024 x 1024 pixels Network Depth up to 64 Layers Layer […]

SiFive to Debut RISC-V PC for Developers based on Freedom U740 next-gen SoC

In recent years, people have discussed the need to have Arm-based PCs or workstations for developers to work directly on the target hardware, and there are now several options including SynQuacer E-Series 24-Core Arm PC, Ampere eMAG 64bit Arm Workstation, and HoneyComb LX2K 16-core Arm Workstation. Now it appears we’ll soon get something similar for RISC-V architecture with SiFive to debut the first RISC-V PC for developers at the Linley Fall Processor Conference 2020 taking place on October 20-22 and October 27-29. The PC will be powered by Freedom U740 next-generation RISC-V processor that will also be introduced at the event. We have very few details about this point in time, but the company points the SiFive Freedom U740 (FU740) SoC will enable professional developers to create RISC-V applications from bare-metal to Linux-based. The processor is said to combines a heterogeneous mix+match core complex with modern PC expansion capabilities, which […]