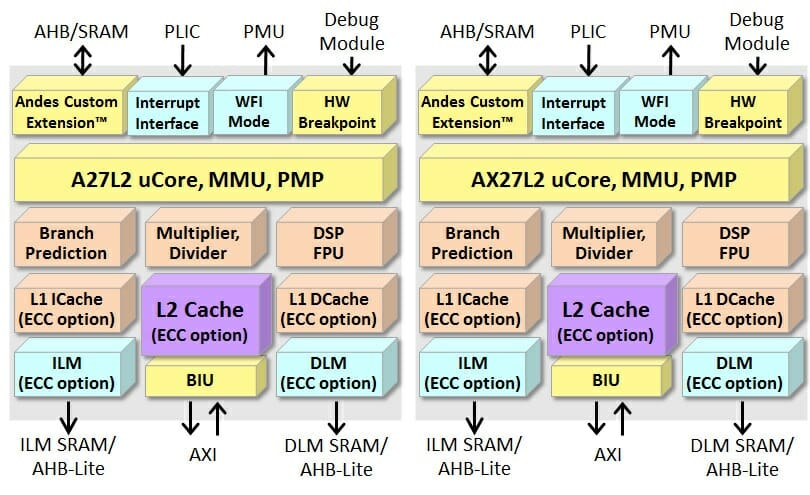

Last year, Andes introduced the AndesCore 27-Series of Linux capable RISC-V cores with a vector processing unit for AI acceleration with specifically the 32-bit A27 and the 64-bit AX27 cores. The company also introduced the higher-end AndesCore 45-series (A45 and AX45) at about the same time, but we somehow missed the announcement. Andes has now added more Linux capable RISC-V AndesCore to the aforementioned families with the high-performance superscalar A45MP and AX45MP multi-core processors, and A27L2 and AX27L2 processors with an L2 cache controller. Andes A27L2 and AX27L2 cores Based on the highlights, the new cores look identical to the A27 and AX27L2 cores announced last year expect the additional L2 cache that comes with optional ECC. AndesCores A27L2 and AX27L2 key features and specifications: AX27L2 – 64-bit, 5-stage pipeline CPU architecture (RV64GCPN), enabling software to utilize the memory spaces far beyond 4GB A27L2 – 32-bit, 5-stage pipeline CPU architecture […]

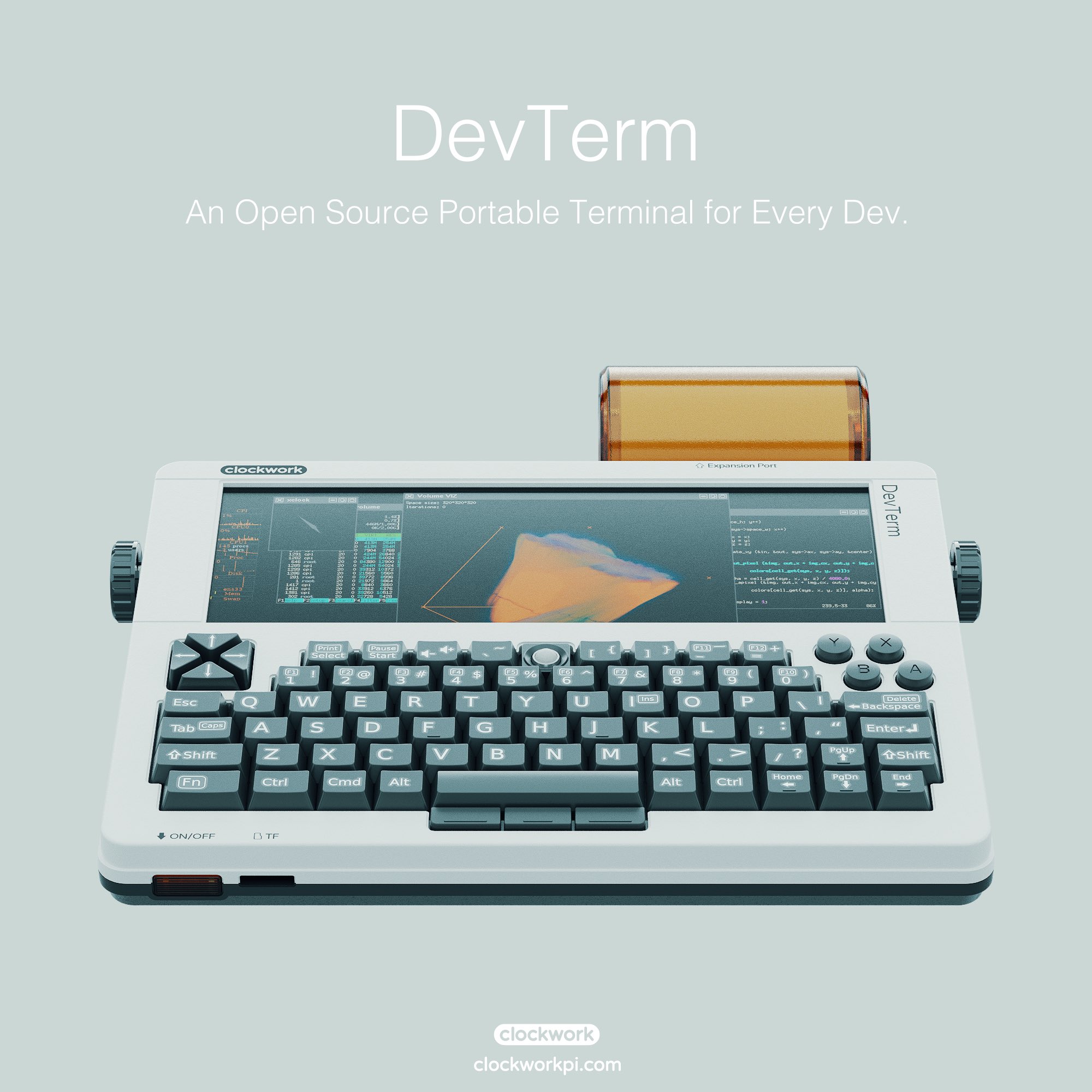

DevTerm with ClockworkPi v3.14: a modular, portable computer

After the launch of ClockworkPi GameShell in Q4 2018, now ClockworkPi has come with yet another exciting product. DevTerm is a portable computer that comes with a 6.8-inch IPS screen, a keyboard with 67 keys, and a battery module, all connected to ClockworkPi v3.14 carrier board and a choice of core modules. It will also come with an optional built-in thermal printer. ClockworkPi v3.14 Mainboard and the Core boards The mainboard ClockworkPi v3.14 uses a compact design and comes with a reduced size of 95x77mm. With a modular design, it gives you a choice of “core board” modules for various applications. Moreover, ClockworkPi v3.14 is now compatible with the Raspberry Pi CM3 series, which means that your work on the Raspberry Pi can be “teleported” to a portable terminal without hassle. It has integrated 5GHz WIFI (802.11ac) and Bluetooth 5.0 which makes it suitable for wireless communication applications as well. […]

M1108 AI accelerator chip delivers up to 35 TOPS for high-end edge AI applications

Last week, Mythic announced a breakthrough with compute-in-memory technology based on a 40 nm process with what the company claims to be the industry’s first Analog Matrix Processor. The M1108 AMP AI accelerator chip targets high-end edge AI applications including smart home, AR/VR, drones, and is said to set a benchmark in the industry for high performance and low power in a single cost-effective device, also available in M.2 and PCIe form factors. The M1108 comes with an array of flash cells, ADCs, a 32-bit RISC-V nano-processor, a SIMD vector engine, SRAM, and a high-throughput Network-on-Chip (NOC) router. With 108 AMP tiles, the M1108 provides up to 35 Trillion-Operations-per-Second (TOPS) enabling ResNet-50 at up to 870 fps. This enables a power-efficient execution of complex AI models such as ResNet-50, YOLOv3, and OpenPose Body25. The industry leader NVIDIA also has a similar AI accelerator chip NVIDIA Xavier AGX which delivers up […]

Pine64’s PINECIL RISC-V soldering iron launched for $25

We’ve previously mentioned PINECIL RISC-V soldering iron during Pine64’s release of PineCube open-source IP camera development kit, and the good news is the soldering iron is now available for $24.99 on Pine64 store together with optional sets of gross or fine soldering tips compatible with the one used with TS100 model The soldering iron is powered by GigaDevice GD32VF103TB 32-bit RISC-V general-purpose microcontroller and features a small display and two buttons for user interaction, as well as changeable tips. It can be powered by a USB-C power adapter or a 12 to 24V power brick such as the ones you’d found with laptops. PINECIL soldering iron key features and specifications: MCU – GigaDevice GD32VF103TB 32-bit RV32IMAC RISC-V “Bumblebee Core” @ 108 MHz with 128KB flash, 32KB SRAM Display – 0.69-inch OLED monochrome display with 96×16 resolution Tip – 106mm long, Type B2 Temperature range – 100°C to 400°C; reaches operating […]

BBC Doctor Who “HiFive Inventor” Coding Kit aims to teach IoT to kids

In what should be one of the first RISC-V education platforms, the BBC, Tynker, and SiFive have just announced the BBC Doctor Who “HiFive Inventor” Coding Kit that comes with an MCU board with WiFi & Bluetooth and guided lessons for kids that teach them to code for the IoT. The HiFive Inventor board is based on a SiFive FE310 RISC-V microcontroller ( the same chip as found in the HiFive1 board) and an ESP32 Solo module for WiFi 4 and Bluetooth 4.x/5.x connectivity. Just like the BBC Micro:bit, HiFive Inventor provides a kids-friendly edge connector with I/O, an LED matrix, sensors, and more. The kit includes the HiFive Inventor hardware platform, a battery holder for three AA batteries (not included), the HiFive Speakers, an illuminated USB cable for power and programming, and alligator clips to connect the speaker or other add-ons to the HiFive Inventor board. HiFive Inventor board […]

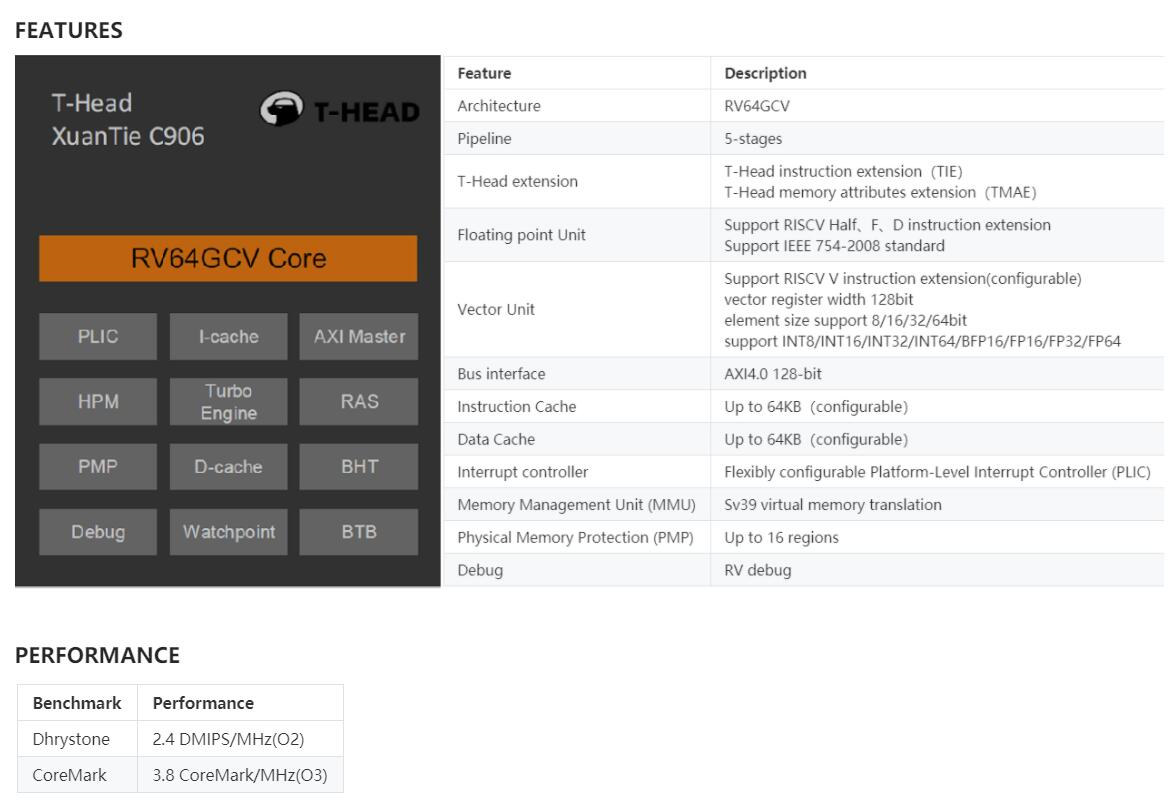

XuanTie C906 based Allwinner RISC-V processor to power $12+ Linux SBC’s

Alibaba unveiled Xuantie-910 RISC-V core (aka XT910) in 2019 for powerful SoC with up to 16 cores, but an update in 2020 revealed the company planned to have a complete RISC-V core family for a wide range of application from low-power microcontrollers to server SoCs. At the time, I just assumed the company planned to keep their cores to themselves, but time proved me wrong as T-Head, the Alibaba subsidiary in charge of developing RISC-V cores, started to cooperate with Allwinner to develop open-source processors, which should lead to low-cost Linux capable RISC-V SBC very soon according to a tweet from Sipeed. Good News: We get first chip which based on XuanTie C906 (RV64GCV), it have abundant interface (HDMI/RGB/DVP/MIPI/GMAC/…), and will be able to run Debian system.Last and most important, the basic dev board price is start at 12.5$ (1% of HiFive Unleashed)。 pic.twitter.com/EJbXTJ5eMb — Sipeed (@SipeedIO) November 6, 2020 […]

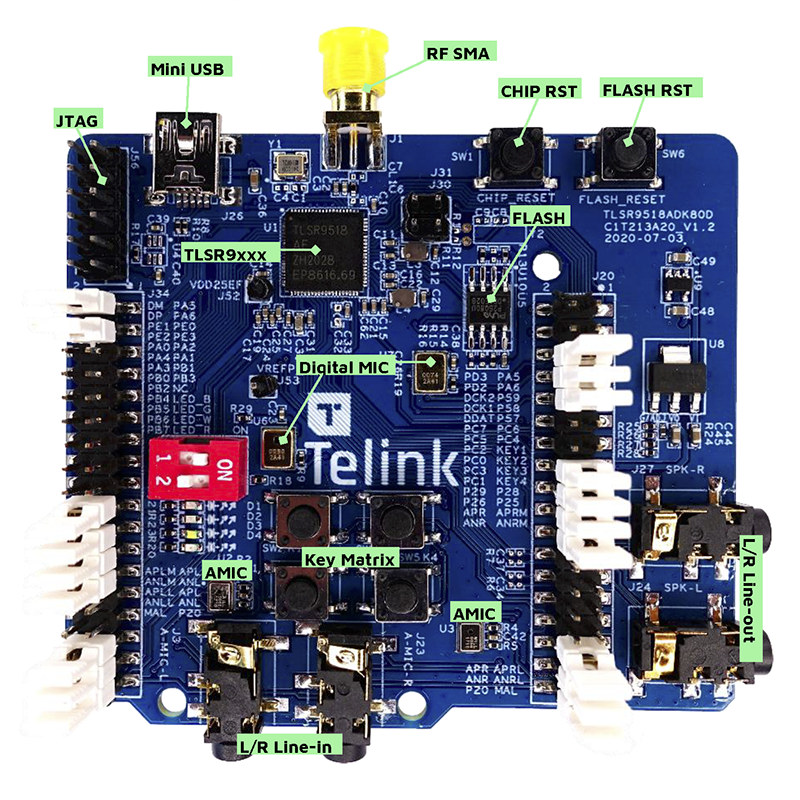

Telink TLSR9 Wireless Audio & IoT RISC-V SoC integrates RISC-V DSP/SIMD P-extension

At the end of last month, there was a lot of buzz about Bouffalo BL602, one of the first RISC-V SoC with built-in wireless connectivity, namely WiFi 4 and Bluetooth 5.0 LE. We should expect more and more of those types of solutions, and Telink & Andes jointly introduced TLSR9-series of wireless audio chips for hearables, wearables, and other high-performance IoT applications. The chips are powered by an Andes D25F RISC-V 5-stage core that happens to be the first core to integrate RISC-V DSP/SIMD P-extension and offer Bluetooth 5.2, Zigbee 3.0, HomeKit, 6LoWPAN, Thread, and/or 2.4 GHz proprietary protocol. The press release focuses on the Andes core, but an article in Chinese allows use to find more about Telink TLSR9 family’s key features: CPU – Andes D25F 32-bit RISC-V 5-stage core @ up to 96 MHz (2.59 DMIPS/MHz and 3.54 CoreMark/MHz) with RISC-V DSP/SIMD P-extension Optional NNU – AI engine […]

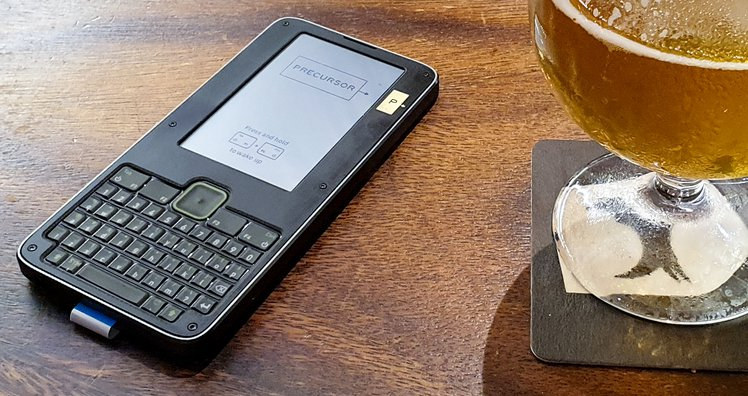

Precursor is a mobile, open hardware, dual FPGA development kit (Crowdfunding)

Sutajio Ko-usagi PTE LTD has launched some interesting hardware on Crowd Supply over the years include Novena open-source hardware Arm laptop, and Fomu FPGA USB board. The company is now back with another project: Precursor, a mobile, open-source hardware devkit powered by not one, but two FPGA with Xilinx Spartan 7-Series FPGA, plus a super-low-power Lattice iCE40 UP5K FPGA for deep-sleep system management. The device also comes with a display, battery, and keyboard that make it looks like older Palm or Blackberry phones. Precursor FPGA devkit specifications: FPGA Xilinx XC7S50 primary System on Chip (SoC) FPGA with -L1 speed grade for longer battery life; tested with 100 MHz VexRISC-V, RV32IMAC + MMU, 4k L1 I/D cache Lattice Semi iCE40UP5K secondary Embedded Controller (EC) FPGA for power, standby, and charging functions; tested with 18 MHz VexRISC-V, RV32I, no cache System Memory – 16MB external SRAM Storage – 128MB flash Display -536 […]