Pine64 community was pretty busy last year with the launch of several products. Recently I’ve received a couple of packages with some of those products, namely PinePhone Community Edition: PostmarketOS, PineCone WiFi & BLE IoT board based on BL602 RISC-V SoC, and Pinecil soldering iron also based on a RISC-V chip for control, but this time GD32V generic-purpose MCU. I’ll most show what I have received without going into too many details, except for PinePhone which I have already set up and used for one hour or so. PineCone BL602 board I received PineCone at the end of last year in a separate envelope with the board only. There’s not much to it with the BL602 processor offering WiFI and Bluetooth, a USB-C port for programming and power, and a few I/Os. The board is interesting as it is the first RISC-V IoT board with wireless connectivity built into the […]

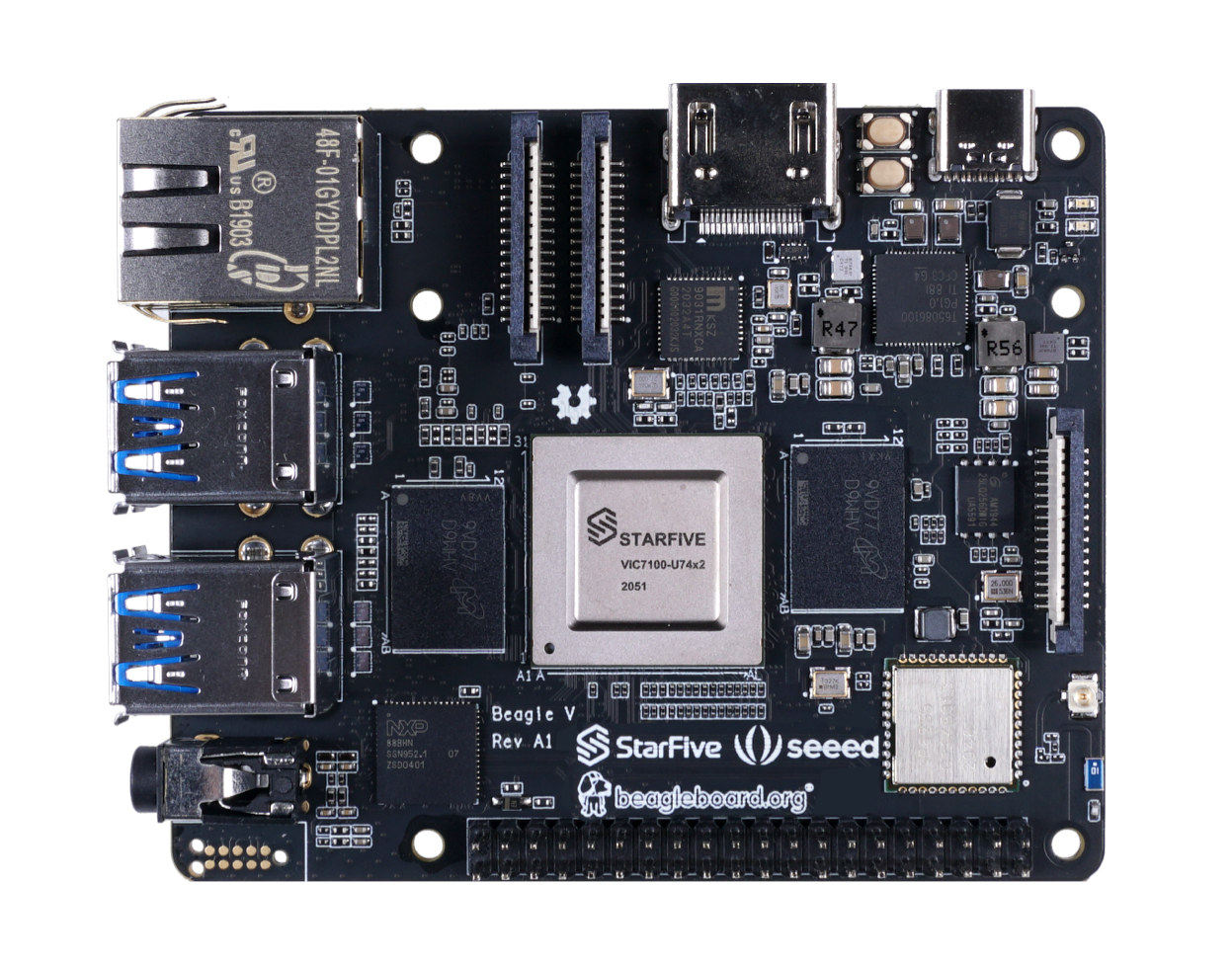

$119+ BeagleV powerful, open-hardware RISC-V Linux SBC targets AI applications

Running Linux on RISC-V hardware is already possible, but you’d have a choice of low-end platforms like Kendryte K210 that’s not really practical for anything, or higher-end board like SiFive HiFive Unmatched or PolarBerry for which you’d have to spend several hundred dollars, or even over one thousand dollars to have a complete system. So an affordable, usable RISC-V Linux SBC is clearly needed. We previously wrote about an upcoming Allwinner RISC-V Linux SBC that will be mostly useful for camera applications without 3D GPU, and a maximum of 256MB RAM. But today, we have excellent news, as the BeagleBoard.org foundation, Seeed Studio, and Chinese fabless silicon vendor Starfive partnered to design and launch the BeagleV SBC (pronounced Beagle Five) powered by StarFive JH7100 dual-core SiFive U74 RISC-V processor with Vision DSP, NVDLA engine, and neural network engine for AI acceleration. BeagleV specifications: SoC – StarFive JH7100 Vision SoC with: […]

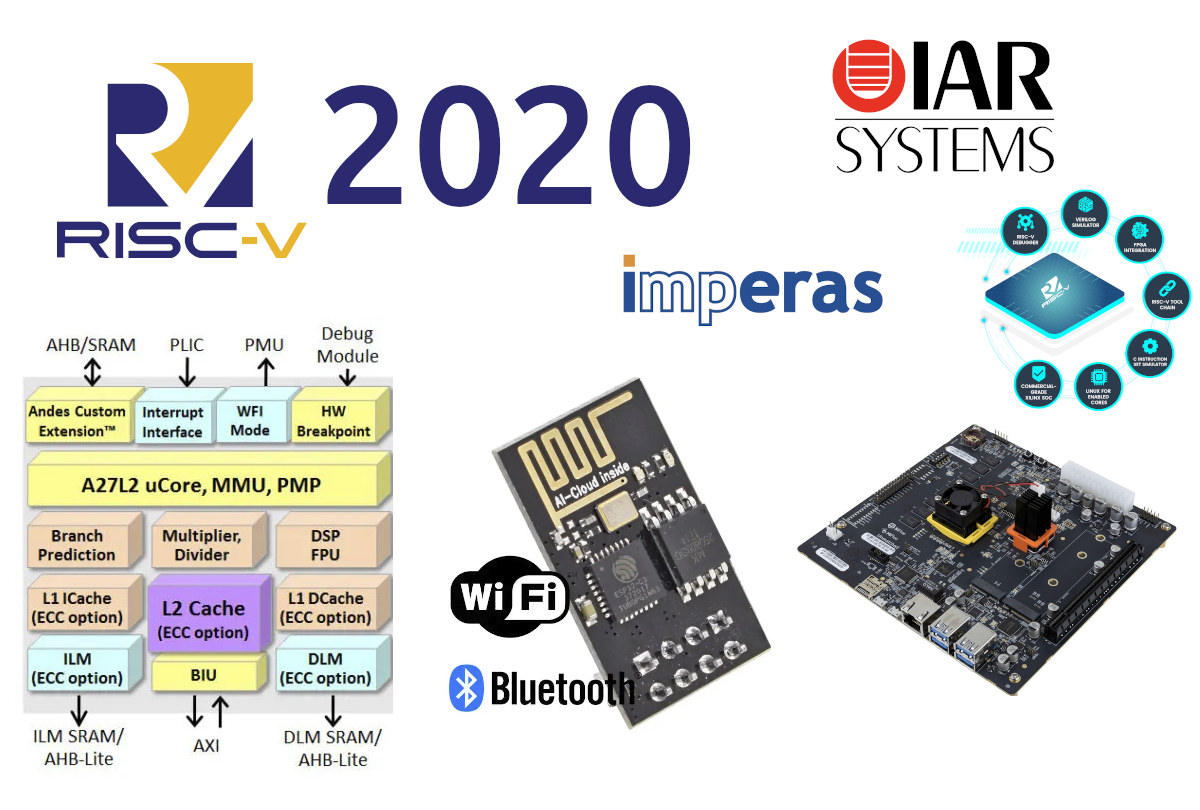

Year 2020 in review – Top ten posts and stats

It’s this time of the year when we look back at what happened, and what may be next. 2020 did not pan out as planned in more ways than one, but there were still some interesting developments. Based on 2019 announcements, 2020 was promising to be an exciting year for Amlogic and Rockchip with the expected launch of RK3588 and S908X high-end processors for 8K capable devices, but we’ll have to wait for 2021 for this to happen. Instead, the most interesting processor of the year from the Allwinner, Amlogic, and Rockchip offerings was probably Amlogic S905X4 processing adding AV1 hardware decoding. As pointed out in our “RISC-V 2020 highlights” post, it was a fairly eventful year for RISC-V architecture, although there’s still a long road ahead, especially for application processors. We had seen some general-purpose and Bluetooth RISC-V MCUs in 2019, but 2020 saw the launch of the first […]

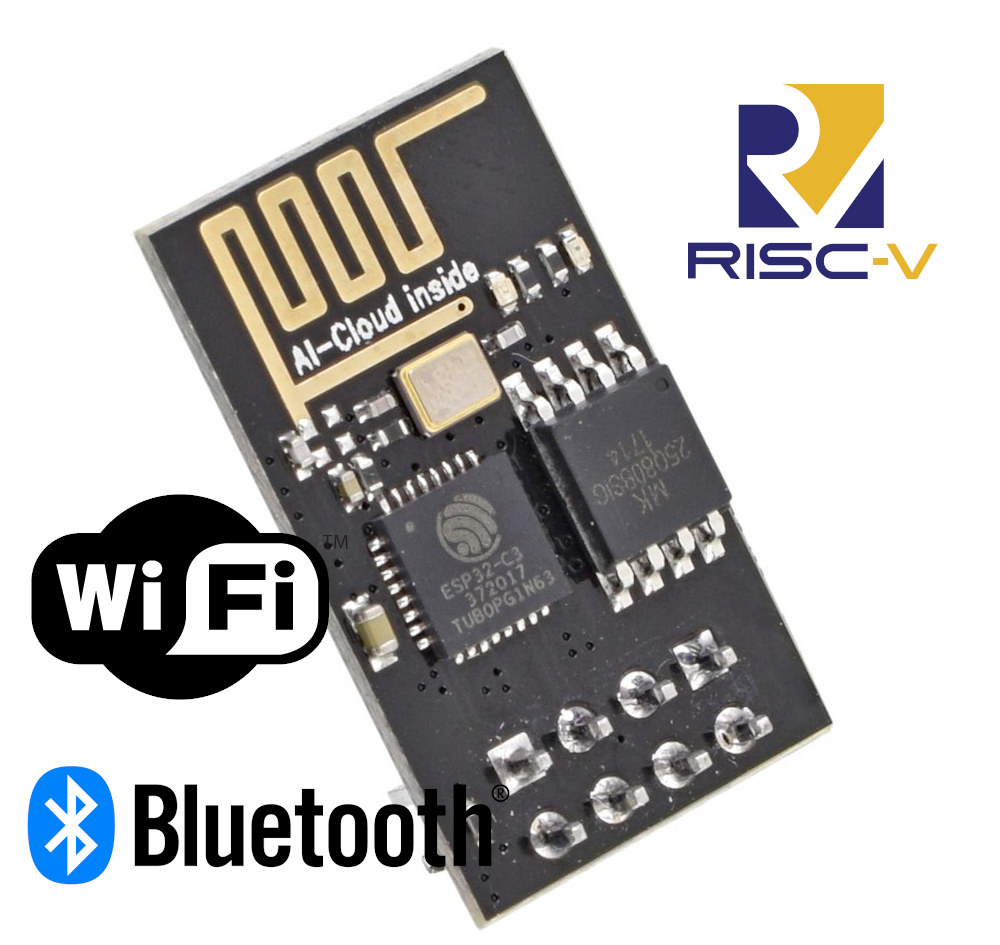

ESP32-C3 WiFi & BLE RISC-V processor to launch at ESP8266 price

[Update December 2020: While we first reported ESP32-C3 would be pin-to-pin compatible to ESP8266 based on the tweet mentioned in the post, the datasheets show both are clearly not pin-to-pin compatible, and instead it looks like the goal is to provide pin-to-pin compatible modules] When we reported about ESP32-S2-MINI modules last September, we also noted Espressif teased us with ESP32-S3 and ESP32-C3 with close to no details. ESP32-S3 is expected to be a multi-core WiFI & Bluetooth processor with AI instructions/accelerator, but there were no details about ESP32-C3 at all, and we only found out it would be a RISC-V processor several weeks ago. But Twitter user Johnny Wu posted a screenshot in Chinese and its translation claiming ESP32-C3 was finally released by Espressif Systems. [Update: The datasheet has been released. See comments.] ESP32-C3 WiSoC is pin to pin compatible with ESP8266, works with ESP32 development framework (e.g. ESP-IDF), supports […]

Cmsemicon ANT32RV56xx is a RISC-V microcontroller for wireless charging

We’ve seen RISC-V architecture used in general-purpose microcontrollers, AIoT processors, as well as WiFi and Bluetooth IoT SoC’s such as ESP32-C3 and BL602. Allwinner is also prepping a RISC-V application processor, and we’ve covered plenty of other developments in our RISC-V 2020 highlights post. But we’ve now been made aware of another application-specific RISC-V microcontroller from a Chinese fabless vendor I had never heard of. Meet Cmsemicon ANT32RV56xx RISC-V microcontroller for wireless charging applications. Cmsemicon ANT32RV56xx “tentative” key features and specifications: MCU Core – RISC-V RV32EC core @ 48MHz 32-bit hardware divider (HWDIV) Memory – Up to 32KB ILM-SRAM, up to 8KB DLM-SRAM Storage – 64KB program FLASH (APROM+BOOT), 1KB FLASH data area Peripherals Up to 46 I/Os 6x Enhanced PWM (EPWM) 1x I2C, 1x SPI/SSP, 2x UART Up to 20x 12-bit ADC up to 100Ksps Up to 20x 12-bit ADC up to 1.2 Msps Capture/compare/pulse width modulation for up […]

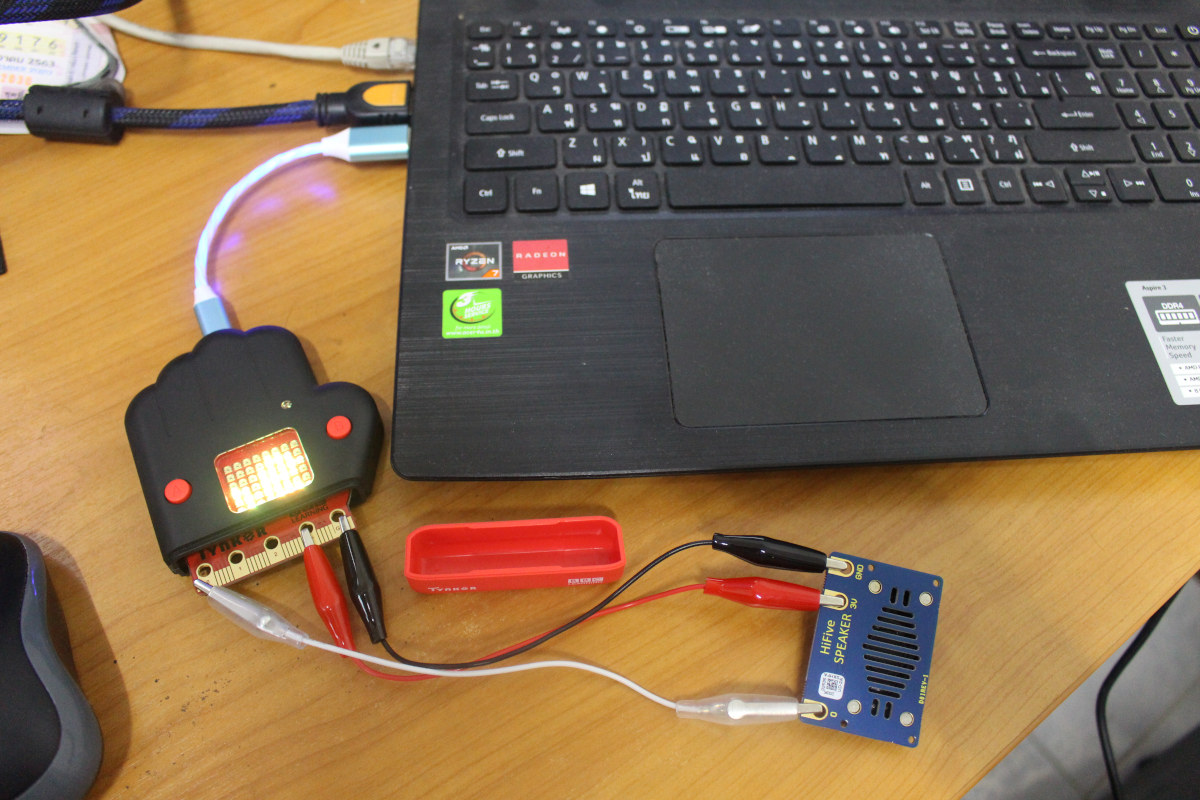

BBC Dr Who HiFive Inventor Coding Kit review – Tynker visual programing and MicroPython

The BBC Doctor Who HiFive Inventor Coding Kit was announced at the end of November 2020 with the goal of teaching IoT to young kids. But one day, I noticed the postman left a package on the ground right next to my house’s gate for some reason. I had no idea what it could be until I read it was from SiFive on the package. So here I am about to review BBC Doctor Who HiFive Inventor Coding Kit! The package actually included two small packages with one being an “expansion board”… HiFive Inventor Coding Kit Unboxing We’ve already written about the specs in the announcement post, but here they are again for those who forgot it’s based on SiFive FE310 RISC-V microcontroller and ESP32 for WiFi and Bluetooth. Let’s open the thinner “expansion board” package first. It’s actually the HiFive Inventor board – aka the mainboard – that comes […]

Linux 5.10 LTS release – Main changes, Arm, MIPS and RISC-V architectures

Linus Torvalds has just released Linux 5.10: Ok, here it is – 5.10 is tagged and pushed out. I pretty much always wish that the last week was even calmer than it was, and that’s true here too. There’s a fair amount of fixes in here, including a few last-minute reverts for things that didn’t get fixed, but nothing makes me go “we need another week”. Things look fairly normal. It’s mostly drivers – as it should be – with a smattering of fixes all over: networking, architectures, filesystems, tooling.. The shortlog is appended, and scanning it gives a good idea of what kind of things are there. Nothing that looks scary: most of the patches are very small, and the biggest one is fixing pin mapping definitions for a pincontrol driver. This also obviously means that the merge window for 5.11 will start tomorrow. I already have a couple […]

RISC-V hardware & software ecosystem highlights in 2020

The RISC-V Summit 2020 is currently taking place virtually, and RISC-V International, a non-profit corporation aiming to drive the adoption and implementation of the RISC-V instruction set architecture (ISA), took the occasion to remind us of the growth of the ISA both in terms of commercial adaption, education, and other projects. Calista Redmond, CEO of RISC-V International, detailed the growth in memberships: This year, our technical community has grown 66 percent to more than 2,300 individuals in our more than 50 technical and special interest groups. We’re seeing increased market momentum of RISC-V cores, SoCs, developer boards, software and tools across computing from embedded to enterprise … We’re proud of our growing global membership, which has more than doubled in the last year to 1,000 total members, including 222 organizations.” RISC-V also launched the RISC-V Exchange now listing over 124 RISC-V cores, SoCs, and developer boards, as well as 129 […]