[Update: Initially published on July 30th, XGO Mini Pro robot dog is now up on Kickstarter. While it was listed on the Kendryte K510 product page, it is only offered with the earlier Kendryte K210 in the crowdfunding campaign] Kendryte K510 RISC-V AI processor is the successor of Kendryte K210 with much more AI processing power (2.5/3 TOPS) that makes it suitable for robotics projects demanding much lower latency and quasi-real-time inference. One of the first products to be compatible with both Kendryte K510/K210 capabilities is Luwu Intelligence Technology’s XGO Mini Pro, a four-legged robot that looks like a dog with a tiny head providing the “smarts” for the system including face detection, image recognition, object tracking, voice recognition, and so on. We first found the description of the robot on Canaan’s website is rather short with an explanation that when equipped with is equipped with a 9-axis IMU and […]

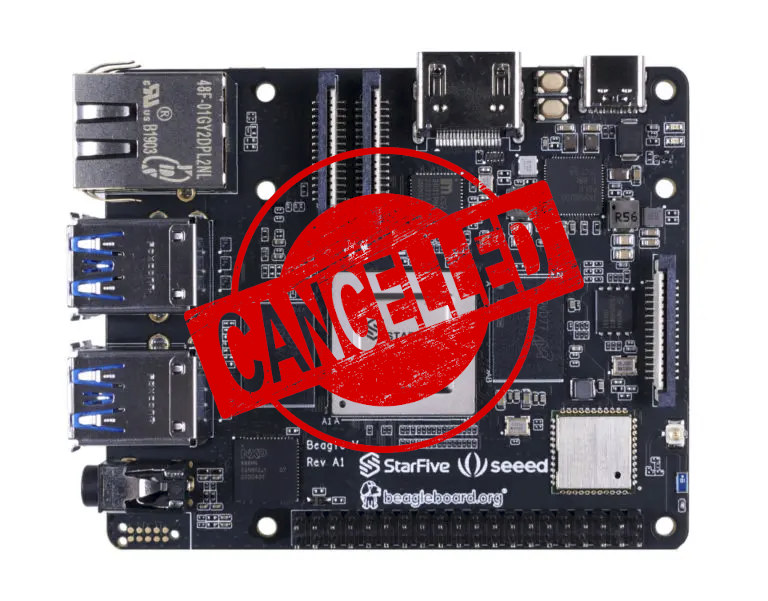

BeagleV Starlight SBC won’t be mass manufactured, redesigned BeagleV RISC-V SBC expected in Q1 2022

There was lots of excitement when BeagleV Starlight single board computer was announced in January of this year. With a price tag of $119 and up, it promises to be an affordable RISC-V SBC with StarFive JH7100 dual-core SiFive U74 Vision SoC with AI accelerator, H.265/H.264 hardware video decoding, up to 8GB RAM, HDMI output, Gigabit Ethernet, and so on. Several beta testers even received BeagleV Startlight prototypes, providing instructions for buildroot, boot Linux, or even a video review with Fedora. The first version lacked a GPU, and the initial schedule planned for a new revision with an Imagination GPU to be manufactured in September. But there have been some changes, as BeagleV Starlight SBC will not go into mass production, but not all is lost, as the Foundation and Seeed Studio are working on a new BeagleV community board slated to be released in Q1 2022. Drew Fustini made […]

Upcoming events about RISC-V, RT-Thread IoT OS, and Embedded Linux

Three events about open/open-source technologies have been recently announced with namely the RT-Thread IoT OS Tech Conference, the jointly organized Open Source Summit and Embedded Linux Conference 2021, and the 2021 RISC-V Summit. Let’s have a quick look at what each will have to offer with the list in chronological order. RT-Thread IoT OS Global Tech Conference 2021 The first-ever RT-Thread IoT OS Global Tech Conference will take place online on September 16–17,2021, be free to attend, and feature talks about embedded technologies, new projects showcase, community contributors track mostly related to RT-Thread open-source real-time operating system, but also IoT development in general. The agenda has not been published just yet, as the call for speakers is still open until August 8th. People just wanting to attend can register through a Google Docs form. Somehow there’s no landing page on the main page, and instead, they’ve decided to publish information […]

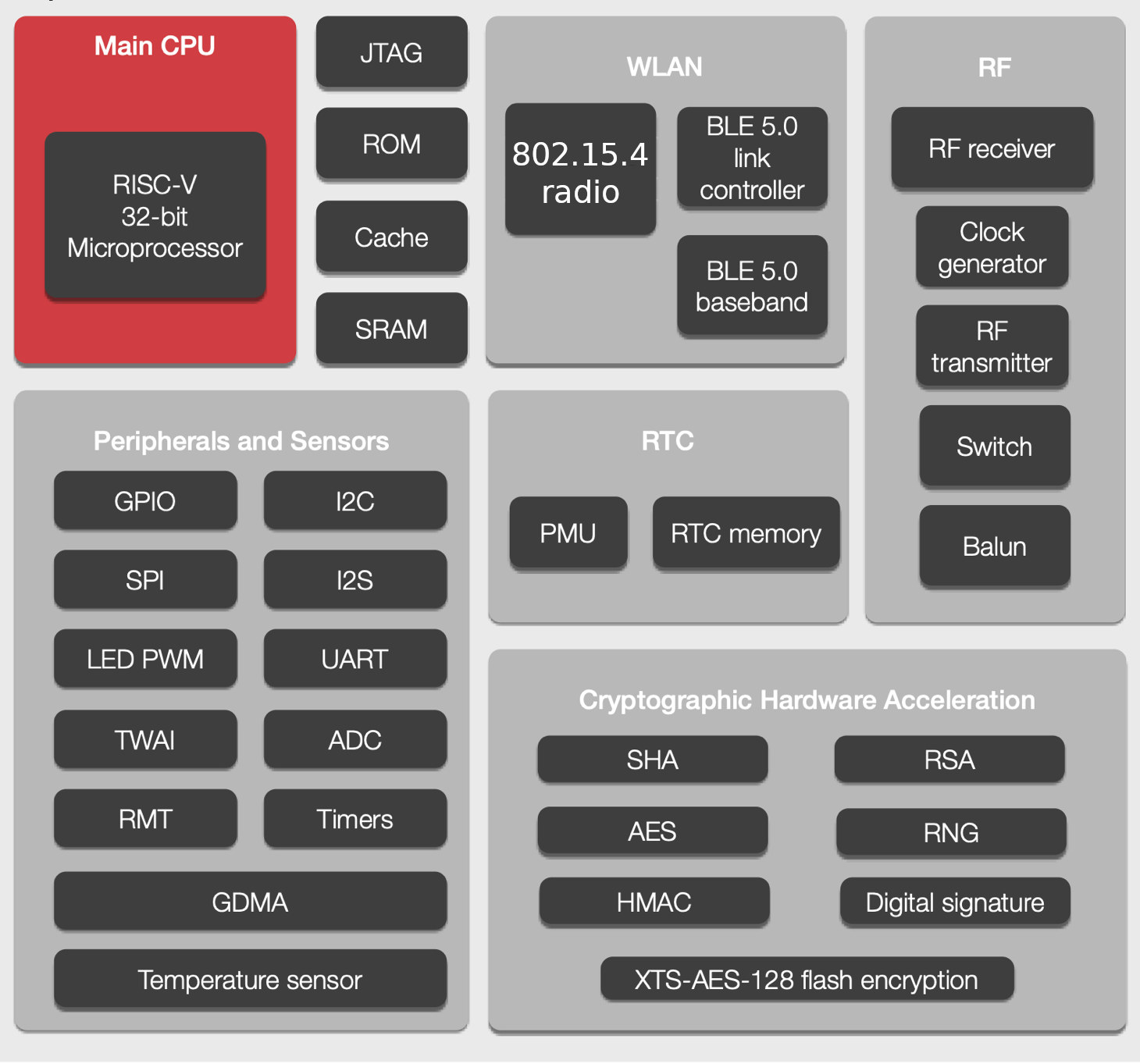

ESP32-H2 Bluetooth LE & 802.15.4 RISC-V SoC shows up in ESP-IDF source code

Espressif Systems is working on yet another RISC-V chip with ESP32-H2 SoC offering Bluetooth LE and 802.15.4 connectivity showing up in the ESP-IDF framework source code. A code comparison shows ESP32-H2 is very similar to ESP32-C3 with a single RISC-V core, albeit clocked at up to 96 MHz, and the first Espressif SoC without WiFi, as the WiFi radio is replaced with an 802.15.4 radio for Thread, Zigbee, etc… that can be used for the development of Home Automation, Smart Lighting, and wireless sensor network applications. While looking at the source code differences between ESP32-C3 and ESP32-H2, the really only major differences were the 802.15.4 radio and lower maximum frequency, and at the current time, it looks like most of the rest is unchanged, so it’s possible they kept the same amount of RAM (400KB), storage, and most of the same peripherals, but it could just well be the code […]

WARP-V: A RISC-V CPU Core Generator Supporting MIPS ISA

If you have been working on open standard RISC-V ISA CPU cores, there is a high chance that you have come across WARP-V. For newbies, WARP-V is a RISC-V CPU core generator written in TL-Verilog (Transaction-Level Verilog) that supports not only RISC-V but also MIPS ISA. WARP-V has been in discussion for a while due to its unparalleled architectural scalability in a small amount of code. The famous proverb “Necessity is the mother of invention” applies to the invention of TL-Verilog and with that this WARP-V CPU core generator. For decades, hundreds of engineers have been working on designing a single CPU core that was more complex in the race to achieve higher single-core performance. But with recent developments in the semiconductor industry, developer and engineer Steve Hoover, with decades of experience in designing CPU cores, has come up with the idea of developing a WARP-V core in just 1.5 […]

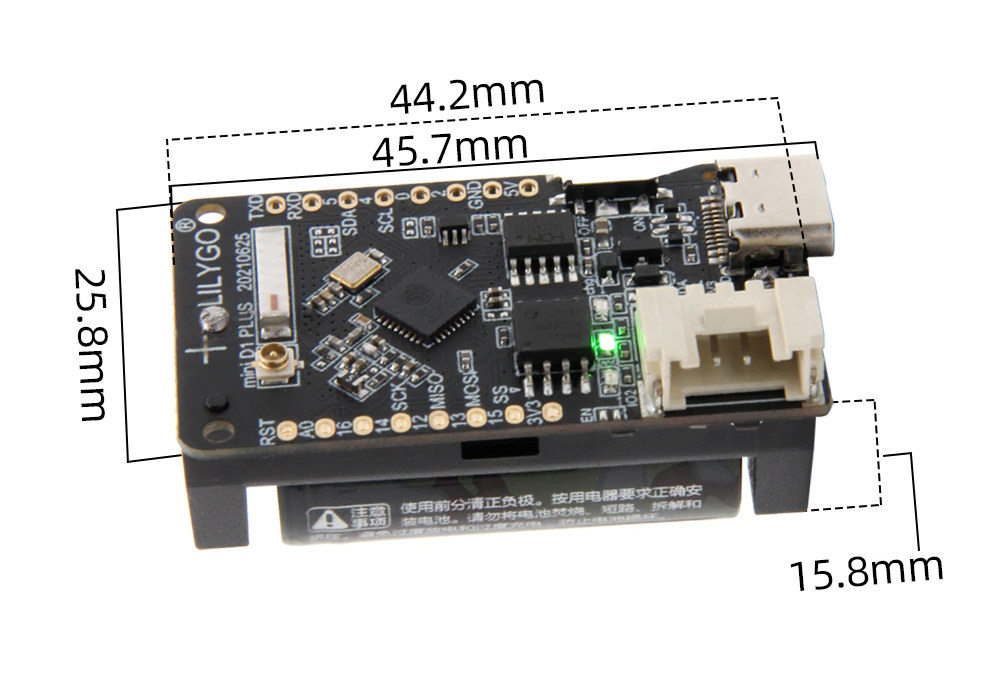

ESP32-C3 board comes with 16340 battery holder, D1 mini compatibility

It looks like ESP32-C3 floodgates have opened. We’ve just written about several NodeMCU ESP32-C3 boards, and now there’s another board with the RISC-V WiFI & Bluetooth processor. Meet LilyGo TTGO T-OI PLUS equipped with a 16340 battery holder. Getting a battery-powered ESP32-C3 board could prove to be very interesting as ESP32-C3 power consumption is much lower than ESP8266 and ESP32, notably in deep sleep mode, where the RISC-V processor consumes just 5uA, against 20 uA for ESP8266 and ESP32, and the difference is even greater in light sleep mode (ESP8266: 2000 uA vs ESP32-C3: 130 uA). LilyGo TTGO T-OI PLUS specifications: SoC – Espressif Systems ESP32-C3 single-core RISC-V processor @ 160 MHz with 2.4 GHz WiFi, Bluetooth 5.0 LE Storage – TBD flash (probably 2MB or 4MB) Antenna – Ceramic antenna and IPEX connector USB – USB-C port for power and programming Expansion 2x 8-pin headers with 12x GPIO, 1x […]

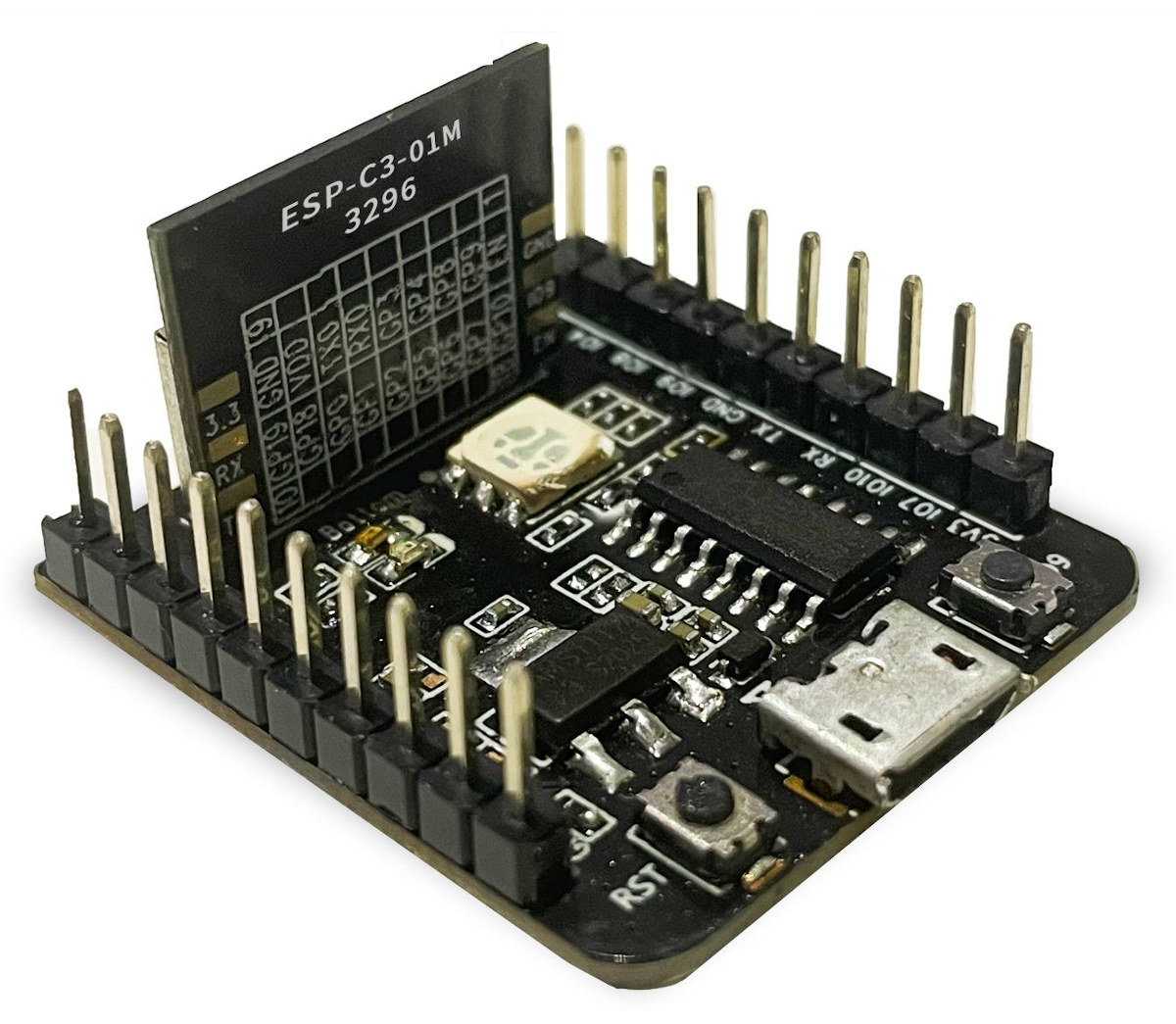

NodeMCU ESP32-C3 WiFi & BLE IoT boards show up for about $4

ESP32-C3 RISC-V IoT processor with 2.4 WiFI and Bluetooth LE 5.0 was unveiled in December 2020, and Espressif Systems’ own ESP32-C3-DevKitM-1 board has been available in limited quantities as an “engineering sample”. But now I’ve noticed third-party NodeMCU ESP32-C3 boards are being sold on Aliexpress for around $4 with ESP32-C3S_Kit and ESP-C3-01M-Kit both based on AI Thinker ESP32-C3 modules announced a few months ago. NodeMCU ESP32-C3S_KIt Specifications: Wireless module – AI Thinker ESP32-C3S (footprint compatible with ESP32-S / ESP32-WROOM-32D) with ESP32-C3 RISC-V processor @ 160 MHz, 2.4 GHz WiFi, Bluetooth 5.0 LE, 4MB flash, on-board PCB antenna, and IPEX connector (which may be soldered or not). USB – Micro USB port for power and programming via CH340C USB to TTL chip Expansion – 2x 15-pin headers with GPIO, SPI, UART, ADC, I2S, 3.3V, GND Misc – RGB LED, Reset key, user-programmable key Dimensions – 49 x 26 mm ESP32-C3S_Kit is […]

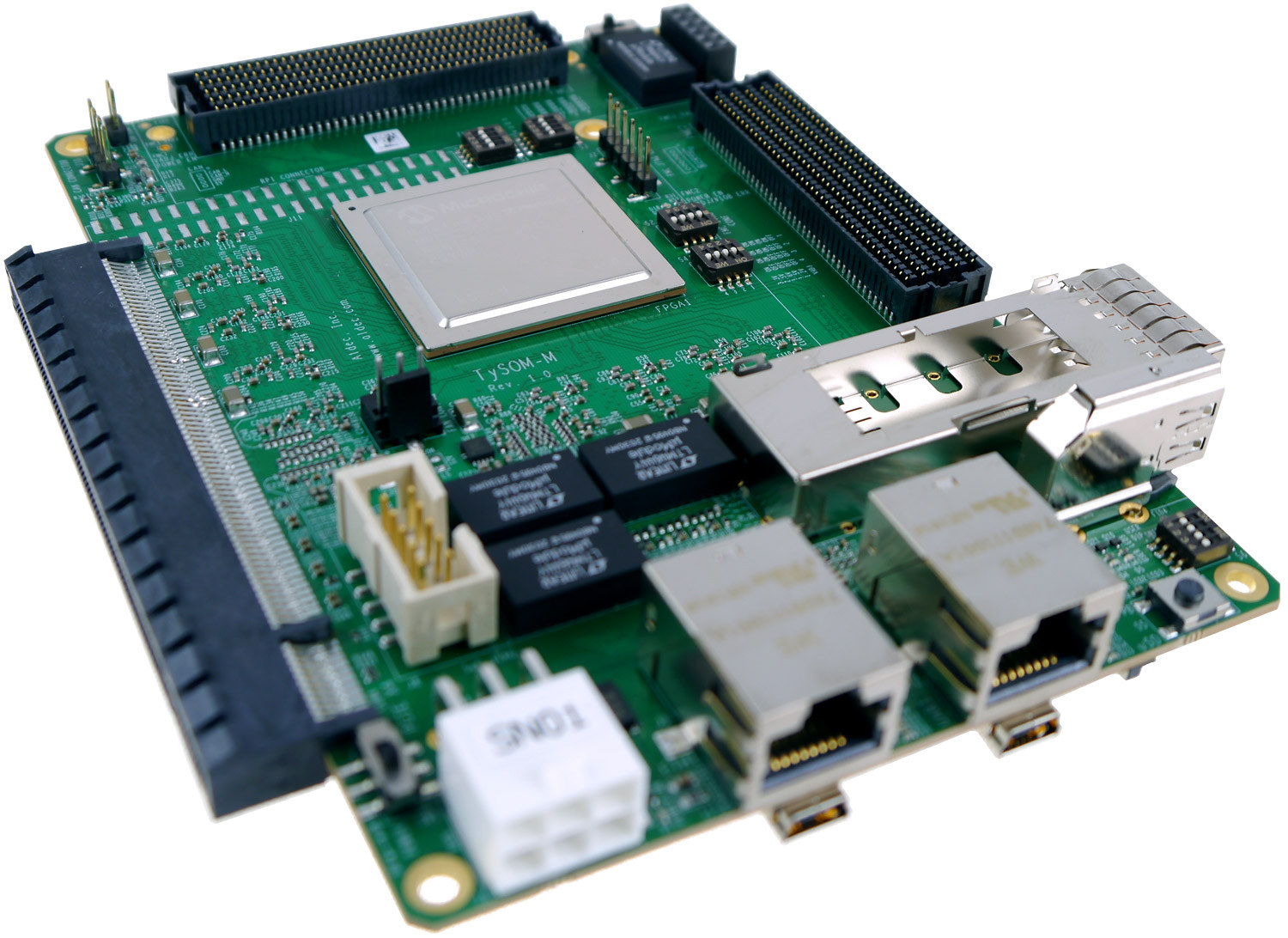

Embedded development board features Microchip PolarFire RISC-V FPGA SoC

Microchip/MicroSemi first introduced PolarFire RISC-V FPGA SoC at the end of 2018, with the chip being like the RISC-V equivalent of Xilinx Zynq Ultrascale+ Arm & FPGA MPSoC. The following year, ARIES Embedded unveiled the ARIES M100PF system-on-module and evaluation board, before Microchip launched PolarFire SoC Icicle 64-bit RISC-V and FPGA development board, followed by the more compact PolarBerry SBC in 2020. There’s now at least a fourth platform based on PolarFire SoC with Aldec TySOM-M-MPFS250 embedded development board. Aldec TySOM-M-MPFS250 specifications: SoC – Microchip PolarFire MPFS250T-FCG1152 SoC with 4x SiFive U54 RV64GC application cores (similar to Cortex-A35 performance), 1x SiFive E51 RV64IMAC monitor core, FPGA fabric with 254K logic cells, 17.6 Mb RAM System Memory 2GB (16Gbit) 32-bit DDR4 for the FPGA 2GB (16Gbit) 36-bit RAM with ECC for the RISC-V cores (aka MSS = Microprocessor Subsystem) Storage – MicroSD card socket, eMMC flash, SPI flash, 64 Kbit […]