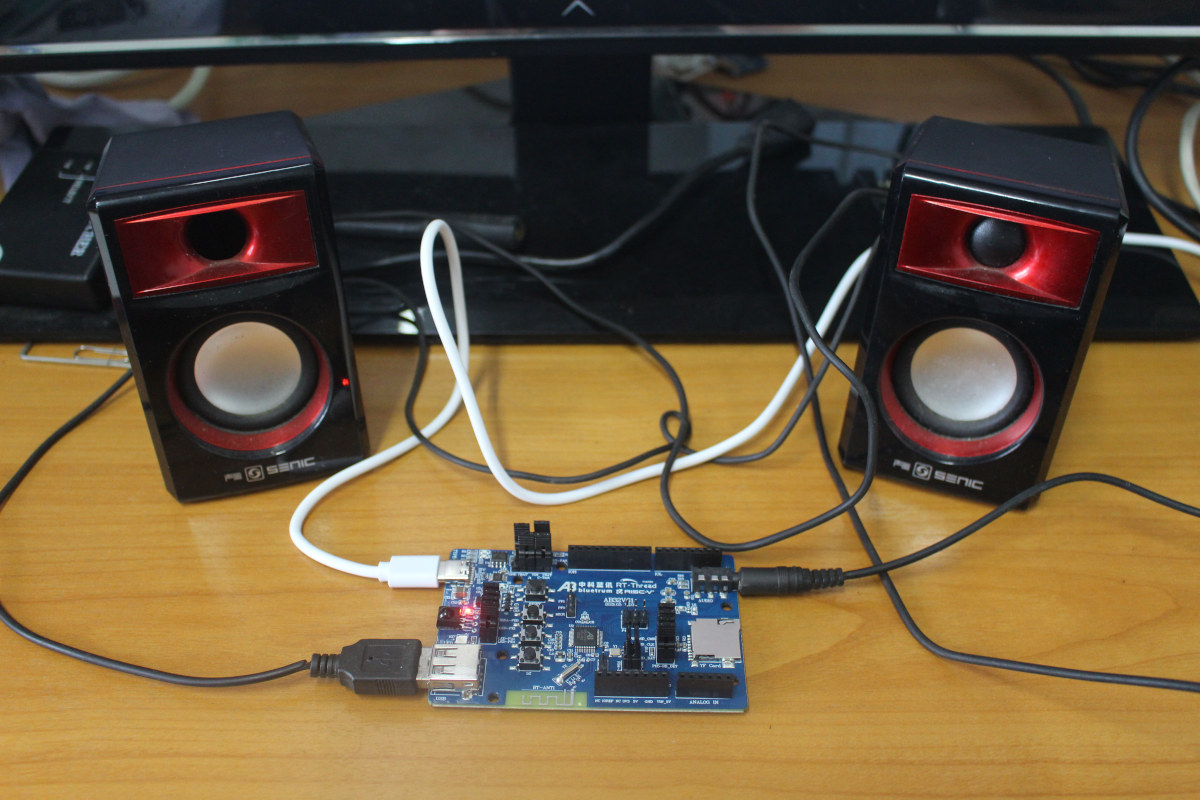

Bluetrum AB32VG1 is a development board based on AB5301A RISC-V microcontroller designed for Bluetooth audio applications as well as general-purpose projects that works with RT-Thread real-time operating system. RT-Thread sent me a board for review, and I’ll write about my experience in a getting started guide for Bluetutm AB32VG1 trying out the RT-Thread Studio IDE with the LED blink and audio samples, as there’s no Bluetooth sample at this time… Bluetrum AV32VG1 Unboxing The board ships with a USB-C cable for power and programming. It offers Arduino UNO headers for expansion, a MicroSD card slot, a USB host port, a 3.5mm audio jack, an IR receiver, and a few buttons. There’s nothing to do on the bottom of the board apart from a QR Core for the WeChat app. There are also several configuration jumpers, but I could not find any documentation about these and did not mess with the […]

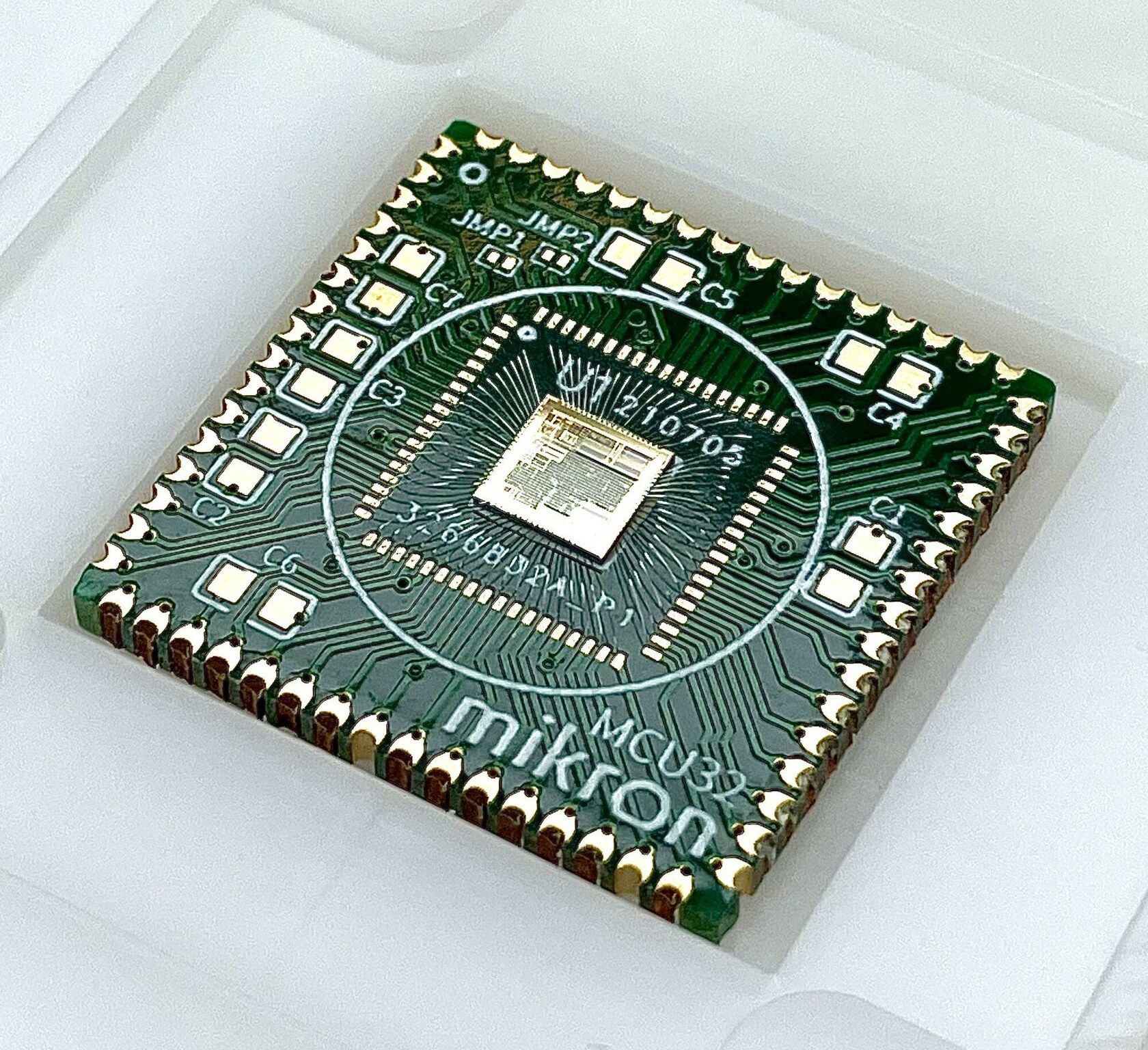

Mikron MIK32 – Made in Russia 32-bit RISC-V MCU offers features similar to STM32L0 MCU

The Mikron MIK32 is a 32-bit RISC-V microcontroller made in Russia with features similar to an STMicro STM32L0 Cortex-M0+ MCU that shows how RISC-V open-source architecture can help lower the barrier to entry, and let more companies design their own chips. The MIK32 microcontroller features CPU IP from Syntacore based in Saint Petersburg following the RV32IMC profile. Clocked at 32 MHz, the MCU comes with I2C, UART, SPI, ADC, DAC interfaces, as well as various timers, an interrupt controller, and more. Mikron MIK32 specifications: CPU Core – 32-bit RISC-V up to 32 MHz with 32 registers, embedded multiplier, debugger (TAP controller and JTAG interface), and interrupt controller Memory & Storage – 256 bytes OTP ROM, 16KB RAM, 8KB EEPROM Interfaces Storage I/F – SPI, Dual-SPI, Quad-SPI interfaces for NOR and NAND flash devices 4-channel DMA controller supporting low-power modes 2x I2C, 2x UART with synchronous mode support, 2x SPI 12-bit […]

LILYGO T-32C3 – A small ESP32-C3 WiFi & BLE IoT module with 4MB flash

We’re slowly starting to see more hardware-based on ESP32-C3 RISC-V processor, and LILYGO T-32C3 is a compact module based on the WiFi & Bluetooth LE processor that includes 4MB flash and a PCB antenna. I’d expect T-32C3 to be eventually found in the company’s smartwatches and development boards, and it joins other ESP32-C3 modules from AI Thinker. LILYGO T-32C3 module specifications: SoC – Espressif ESP32-C3 RISC-V processor @ 160 MHz with 400 KB SRAM, 384 KB ROM, 8KB RTC SRAM, 2.4 GHz WiFi 4, Bluetooth 5.0 LE & Mesh Storage – 4MB flash On-board PCB antenna I/Os – 22x castellated holes with GPIO, 3x ADC, SPI, UART, I2C, Boot, Reset, 5V, 3.3V, GND Dimensions – 23 x 11 x 3.5 mm (4-layer PCB) Note the USB interface is not listed in the specs, but USB DN and DP signals are located on GPIO18 and GPIO19 so USB should also be […]

Linux 5.14 Release – Main changes, Arm, MIPS, and RISC-V architectures

Linus Torvalds has just announced Linux 5.14 release which happens to almost coincide with the anniversary of the initial announcement of the “small” project on August 25, 1991, about 30 years ago. Here’s Linux 5.14’s announcement: So I realize you must all still be busy with all the galas and fancy balls and all the other 30th anniversary events, but at some point you must be getting tired of the constant glitz, the fireworks, and the champagne. That ball gown or tailcoat isn’t the most comfortable thing, either. The celebrations will go on for a few more weeks yet, but you all may just need a breather from them. And when that happens, I have just the thing for you – a new kernel release to test and enjoy. Because 5.14 is out there, just waiting for you to kick the tires and remind yourself what all the festivities are […]

Imagination Technologies to design RISC-V cores

Now better known for its PowerVR embedded GPUs, Imagination Technologies tried to enter the CPU market by purchasing MIPS Technologies and introducing microAptiv, interAptiv, and proAptiv cores in 2012. It did not end up well, as the company had to sell its MIPS technology a few years later, and the MIPS architecture is now barely supported. But Imagination is now working on getting back into the CPU space by designing RISC-V cores. At least that’s what the company revealed in a press release also announcing overall revenues increased by 55% to $76m in H1 2021, with $70m in cash, and no external third-party debt. This year Imagination is re-entering the CPU market with designs based around the RISC-V open ISA. Imagination’s heritage in CPU enables it to provide innovative and patent protected technologies for the discrete CPU market as well as addressing demand for heterogeneous solutions that combine GPU, CPU […]

Ultra-Low-Power RISC-V System-on-Chip features Adaptive Body Biasing Technology

CSEM and USJC together have developed an ultra-low-power RISC-V chip for electronic gadgets such as wearables. The semiconductor companies, from Switzerland and Japan respectively, have been in the market for a while, developing technologies for low-power chips. Their latest collaboration uses Adaptive Body Biasing (ABB) and Deeply Depleted Channel (DDC) to build an ultra-low-power RISC-V chip with all the required and necessary components. Originating from the labs of CSEM, the Adaptive Body Biasing dwells into the operating efficiency of all the modes of ON, Standby, and OFF. There has been the problem of power leakage in Standby and OFF operating modes, but the Adaptive Body Biasing technology helps design to minimize power leakage when the processor is not operating while keeping the best performance in ON mode. For most of the designs, the processor is in Standby mode waiting for the incoming data or the next event to be offered. […]

The RISC-V Platform Specification aims to ensure RISC-V hardware and software compatibility

The RISC-V platform specification aims to define a set of rules to make sure operating systems like Linux or the Zephyr Project can boot properly on all RISC-V hardware compliant with the specs. If you’ve ever worked with the Arm Linux kernel over ten years ago, you may remember board files, which were replaced by device tree bindings, and eventually, Arm defined several standards culminating with Arm SystemReady certifications allowing compliant Arm platforms to boot off-the-shelf OS images like in the x86 world. While we are probably a long way from a “RISC-V SystemReady” platform certification program, the RISC-V platform specification is currently being worked on to define requirements for two types of platforms with optional extensions: OS-A Platform: This specifies a rich-OS platform for Linux/FreeBSD/Windows…flavors that run on enterprise and embedded class application processors. Current extension: Server Extension M Platform – This specifies an RTOS platform for bare-metal applications […]

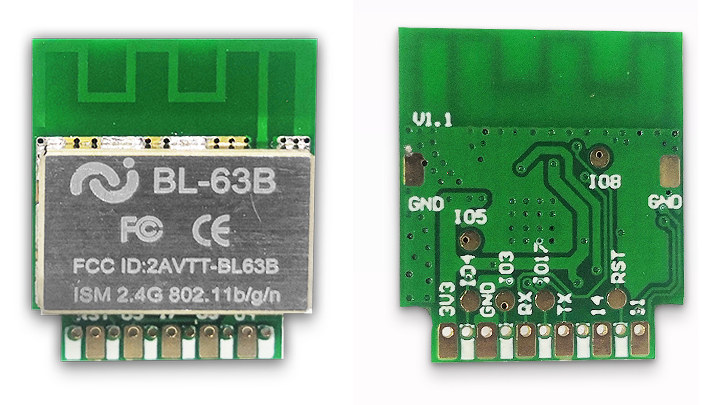

BL-63B – A smaller BL602 IoT module that sells for $1.5

Bouffalo Labs BL602 is a low-cost, low-power RISC-V microcontroller that offers 2.4 GHz WiFi and Bluetooth 5.0 LE connectivity for IoT projects for about the price of ESP8266. We first discovered it last year, together with a development board. Pine64 created its own PineCone board fitted with the $2 PineNut module, and some reverse-engineering work has started on BL602 SDK. But there’s now another smaller BL602 module with “Machine Intelligence” (that’s the company name) BL-63B that sells for $1.5 on Taobao in China, as well as on LCSC Electronics albeit you’d need to purchase 1000 pieces to get that price, and single-unit pricing is currently $2.5. BL-63B WiFI & BLE module specifications: SoC – Bouffalo Labs BL602 32-bit RISC-V processor @ up to 192 Mhz with 276KB RAM, 128KB ROM, 1Kbit eFuse, WiFi and BLE Storage – 2MB flash Wireless 2.4GHz 802.11b/g/n WiFI 4 1×1 SISO up to 65 Mbps […]