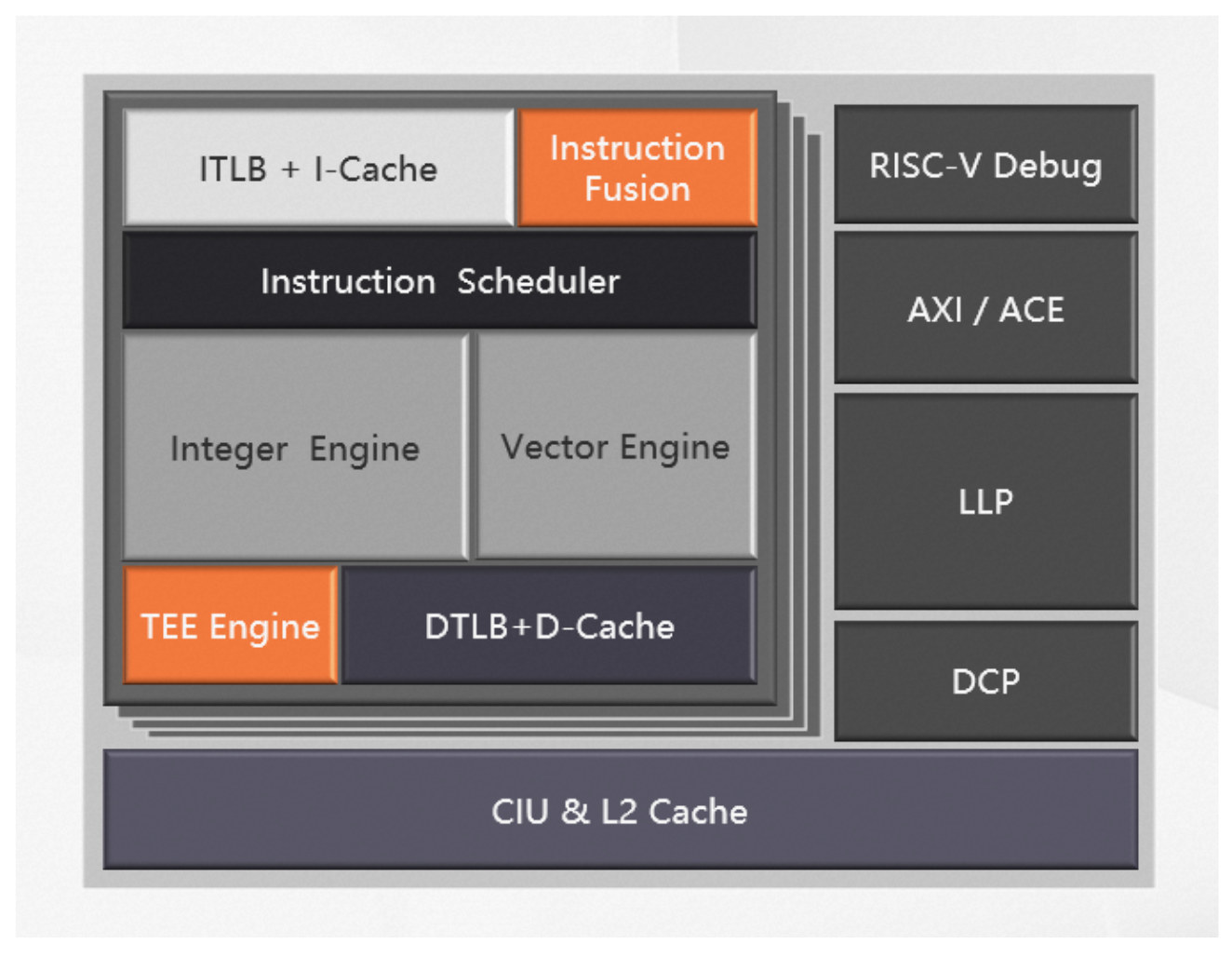

We’ve seen two announcements of high-end RISC-V cores this week with the SiFive P670 and Andes AX65 processors each with a 4-way out-of-order pipeline, but Alibaba’s T-Head Semiconductor Xuantie C908 is a little different with a dual-issued, 9-stage in-order pipeline and support for the RISC-V Vector extension acceleration targeting mid-range AIoT applications. The C908 64-bit RISC-V core adopts the RV64GCB[V] instruction and complies with the RVA22 profile for better compatibility with Android and other “rich” operating systems. The company says its performance is between the C906 and C910 cores introduced in 2020 and 2019 respectively. XuanTie C908 highlights: RV32GCB[V] 32-bit and RV64GCB[V] 64-bit RISC-V architectures with Bit manipulation and (optional) Vector operations extensions Support for RV32 COMPAT mode which allows for 64-bit RISC-V CPUs to run 32-bit binary code, and was merged into Linux 5.19. XuanTie extensions, including Instruction, Memory Attributes Extension (XMAE). RVA22 profile compatibility Cluster of 1 to […]

Andes unveils AndesCore AX65 Out-of-Order RISC-V core for compute intensive applications

Andes Technology has unveiled the high-end AndesCore AX60 series out-of-order 64-bit RISC-V processors at the Linley Fall Processor Conference 2022 with the new cores designed for compute-intensive applications such as advanced driver-assistance systems (ADAS), artificial intelligence, augmented/virtual reality, datacenter accelerators, 5G infrastructure, high-speed networking, and enterprise storage. AndesCore AX65 is the first member of the family and supports RISC-V scalar cryptography extension and bit manipulation extension. It is a 4-way superscalar core with Out-of-Order (OoO) execution in a 13-stage pipeline and can fetch 4 to 8 instructions per cycle. The company further explains the AX65 core then decodes, renames, and dispatches up to 4 instructions into 8 execution units, including 4 integer units, 2 full load/store units, and 2 floating-point units. The AX65’s memory subsystem also includes split 2-level TLBs (translation lookaside buffers) with up to 64 outstanding load/store instructions. Up to eight AX65 cores (or should that then be […]

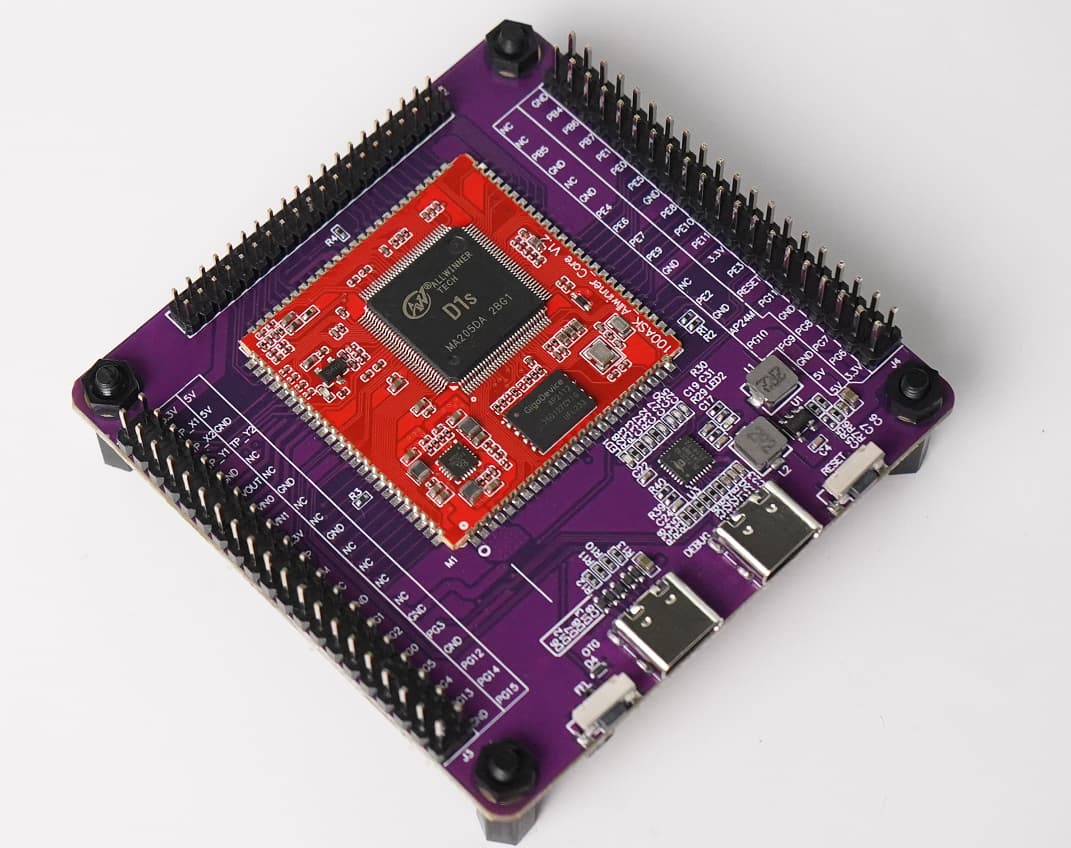

DongshanPI-D1s – An Allwinner D1s RISC-V development board designed to teach programming

The DongshanPI-D1s development board is comprised of a soldered-on Allwinner D1s RISC-V system-on-module board (SoM) and a carrier board with two 40-pin headers and a 2.0mm dedicated header. This development board is specifically designed to teach programming with a focus on the RISC-V architecture. The development board was designed by 100ask. They previously designed the Dongshan NeZha STU a development board based on the Allwinner D1. The main difference between the two is that 100ask did not include the Ethernet and HDMI interfaces on the DongshanPI-D1s board. The pinout of the headers is also slightly different because they opted to make the headers compatible with the widely used 40-pin GPIO from Raspberry Pi single board computers. DongshanPI-D1s preliminary specifications: D1s Core Lite SoC – Allwinner D1s single-core XuanTie C906 64-bit RISC-V processor @ 1.0 GHz with with 32 KB I-cache + 32 KB D-cache Memory – 64 MB DDR2 (SIP) […]

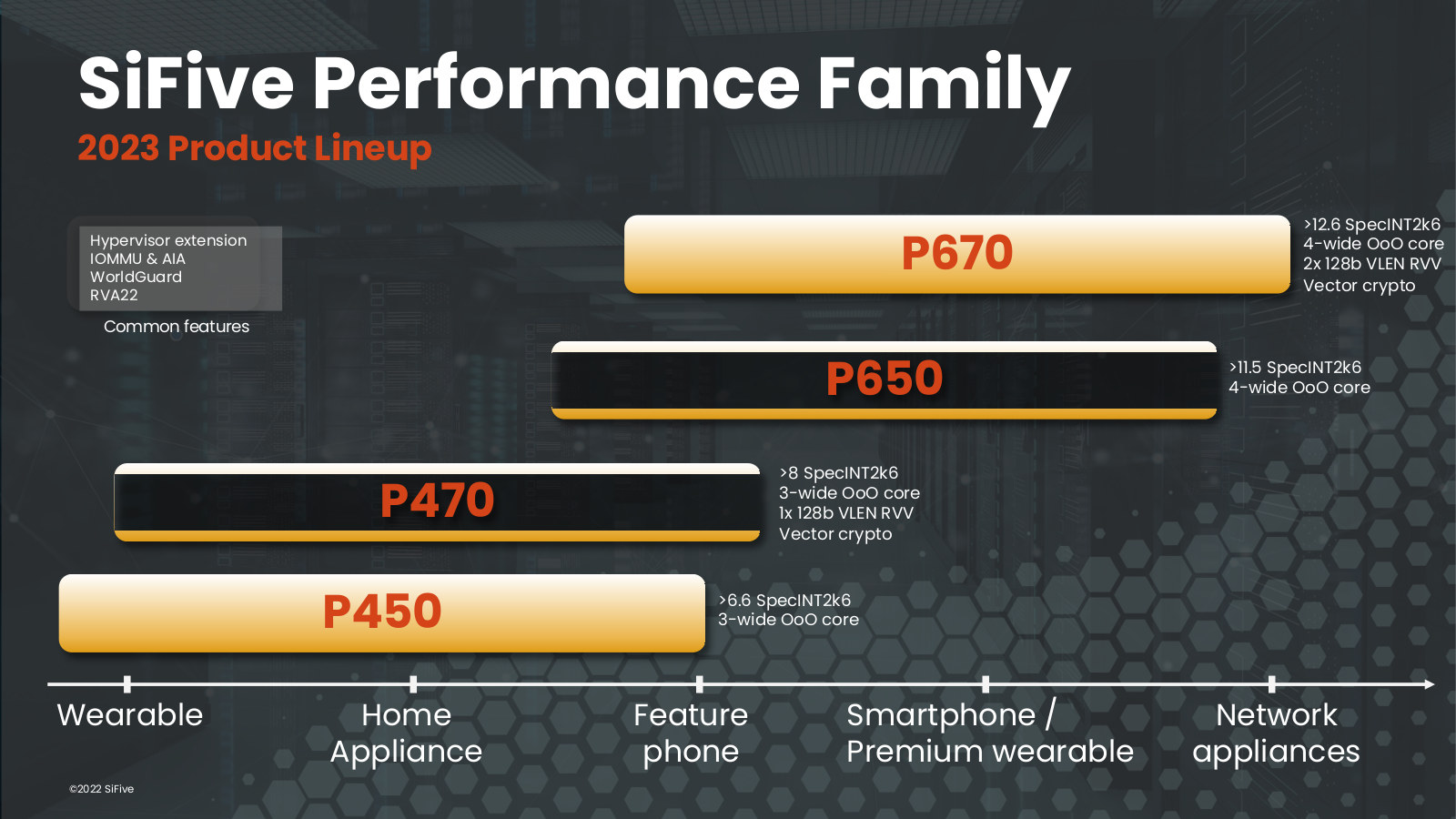

SiFive P670 and P470 RISC-V processors feature RISC-V Vector Extensions

SiFive has announced two new RISC-V Performance cores with the P670 and P470 processors with RISC-V Vector Extension for AI/ML, media and sensor processing, and designed for high volume applications such as wearables, smart home, industrial automation, AR/VR, and other consumer devices. The P670 is comparable to the Cortex-A78, and the P470 is comparable to the Cortex-A55. Both support the standardized RISC-V RVA22 profile for better OS compatibility and implement RISC-V Vector v1.0 and Vector Cryptography extensions. The SiFive Performance P470 and P670 share the following features: Full RISC-V RVA22 profile compliance Full, Out-of-Order, RISC-V Vector implementation, based on the ratified RISC-V Vector v1.0 Specification RISC-V Vector Cryptography extensions SiFive WorldGuard system security Support for virtualization, including a separate IOMMU for accelerating virtualized device IO Advanced Interrupt Architecture (AIA) compliant interrupt controller with better support for Message Signal Interrupts (MSI) and virtualization Enhanced scalability with fully coherent multi-core, multi-cluster, with […]

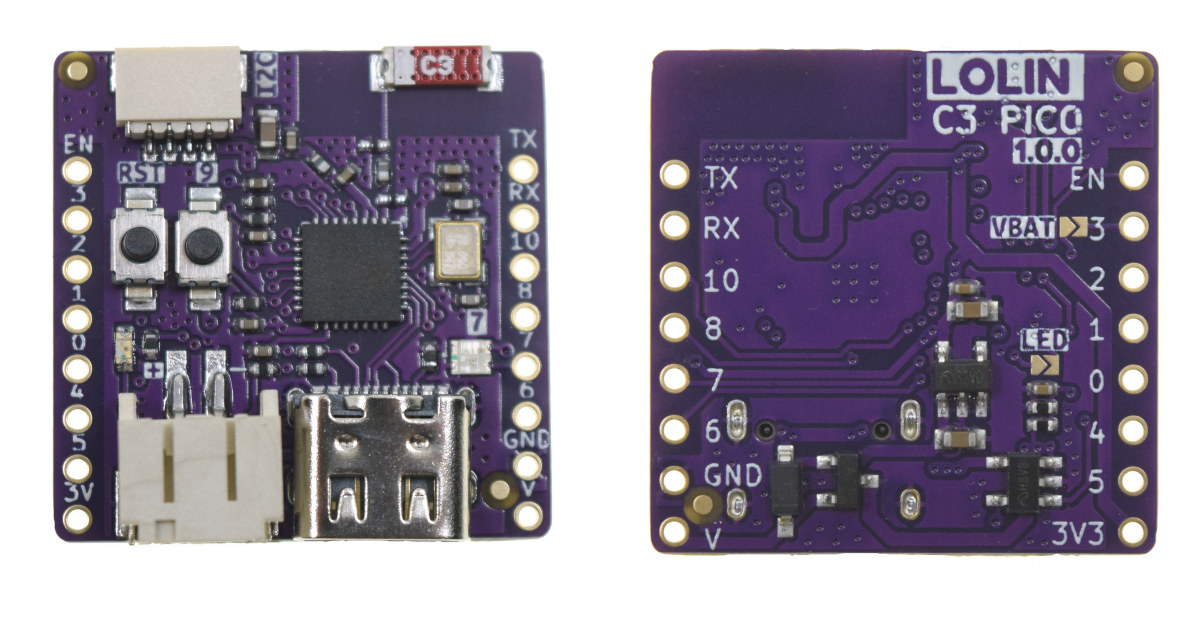

LOLIN C3 Pico is a tiny ESP32-C3 board with battery charging support

LOLIN C3 Pico is a tiny (25.4×25.4mm) ESP32-C3 RISC-V board with 2.4 GHz WiFi and Bluetooth Low Energy connectivity, a few I/Os, and LiPo battery support including charging circuitry. I tend to like Wemos/LOLIN boards, because of their small form factor, support for equally tiny shields, and low price. The LOLIN C3 Pico is no exception, and even adds a few features such as an RGB LED, an I2C connector, and support for battery power and charging. LOLIN C3 Pico specifications: SoC – Espressif Systems ESP32-C3FH4 single-core 32-bit RISC-V (RV32IMC) microcontroller up to 160 MHz with 400 KB SRAM, 4MB Flash Connectivity – 2.4 GHz WiFi 4 and Bluetooth 5.0 LE (in SoC) Expansion headers 2x 8-pin headers with up to 12x GPIO, ADC, I2C, SPI, UART (3.3V I/O voltage) LOLIN I2C port USB – 1x Type-C USB for 5V power and programming Misc – Reset button and user button, […]

uConsole is a modular Arm or RISC-V handheld computer with optional 4G connectivity

Clockwork’s uConsole is a modular handheld computer with a 5-inch display, a built-in keyboard, and based on a carrier board supporting various Arm or RISC-V modules compatible with the Raspberry Pi CM3 or CM4 form factors. The device is offered with a system-on-module with up to 4GB RAM, a WiFi 5 and Bluetooth 5.0 wireless module, features micro HDMI video output, USB ports, and an audio jack, plus expansion connectors for more advanced users, and takes two 18650 batteries for power. The company also offers a 4G LTE module for cellular connectivity. The mainboard, called ClockworkPi v3.14 revision 5, offers the following: System-on-module socket – 200-pin DDR2 SODIMM socket compatible with Raspberry Pi CM3 and, through an adapter, Raspberry Pi CM4 and compatible modules Storage – MicroSD card socket Video Interfaces 40-pin MIPI DSI connector micro HDMI interface for external display Audio – 3.5mm audio jack with headphone and microphone […]

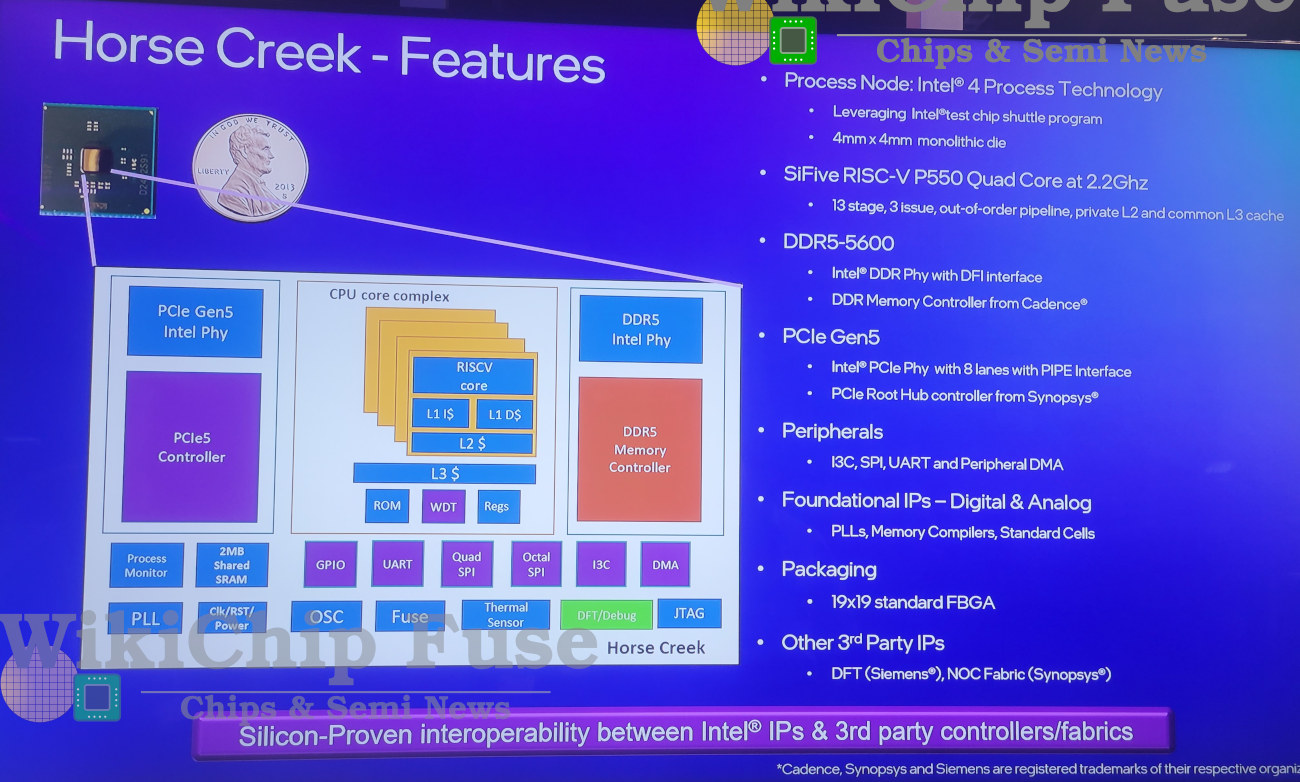

Intel Horse Creek platform showcased with SiFive P550 RISC-V CPU, 8GB DDR5, PCIe Gen5

When SiFive introduced its Performance P550 64-bit RISC-V processor in 2021, we were told that Intel would use it in the Horse Creek platform with “leading-edge interface IP such as DDR and PCIe” and manufactured with Intel’s 7nm process. We now have more details about the Horse Creek platform, as a development board was showcased for the first time in public at the Intel Innovation 2022 Developer Conference, and according to a report by Wikichip, the Cortex-A75 class quad-core RISC-V processor runs at up to 2.2 GHz, supports DDR5-5600 memory and eight PCIe 5.0 lanes, and was taped out with Intel 4 process. Horse Creek platform specifications: CPU – SiFive P500 quad-core RISC-V processor @ up to 2.2 GHz with a 13-stage, 3-issue, out-of-order (OoO) pipeline, private L2 cache, and common L3 cache Memory – DDR5-5600 interface PCIe – PCIe Gen5 through Intel’s PCIe PHY with 8 lanes, Synopsys PCIe […]

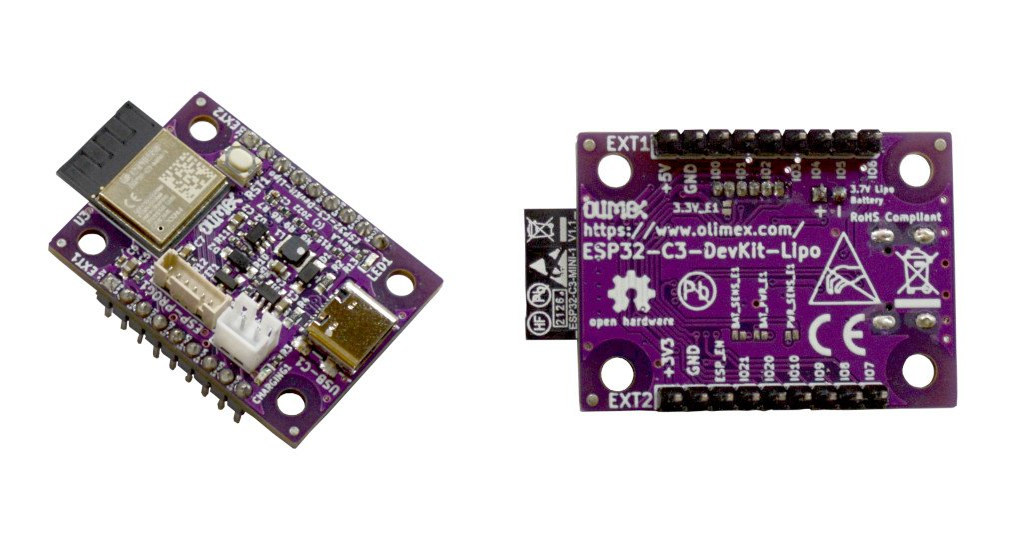

Olimex ESP32-C3-DevKit-Lipo is a tiny RISC-V board with WiFi 4, Bluetooth 5.0, and a LiPo battery charger

Olimex has just launched the ESP32-C3-DevKit-Lipo board based on ESP32-C3 RISC-V wireless microcontroller offering WiFI 4 and Bluetooth 5.0 connectivity, some I/Os, as well as USB and JTAG. As its name implies, the board can be powered by a LiPo battery and charged through a USB Type-C port. It offers up to 15 GPIO for expansion and comes with an ICSP connector in case you need to reflash or debug the bootloader through a JTAG interface. ESP32-C3-DevKit-Lipo specifications: Wireless module – Espressif Systems ESP32-C3-MINI-1-N4 module with: ESP32-C3 (ESP32-C3FN4) 32-bit RISC-V single-core processor up to 160 MHz with 4 MB embedded flash, 384 KB ROM, 400 KB SRAM (16 KB for cache), 8 KB SRAM in RTC Connectivity – 2.4 GHz 802.11b/g/n Wi-Fi 4 1T1R up to 150 Mbps & Bluetooth LE 5.0 with PCB antenna USB – 1x USB Type-C port for programming and JTAG debugging Expansion – 2x 9-pin […]