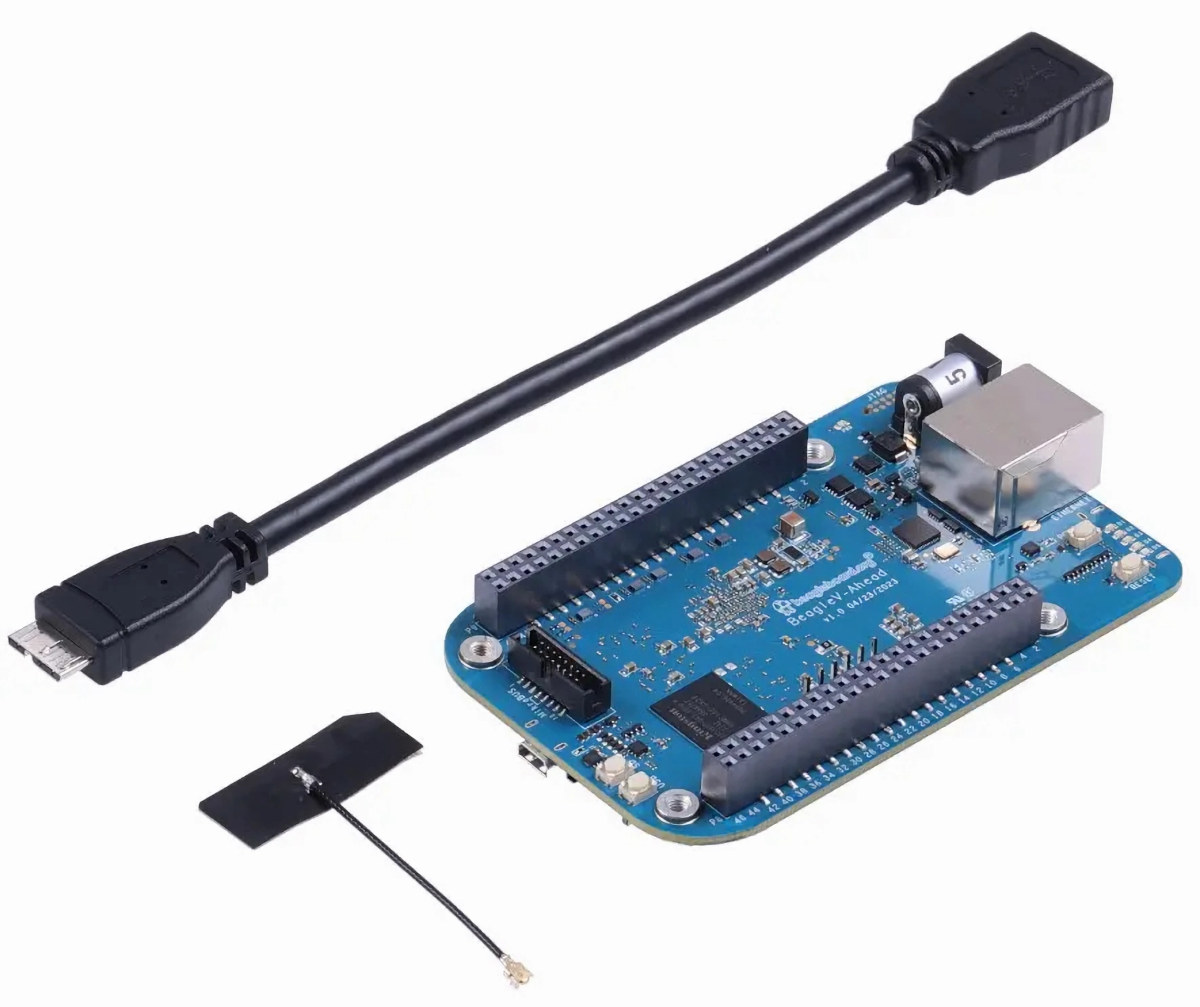

Beagleboard.org Foundation’s BeagleV-Ahead is a single board computer powered by the T-Head TH1520 quad-core RISC-V processor and following the form factor of the popular BeagleBone Black board based on a Texas Instruments Sitara AM3359 single-core Arm Cortex-A8 processor. The new board looks better in almost every way with a much faster processor, 4GB RAM, 16GB eMMC flash, Gigabit Ethernet, built-in WiFI and Bluetooth, a micro USB 3.0 port, micro HDMI video output up to 4Kp60, etc… and the same 80-pin headers as found on other BeagleBone boards. The main downside is that it comes at a significantly higher price as we’ll see further below. BeagleV-Ahead specifications: SoC – Alibaba T-Head TH1520 CPU – quad-core RISC-V Xuantie C910 (RV64GCV) processor @ up to 2.0 GHz, low power Xuantie E902 core GPU – Imagination BXM-4-64 GPU with OpenGL ES 3.2, OpenCL 2.0, Vulkan 1.2, 50.7GFLOPS DSP – Xuantie C906 audio DSP @ […]

UniHiker review – A Linux-based STEM education platform with IoT and AI support, Micro:bit edge connector

DFRobot’s UniHiker is a STEM educational platform that was originally launched in China, but now UniHiker is now available worldwide through the DFRobot shop. The company has sent us a UniHiker sample for review, so let’s unpack the kit and learn how to use the UniHiker platform. The main component of the kit is the Linux-powered UniHiker board which features a 2.8-inch resistive touchscreen display and a BBC Micro:bit edge connector, so we can use expansion boards for the Micro:bit board. Let’s start unboxing it together. UniHiker unboxing DFRobot sent us the UniHiker platform by DHL. The package is a familiar-looking DFRobot box in orange color and comes with a plastic box to safely store the UniHiker board and accessories after use. The plastic box contains another plastic box with the board, some 3-pin and 4-pin cables for Gravity ports, and a USB Type-C cable. The UniHiker is like a […]

LicheePi 4A RISC-V SBC gets 16GB/128GB version, metal enclosure, 10.1-inch display, and more accessories

LicheePi 4A quad-core RISC-V SBC is now available with 16GB RAM and 128GB eMMC flash, and Sipeed has also introduced various accessories such as a metal enclosure, a 10.1-inch touchscreen display, a PoE module, and a camera module. The Lichee Pi 4A board was first unveiled in December 2022, before the beta version launched in May 2023 with 8GB RAM and 8GB flash. Since then Sipeed also started selling an 8GB/32GB model, and now a new version of the T-Head TH1520-powered single board computer is now available with 16GB LPDDR4X and 128GB eMMC flash for $179 plus shipping. LicheePi 4A SBC While pricing is quite different, the LicheePi 4A was launched as a RISC-V alternative to the Raspberry Pi 4 SBC, so here are the specifications of the two boards side-by-side. Sipeed currently provides a Debian image based on Linux 5.10 and built with Yocto, but Linux mainline support is […]

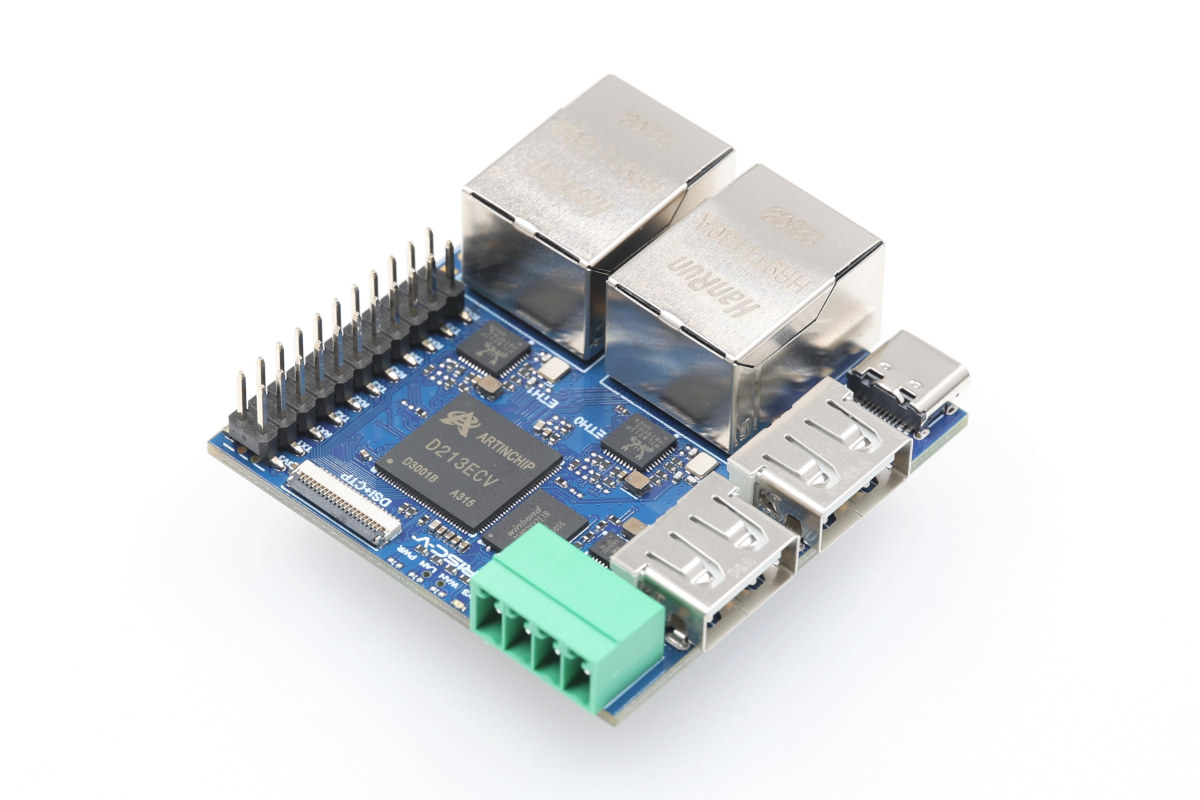

MangoPi MPi-GW1 RISC-V router will support dual GbE, dual USB 2.0, CAN bus, RS485, and more

MangoPi is working on the first RISC-V router I’ve seen. The MPi-GW1 is based on the ArtInChip D213ECV 64-bit RISC-V processor with 128 MB DDR3 on-chip, 256MB SPI NAND flash, two Gigabit Ethernet ports, two USB 2.0 ports, MIPI DSI+touch connector, support for CAN Bus and RS485, and expansion through a 22-pin GPIO header. Routers used to be mostly based on MIPS processors, then Arm processors took over, and maybe RISC-V is next, as MangoPi has just unveiled photos of the first RISC-V router on Twitter, and leaked some tidbits of information over the last two weeks or so on the social media platform. MangoPi MPi-GW1 RISC-V router specifications (preliminary): SoC – ArtInChip D213ECV 64-bit RISC-V (RV64IMAFDC) processor System Memory – 128MB 16-bit DDR3 @ 672 MHz (SiP) Storage – 256MB (2Gbit) SPI NAND flash (Winbond 25N02KVZEIR), microSD card slot (bottom side of the board) Networking – 2x Gigabit Ethernet […]

ESP32-S3 board features 2.8-inch display, Blackberry-like keyboard, and optional LoRaWAN connectivity

LILYGO T-Deck is a development kit with an ESP32-S3 WiFi and BLE module, a 2.8-inch display with touchscreen support, a Blackberry-like keyboard based on ESP32-S3, and optional LoRaWAN connectivity through an SX1262 LoRa module. It looks ideal for text-based messaging, but the devkit also includes two microphones and a speaker so audio communication must be possible. Other features include a MicroSD card slot, a Grove connector (UART) for expansion, and support for a LiPo battery with USB charging. LILYGO T-Deck specifications: ESP32-S3-WROOM-1 wireless module SoC – ESP32-S3FN16R8 dual-core Tensilica LX7 microcontroller @ up to 240 MHz with 2.4 GHz 802.11n WiFi 4 and Bluetooth 5.0 LE connectivity Memory – 8MB PSRAM Storage – 16MB SPI flash PCB antenna Storage – MicroSD card slot Display – 2.8-inch IPS display with 320×240 resolution; ST7789 SPI display controller Audio – Built-in speaker using MAX98357A amplifier, 2x MEMS microphones Wireless 2.4 GHz 802.11n WiFi […]

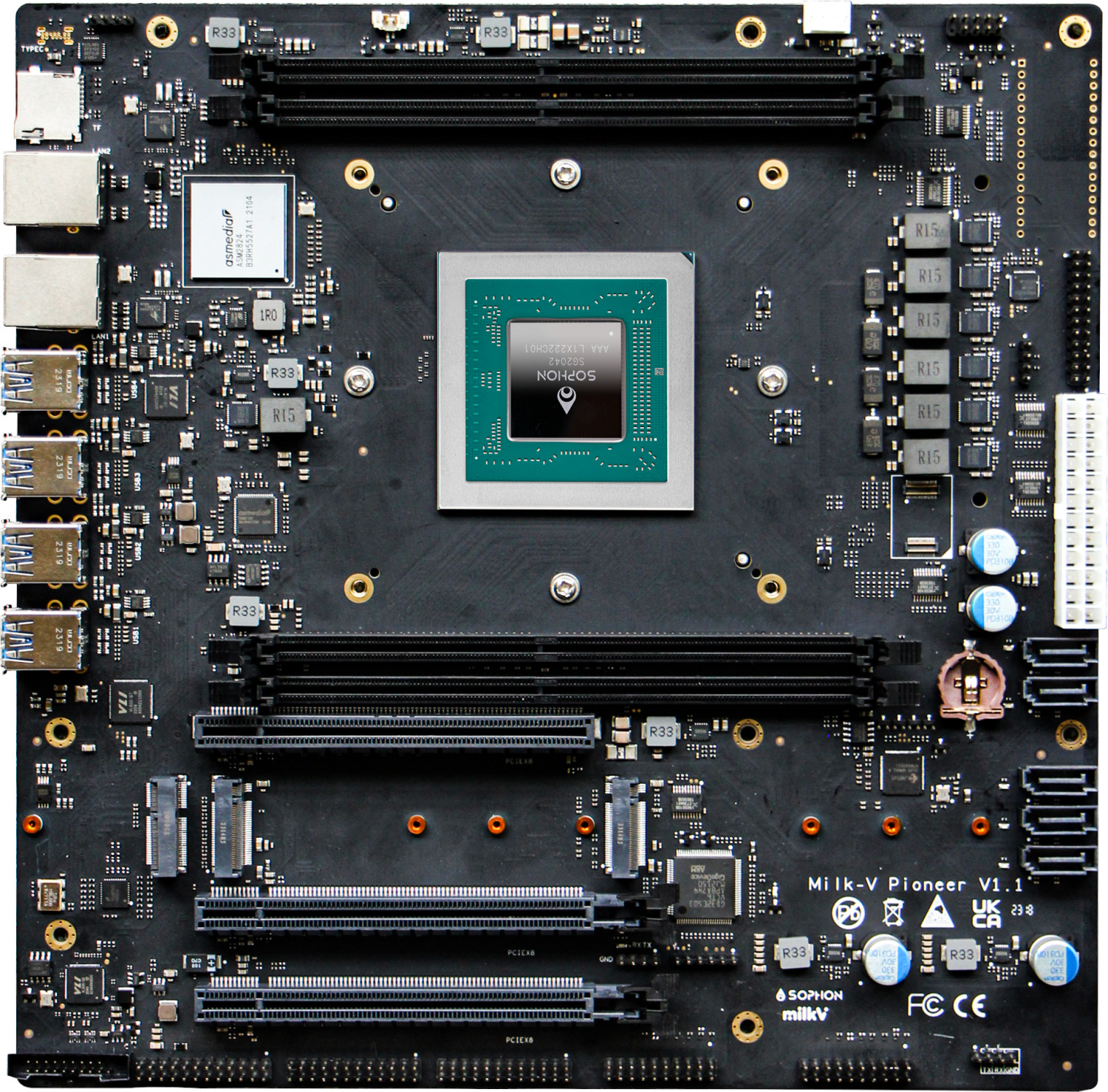

64-core RISC-V motherboard and workstation enable native RISC-V development (Crowdfunding)

There’s now a microATX motherboard and workstation for native RISC-V development based on the SOPHON SG2042 64-core RISC-V C920 processor with up to 128GB DDR4 memory, various SATA and M.2 NVMe interfaces for storage, three PCIe x16 slot for expansion and more. I remember a few years ago, there was a lot of talk about making a workstation for native Arm development instead of relying on x86 machines, cross-compilation, and emulation. So we got hardware like the HoneyComb LX2K, Ampere eMAG, and more recently the ADLINK Ampere Altra Dev Kit to achieve this goal. The RISC-V ecosystem is now getting something similar thanks to the Milk-V Pioneer microATX motherboard and the Pioneer Box that provides a complete 64-core RISC-V workstation with DIMM memory, SATA and NVMe storage, a graphics card, 10GbE networking, a 350W power supply, and more. Pioneer board specifications: SoC – Sophgo SOPHON SG2042 64-core RISC-V processor (T-Head […]

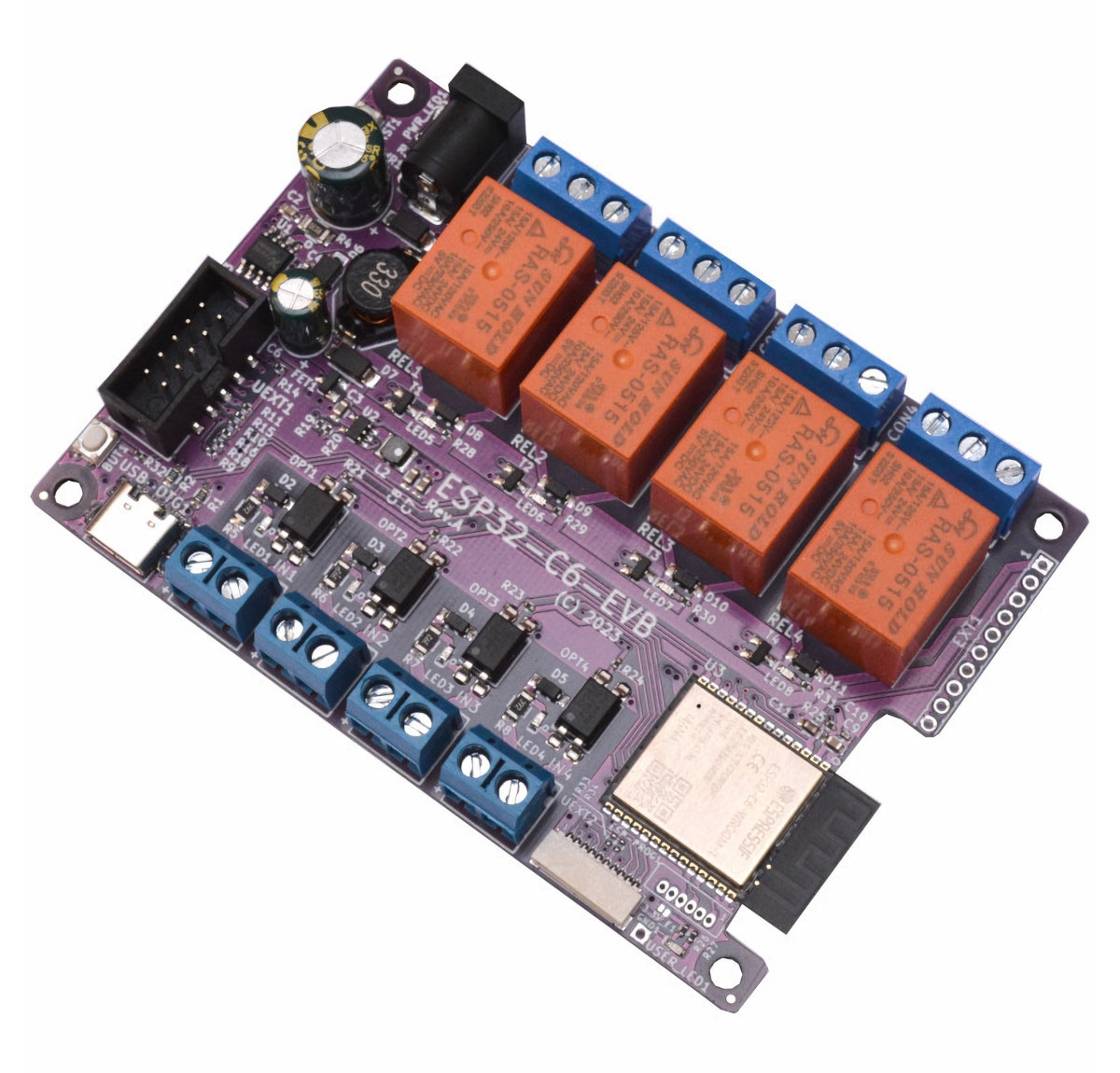

Olimex ESP32-C6-EVB supports WiFi 6, BLE, Zigbee, comes with four relays, four opto-isolated inputs

Olimex ESP32-C6-EVB is an open-source hardware board based on an ESP32-C6 wireless module with 2.4 GHz WiFi 6, Bluetooth LE, and Zigbee connectivity, and offering four relays and four opto-isolated inputs, as well as further expansion via two UEXT connector. So far we had a limited amount of third-party ESP32-C6 boards, with Espressif making their own module and development board available in January, and 01Space launching a tiny ESP32-C6 board in April, a time when a lot of software work was still needed. But the ESP-IDF v5.1 with ESP32-C6 support is nearing release (now RC2), and the Olimex board may mark the start of greater availability of ESP32-C6 hardware with stable/usable firmware. ESP32-C6-EVB specifications: Wireless module – ESP32-C6-WROOM-1-N4 module with Espressif Systems ESP32-C6 single core 32-bit RISC-V processor @ 160 MHz with 2.4 GHz WiFi 6 1T1R with Target Wake Time (TWT) support, Bluetooth LE 5.0, and 802.15.4 radio for […]

Linux 6.4 release – Main changes, Arm, RISC-V and MIPS architectures

Linux 6.4 has just been released by Linus Torvalds on the Linux Kernel Mailing List (LKML): Hmm. Final week of 6.4 is done, and we’ve mainly got some netfilter fixes, some mm reverts, and a few tracing updates. There’s random small changes elsewhere: the usual architecture noise, a number of selftest updates, some filesystem fixes (btrfs, ksmb), etc. Most of the stuff in my mailbox the last week has been about upcoming things for 6.5, and I already have 15 pull requests pending. I appreciate all you proactive people. But that’s for tomorrow. Today we’re all busy build-testing the newest kernel release, and checking that it’s all good. Right? Released around two months ago, Linux 6.3 brought us AMD’s “automatic IBRS” Spectre defense mechanism, additional progress on the Rust front with User-mode Linux support (on x86-64 systems only), the NFS filesystem (both the client and server sides) gained support for […]