Sipeed has unveiled three new hardware platforms based on the LM4A RISC-V system-on-module found in their LicheePi 4A SBC, namely the Lichee Cluster 4A cluster for native RISC-V compilation, the Lichee Pad 4A 10.1-inch tablet running Android 13 or Debian, and the Lichee Console 4A a portable Linux console with a small 7-inch display and a built-in keyboard. As a quick reminder, the Sipeed LM4A SoM is based on the Alibaba T-Head TH1520 quad-core RISC-V processor @ 1.8 to 2.5 GHz that has just gotten some support in Linux 6.5, comes with up to 16GB RAM and up to 64 GB eMMC flash, integrates two Gigabit Ethernet PHY, and exposes all I/Os through a 260-pin SO-DIMM connector. We’ve previously noticed the TH1520 module delivers performance similar to the Raspberry Pi Compute Module 4 and even more when using a customized toolchain. Lichee Cluster 4A All new Sipeed hardware platforms feature […]

Linux 6.5 release – Notable changes, Arm, RISC-V and MIPS architectures

Linus Torvalds has just announced the release of Linux 6.5 on the Linux Kernel Mailing List (LKML): So nothing particularly odd or scary happened this last week, so there is no excuse to delay the 6.5 release. I still have this nagging feeling that a lot of people are on vacation and that things have been quiet partly due to that. But this release has been going smoothly, so that’s probably just me being paranoid. The biggest patches this last week were literally just to our selftests. The shortlog below is obviously not the 6.5 release log, it’s purely just the last week since rc7. Anyway, this obviously means that the merge window for 6.6 starts tomorrow. I already have ~20 pull requests pending and ready to go, but before we start the next merge frenzy, please give this final release one last round of testing, ok? Linus The earlier […]

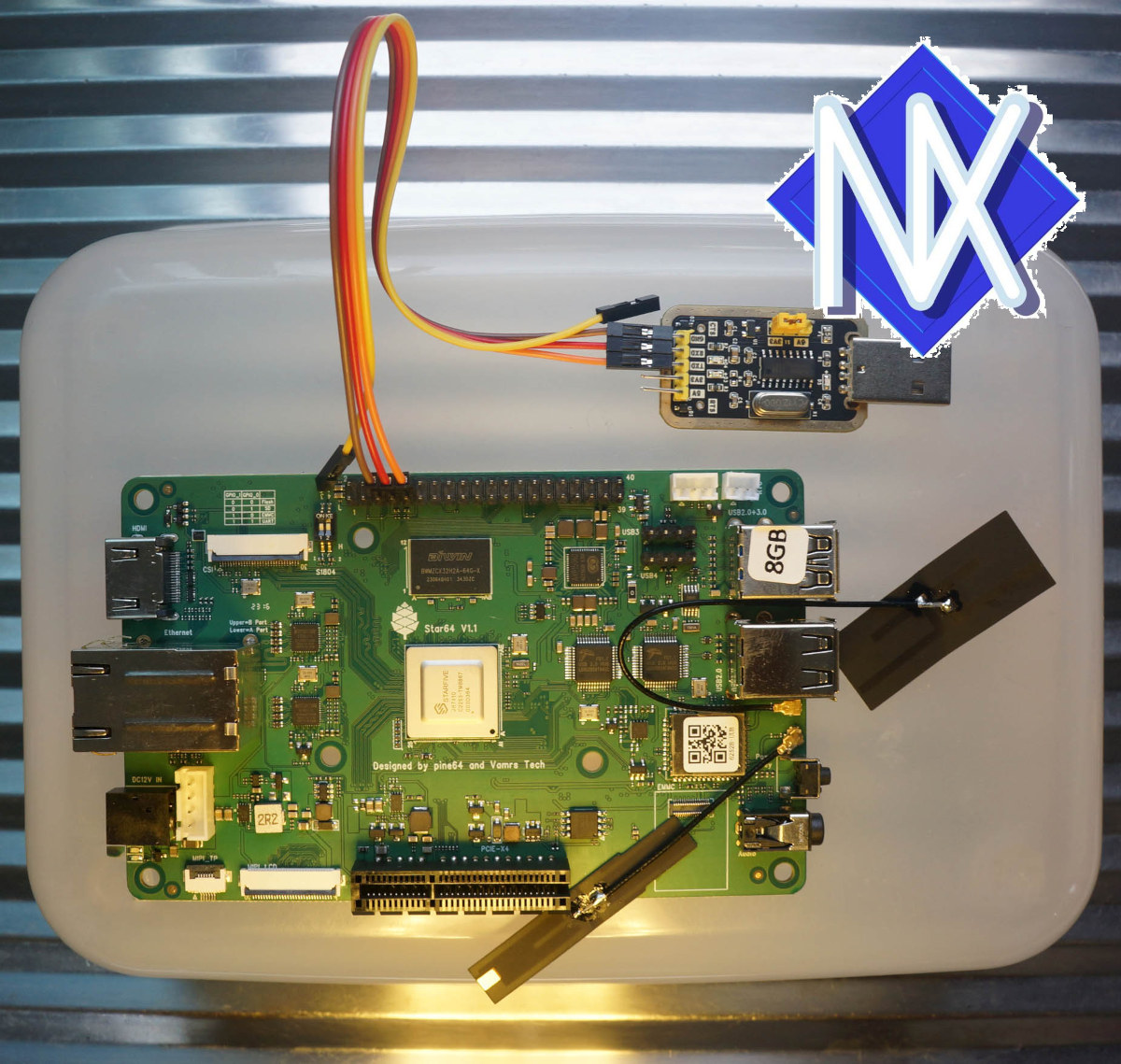

Star64 RISC-V SBC can now boot Apache NuttX real-time operating system

Most of the software development efforts on the more powerful RISC-V boards like Pine64 Star64 or StarFive VisionFive 2 have been focusing on Linux, but Lup Yuen Lee tried something different and managed to boot Apache NuttX real-time operating system on the StarFive JH7110-powered Star64 SBC. NuttX may not often make the news, but they are plenty of supported platforms, and we previously played with it on the Sony SPresense board, and reported about NuttX RTOS on ESP32, so it’s good seeing the open-source real-time operating system add support for the RISC-V architecture. [Update: RISC-V support was added many years ago, sometimes around 2016] The main trick to boot NuttX on the Star64 is to make U-boot think the NuttX kernel is the Linux kernel. That means a Linux image such as sdcard.img for the VisionFive 2 board will be used to get OpenSBIU and U-boot bootloaders, and the NuttX […]

DietPi News – v8.20 released, NanoPi Neo Air handheld Linux terminal

The latest DietPi v8.20 release of the lightweight Debian-based Linux distribution for SBCs and server systems was outed on July 29, 2023, and on a separate note, a DIY handheld Linux terminal based on the NanoPi Neo Air SBC and running DietPi has been found on the interwebs. DietPi v8.20 release The project team released the new DietPi v8.20 on July 29th, 2023 with the following highlights: Homebridge: New software package bringing Apple Homekit support Kernel updates for Pine64 Quartz64 – Linux 6.4.7 and enabled support for the NFS kernel server FriendlyELEC NanoPi R5S/R5C/R6S series – Linux 5.10.160 StarFive VisionFive 2 RISC-V SBC – Linux 5.15.123 WiFi Hotspot: Enhanced DHCP default settings Fixes and updates for DietPi-LogClear, DietPi-Dashboard, DietPi-LetsEncrypt, PaperMC, vaultwarden, etc… The full changelog can be found on the DietPi website and the source code is hosted on GitHub. NanoPi Neo Air handheld Linux terminal running DietPi While it’s […]

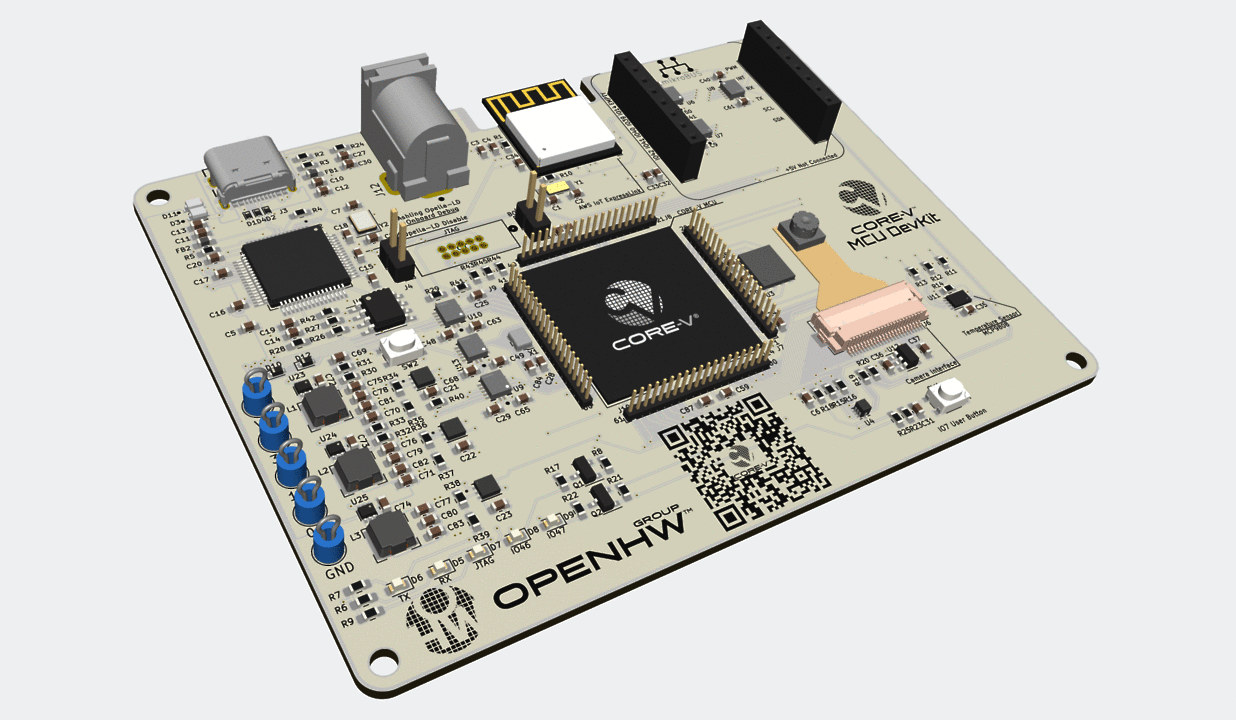

CORE-V MCU Devkit features open-source 32-bit RISC-V core, Amazon AWS IoT connectivity, Mikrobus expansion, VGA camera

The CORE-V MCU DevKit is an open-source hardware board based on the CORE-V microcontroller featuring the open-source OpenHW CV32E40P0 RISC-V MCU core and a Quicklogic ArticPro 2 eFPGA. The board offers wireless connectivity to Amazon AWS through an ESP32-C3 AWS IoT ExpressLink module, a MikroBus connector for expansion, a VGA camera module, JTAG and serial debugging, as well as a temperature sensor and a few buttons. The development kit can be powered by its USB Type-C port (5V) or a DC jack taking 5V to 18V DC. CORE-V MCU devkit specifications: Microcontroller – CORE-V MCU OpenHW CV32E40P RISC-V processor core (in-order 4-stage RISC-V RV32IMFCXpulp CPU based on RI5CY from PULP-Platform) with 512KB SRAM, boot ROM Quicklogic ArticPro 2 eFPGA Storage – 4MB QSPI flash Wireless – Espressif AWS IoT ExpressLink Module for AWS IoT cloud interconnect Camera – Himax HM01B0 ultra-low-power QVGA (320×240) CMOS image sensor as found in the […]

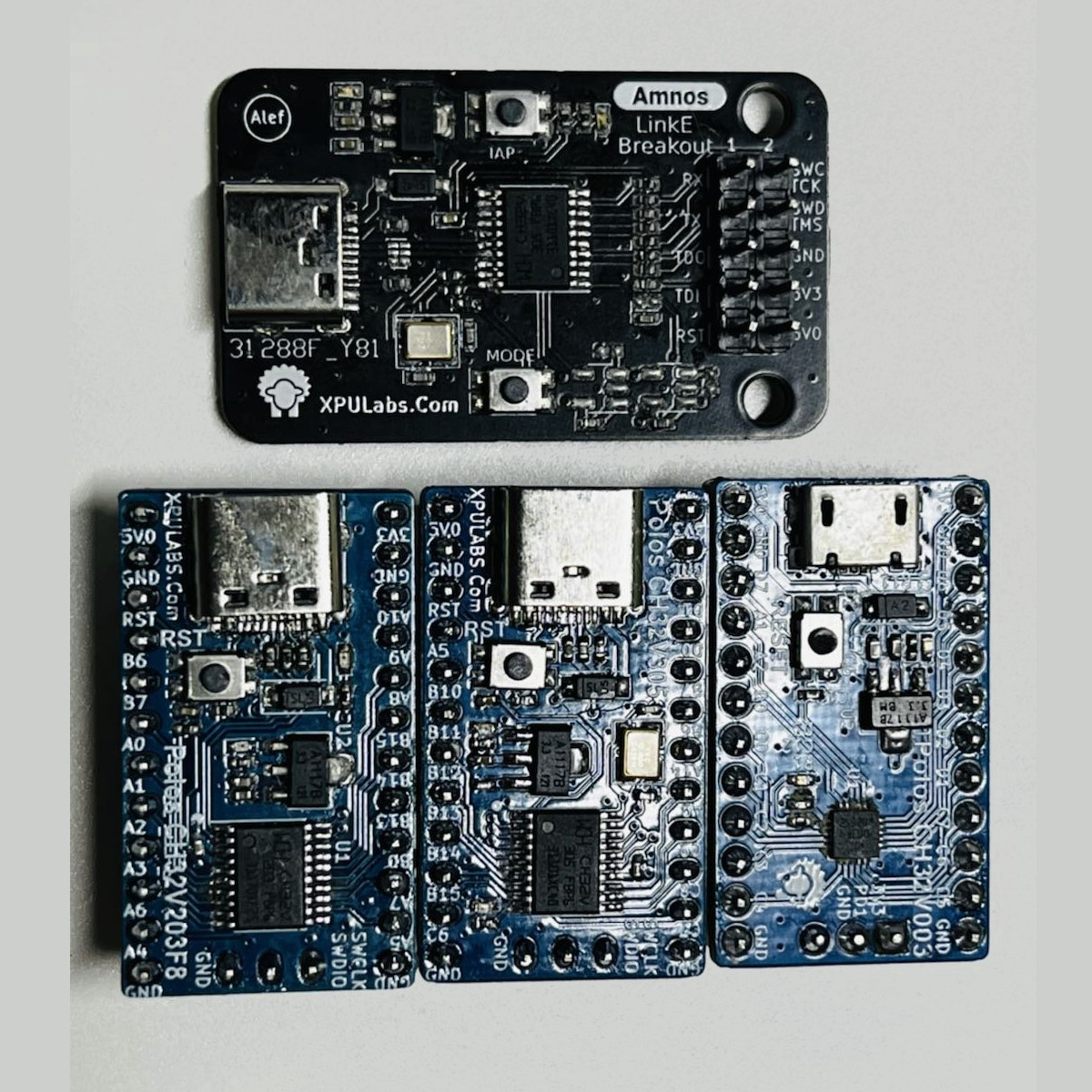

Polos CH32Vxx 32-bit RISC-V MCU boards starts at $1.99

XPU Labs, a subsidiary of AnalogLamb, has designed three inexpensive “Polos” development boards based on WCH CH32VXX RISC-V microcontrollers with pricing starting at just $1.99. The three development/breakout boards have the same form factor and only differ in the specific RISC-V MCU used with three parts selected: the 48 MHz CH32V003F4U6 microcontroller, the 144 MHz CH32V203F8P6 MCU, and the CH32V305FBP6 that’s similar to the former but add more memory (32KB) and flash (128KB). You can see also three boards side-by-side in the photo below along with the Amnos LinkE CH32Vxx debugger & programmer board. Polos CH32V003 Breakout Alef specifications: MCU – WCH CH32V003F4U6 QingKe 32-bit RISC-V2A microcontroller up to 48MHz with 2KB SRAM, 16KB Flash (QFN20 Package) USB – 1x Micro USB port I/Os – 2x 12-pin headers with Up to 18 GPIOs with external interrupt support 1x USART, 1x I2C, 1x SPI 10-bit ADC Debugging – 1-wire serial debug […]

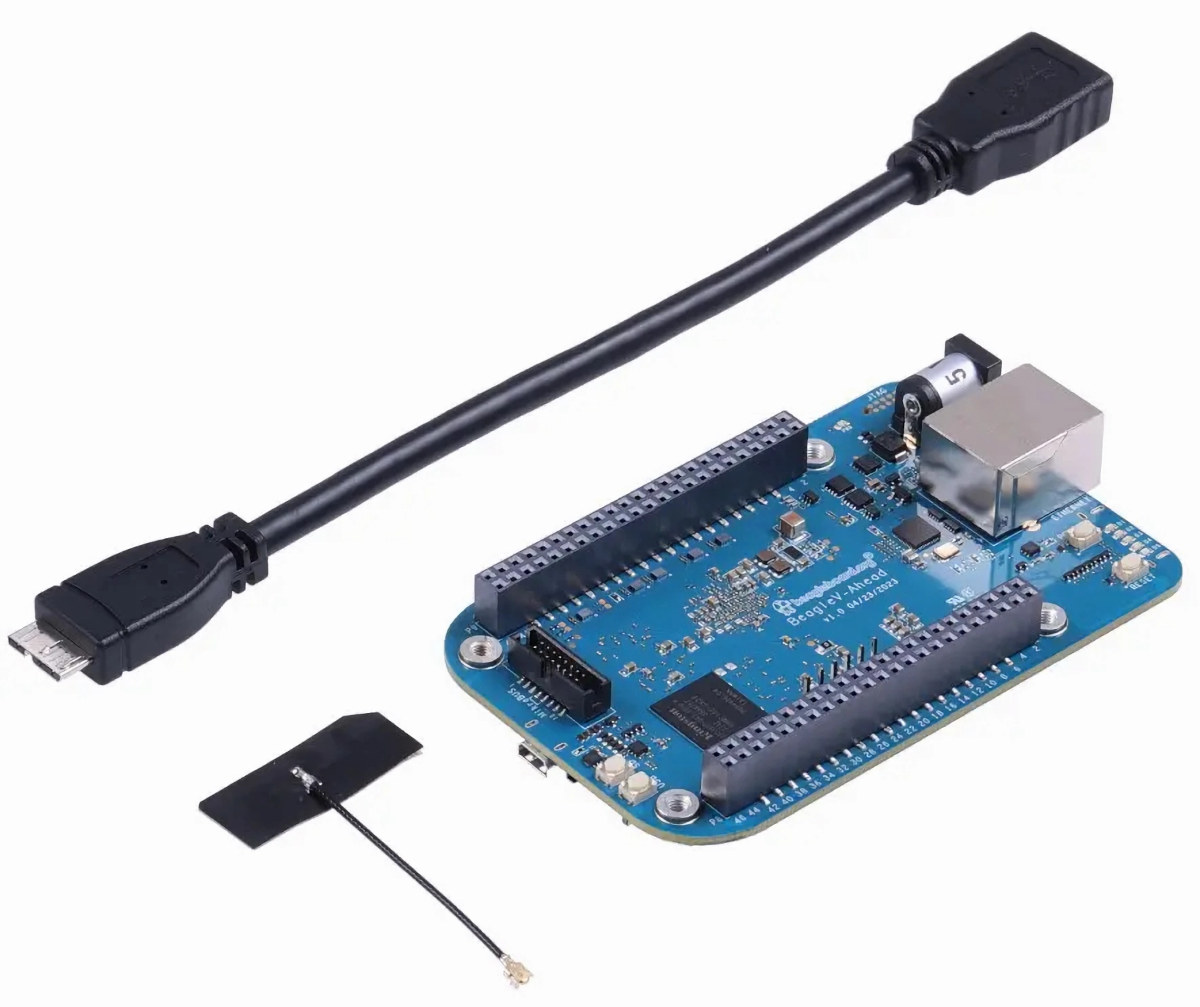

BeagleV-Ahead quad-core RISC-V SBC offers BeagleBone Capes compatibility

Beagleboard.org Foundation’s BeagleV-Ahead is a single board computer powered by the T-Head TH1520 quad-core RISC-V processor and following the form factor of the popular BeagleBone Black board based on a Texas Instruments Sitara AM3359 single-core Arm Cortex-A8 processor. The new board looks better in almost every way with a much faster processor, 4GB RAM, 16GB eMMC flash, Gigabit Ethernet, built-in WiFI and Bluetooth, a micro USB 3.0 port, micro HDMI video output up to 4Kp60, etc… and the same 80-pin headers as found on other BeagleBone boards. The main downside is that it comes at a significantly higher price as we’ll see further below. BeagleV-Ahead specifications: SoC – Alibaba T-Head TH1520 CPU – quad-core RISC-V Xuantie C910 (RV64GCV) processor @ up to 2.0 GHz, low power Xuantie E902 core GPU – Imagination BXM-4-64 GPU with OpenGL ES 3.2, OpenCL 2.0, Vulkan 1.2, 50.7GFLOPS DSP – Xuantie C906 audio DSP @ […]

UniHiker review – A Linux-based STEM education platform with IoT and AI support, Micro:bit edge connector

DFRobot’s UniHiker is a STEM educational platform that was originally launched in China, but now UniHiker is now available worldwide through the DFRobot shop. The company has sent us a UniHiker sample for review, so let’s unpack the kit and learn how to use the UniHiker platform. The main component of the kit is the Linux-powered UniHiker board which features a 2.8-inch resistive touchscreen display and a BBC Micro:bit edge connector, so we can use expansion boards for the Micro:bit board. Let’s start unboxing it together. UniHiker unboxing DFRobot sent us the UniHiker platform by DHL. The package is a familiar-looking DFRobot box in orange color and comes with a plastic box to safely store the UniHiker board and accessories after use. The plastic box contains another plastic box with the board, some 3-pin and 4-pin cables for Gravity ports, and a USB Type-C cable. The UniHiker is like a […]