Linux 5.12 release was expected last Sunday, but Linus Torvalds decided to release one more release candidate, namely Linux 5.12-RC8, to “make sure things are all settled down“, so the latest Linux kernel is now expected this weekend. Tihs should not yield any significant changes, so we can check what’s new in Linux 5.12, notably with regards to Arm, MIPS, and RISC-V architectures often used in SoC’s found in embedded systems. Around two months ago, the release of Linux 5.11 added support for Intel’s software guard extensions (SGX) and Platform Monitoring Technology (PMT), AMD “Van Gogh” and “Dimgrey cavefish” graphics processors, MIPI I3C host controller interfaces, and much more. Some interesting changes in Linux 5.12 include: Added support for ACRN hypervisor designed for IoT & embedded devices Added support for Playstation DualSense & Nintendo 64 game controllers, as well as Nintendo 64 data cartridges Dynamic thermal power management via a […]

Linux 5.11 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has released Linux 5.11 just in time for… “Valentine’s Day”: Nothing unexpected or particularly scary happened this week, so here we are – with 5.11 tagged and pushed out. In fact, it’s a smaller-than-average set of commits from rc7 to final, which makes me happy. And I already have several pull requests lined up for tomorrow, so we’re all set for the merge window to start. But in the meantime – and yes, I know it’s Valentine’s Day here in the US – maybe give this release a good testing before you go back and play with development kernels. All right? Because I’m sure your SO will understand. Linus Last time around, Linux 5.10 was an LTS release that added EXT-4 performance enhancements, improved post-Spectre performance, as well as the enablement of BCM2711 (Raspberry Pi 4) display pipeline, among other many changes. Some of the notable changes in […]

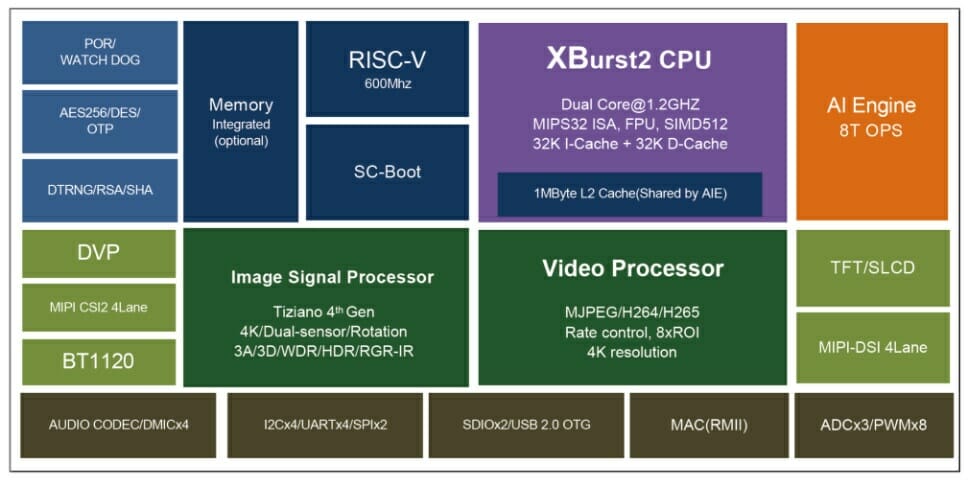

Ingenic T40 4K Video & AI Vision Processor mixes MIPS & RISC-V cores with AI accelerator

Ingenic T31 MIPS & RISC-V AI video processor was introduced last year with the MIPS core including SIMD128 Vector instructions for deep learning. The Chinese company has now introduced the new Ingenic T40 processor still with MIPS and RISC-V cores, but also a dedicated 8 TOPS AI engine/CNN accelerator. The new processor is especially suited to smart AI vision application thanks to support for 4K cameras, and 4K MJPEG/H.264/H.265 hardware video encoding, complemented by the 8 TOPS AI engine for computer vision workloads such as people detection, face recognition, object detection, and so on. Ingenic T40 key features and specifications: CPU – Dual-core MIPS XBurst2 @ 1.2 GHz with 256KB L2 Cache, SIMD512 instruction set MCU – 600MHz RISC-V coprocessor AI Engine – 8 TOPS neural network accelerator with 1MB memory pool, support for int16/int8/int4/int2 convolution width Memory – DDR2/DDR3/DDR3L up to 2GB Storage – SPI NOR flash, SPI NAND flash, […]

Linux 5.10 LTS release – Main changes, Arm, MIPS and RISC-V architectures

Linus Torvalds has just released Linux 5.10: Ok, here it is – 5.10 is tagged and pushed out. I pretty much always wish that the last week was even calmer than it was, and that’s true here too. There’s a fair amount of fixes in here, including a few last-minute reverts for things that didn’t get fixed, but nothing makes me go “we need another week”. Things look fairly normal. It’s mostly drivers – as it should be – with a smattering of fixes all over: networking, architectures, filesystems, tooling.. The shortlog is appended, and scanning it gives a good idea of what kind of things are there. Nothing that looks scary: most of the patches are very small, and the biggest one is fixing pin mapping definitions for a pincontrol driver. This also obviously means that the merge window for 5.11 will start tomorrow. I already have a couple […]

Linux 5.9 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.9 on lkml: Ok, so I’ll be honest – I had hoped for quite a bit fewer changes this last week, but at the same time there doesn’t really seem to be anything particularly scary in here. It’s just more commits and more lines changed than I would have wished for. The bulk of this is the networking fixes that I already mentioned as being pending in the rc8 release notes last weekend. In fact, about half the patch (and probably more of the number of commits) is from the networking stuff (both drivers and elsewhere). Outside of that, the most visible thing is a reinstatement of the fbdev amba-clcd driver – that’s a noticeable patch, but it’s basically just mainly a revert. The rest is really really tiny (mostly some other minor driver updates, but some filesystem and architecture fixes […]

Linux 5.8 Release – Main Changes, Arm, MIPS, and RISC-V Architectures

Linus Torvalds has just released Linux 5.8: So I considered making an rc8 all the way to the last minute, but decided it’s not just worth waiting another week when there aren’t any big looming worries around. Because despite the merge window having been very large, there really hasn’t been anything scary going on in the release candidates. Yeah, we had some annoying noise with header file dependencies this week, but that’s not a new annoyance, and it’s also not the kind of subtle bug that keeps me up at night worrying about it. It did reinforce how nice it would be if we had some kind of tooling support to break nasty header file dependencies automatically, but if wishes were horses.. Maybe some day we’ll have some kind of SAT-solver for symbol dependencies that can handle all our different architectures and configurations, but right now it’s just a manual […]

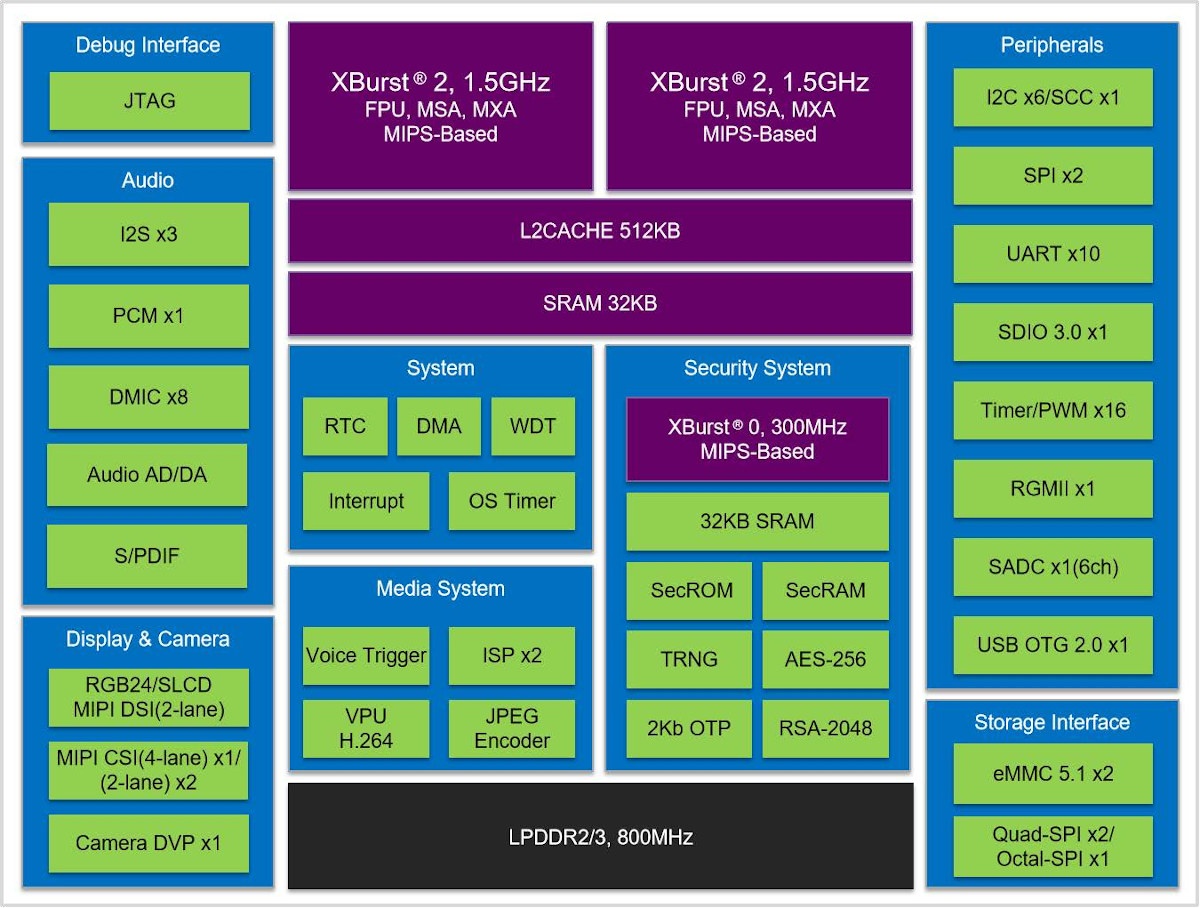

Ingenic X2000 IoT Application Processor Combines 32-bit MIPS Xburst 2 Cores with Xburst 0 Real-time Core

In Arm’s world, heterogeneous processors are pretty common, with for example big.LITTLE / dynamIQ application processors mixing powerful Cortex-A7x cores with power-efficient Cortex-A5x cores., or “industrial” processor such NXP i.MX 8M family with Cortex-A53 application cores combined with Cortex-M4F real-time core. Maybe I did not follow enough, but I hadn’t really seen anything equivalent in MIPS world, except if we count Ingenic T31 with RISC-V and MIPS cores. That is until today where I was informed about documents related to Ingenic X2000 IoT application processor with two 32-bit MIPS Xburst 2 core, one MIPS Xburst 0 real-time cores, as well as up to 256MB RAM built-into the SoC. Ingenic X2000 specifications: CPU Core – Dual XBurst 2, MIPS ISA based, frequency up to 1.5 GHz with 32KB L1 x2 Cache, 512KB L2 Cache, 32KB SRAM, FPU,128bit SIMD MCU Core – XBurst 0 MIPS core @ 300MHz for security and real-time […]

Linux 5.7 Released – Main Changes, Arm, MIPS and RISC-V Architectures

OK… I’m a bit late on that one. Linus Torvalds released Linux 5.7 last week: So we had a fairly calm last week, with nothing really screaming “let’s delay one more rc”. Knock wood – let’s hope we don’t have anything silly lurking this time, like the last-minute wifi regression we had in 5.6.. But embarrassing regressions last time notwithstanding, it all looks fine. And most of the discussion I’ve seen the last week or two has been about upcoming features, so the merge window is now open and I’ll start processing pull requests tomorrow as usual. But in the meantime, please give this a whirl. We’ve got a lot of changes in 5.7 as usual (all the stats look normal – but “normal” for us obviously pretty big and means “almost 14 thousand non-merge commits all over, from close to two thousand developers”), So the appended shortlog is only […]