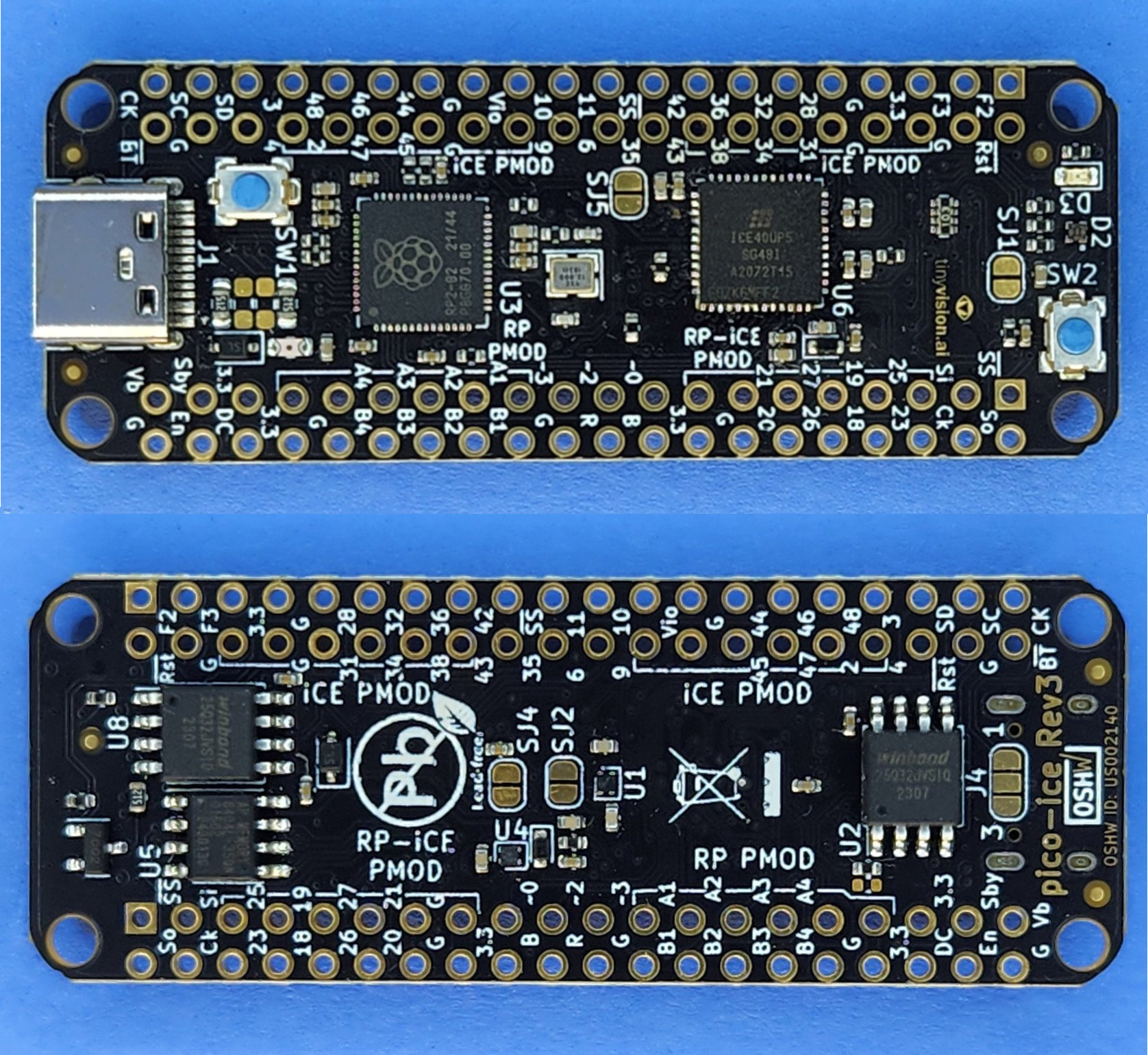

tinyVision.ai Pico-Ice is a development board with a Raspberry Pi RP2040 MCU and a Lattice ICE40 UltraPlus 5K FPGA connected through an 8-bit bus. The Arm Cortex-M0+ microcontroller provides the clock for the FPGA and can program the FPGA directly or the dedicated FPGA flash using a drag-drop of a UF2 file. Just a few days ago we wrote about the LILYGO T-FPGA board that combines an ESP32-S3 wireless MCU with a Gowin FPGA connected through a 6-bit bus, and the Pico-Ice board provides a similar option with different chips and without wireless connectivity. Pico-Ice specifications: MCU – Raspberry Pi RP2040 dual-core Cortex-M0+ microcontroller @ 133 MHz with 264KB SRAM with all pins exposed FPGA – Lattice UltraPlus iCE40UP5K FPGA with 5.3K LUTs, 1Mbit SPRAM, 120Kbit DPRAM, 8x multipliers with all pins brought out Memory & storage chips MCU – 4MB QSPI flash FPGA – 4MB QSPI Flash, 8MB low […]

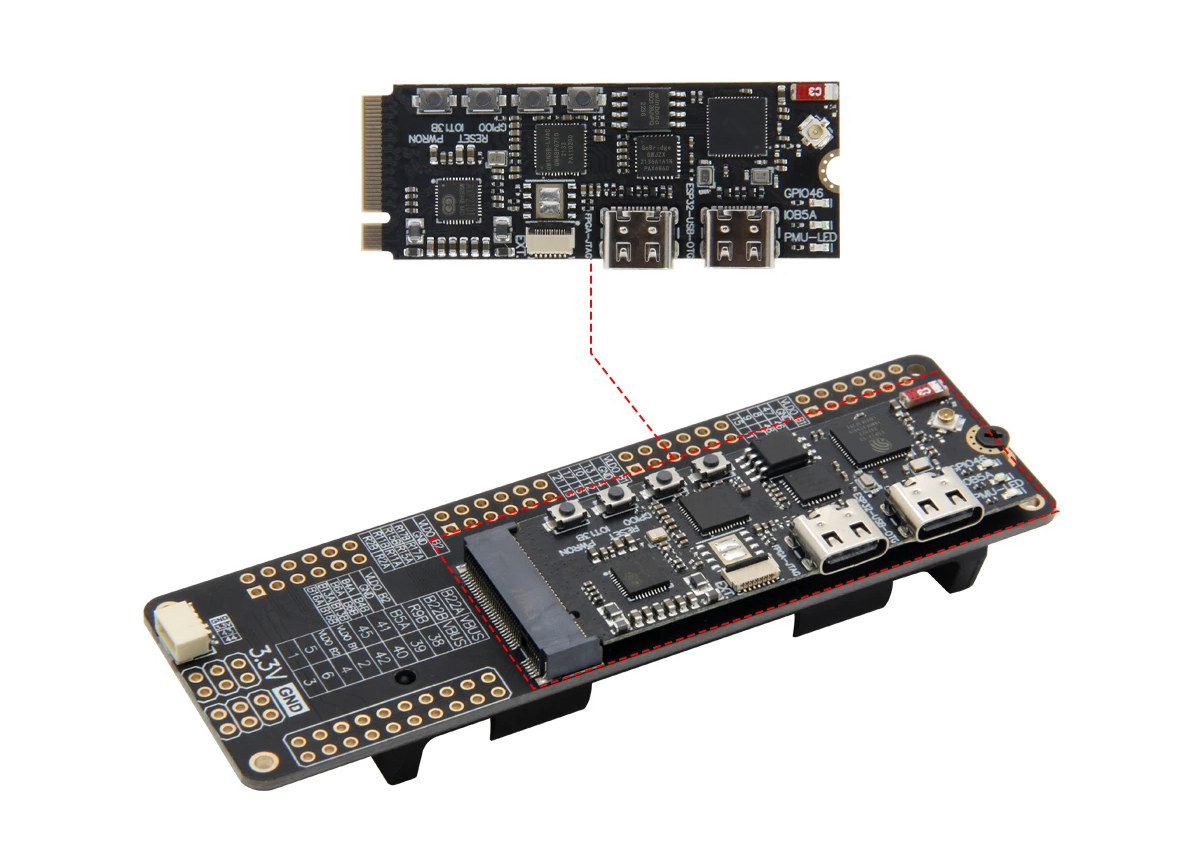

LILYGO T-FPGA devkit combines ESP32-S3 WiSoC with Gowin GW1NSR-4C FPGA

LILYGO T-FPGA development kit is comprised of an M.2 module with an ESP32-S3 WiFi and Bluetooth wireless microcontroller and a Gowin GW1NSR-4C FPGA with 4,608 LUTs, and a carrier board that gives easy access to I/Os and comes with a 18650 battery holder. The module comes with a USB -C OTG port connected to the ESP32-S3, and a USB-C FPGA port for the FPGA. The “T-FPGA shield” carrier board includes four Pmod interfaces and a STEMMA Qt/Qwiic connector for expansion, plus several pins for 3.3 and GND, and another 20-pin I/O header. LILYGO T-FPGA specifications: Wireless MCU – Espressif Systems ESP32-S3R8 dual-core Tensilica LX7 @ up to 240 MHz with vector instructions for AI acceleration, 512KB RAM, 8MB PSRAM, wireless connectivity Storage – 16MB flash FPGA – Gowin Semiconductors GW1NSR-LV4CQN48PC6/I5 with 4,608 LUT4, 256Kb flash, 64Mb PSRAM, 64Mb Hyperflash, 32Mb NOR flash Connectivity via ESP32-S3 2.4 GHz 802.11 b/g/n Wi-Fi […]

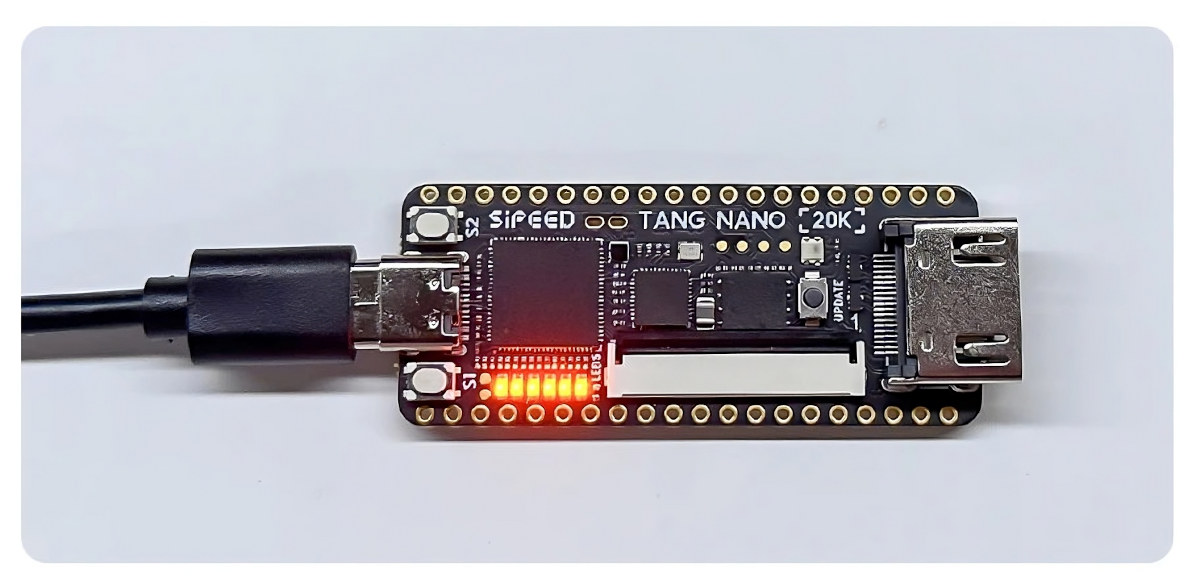

$25 Sipeed Tang Nano 20K FPGA board can simulate a RISC-V core, run Linux, retro games

The Sipeed Tang Nano 20K is a low-cost FPGA development board based on Gowin GW2AR-18 FPGA with 20,736 logic cells and 64Mbit RAM, which coupled with 64MBit QSPI flash provides enough resources to simulate a 32-bit RISC-V core booting Linux or playing retro games in an emulator. The FPGA board comes with a USB-C port for power and to load the FPGA bitstream through a BL616 microcontroller that also acts as a USB to serial chip, an HDMI port and an RGB LCD interface for video output, two user buttons, and two rows GPIOs to connect peripherals such as gamepads (through adapters). Sipeed Tang Nano 20K specifications: FPGA – Gowin GW2A-LV18QN88C8I7 with 20,736 logic units (LUT4) 15,552 flip-flops (FF) RAM 41,472 shadow SRAM (S-SRAM) 828K block SRAM (B-SRAM) Numbers of B-SRAM – 46 64Mbit 32-bit SDR SDRAM 48x 18×18 multipliers 2x PLLs 8x I/O Bank Onboard debugger – Bouffalo Labs […]

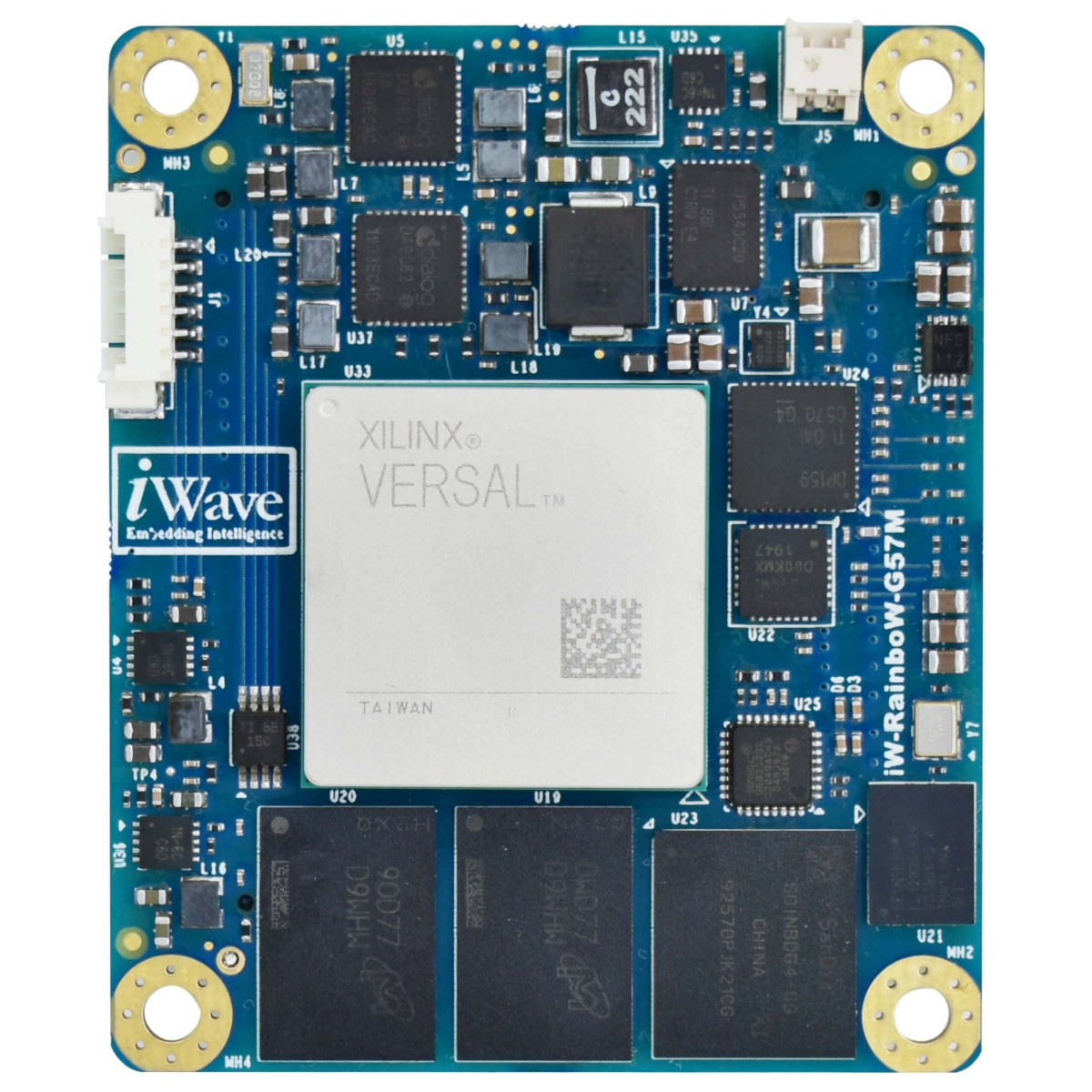

AMD Versal AI Edge SoC FPGA system-on-module targets ADAS, robotics, medical imaging, and other AI applications

iWave Systems iW-Rainbow-G57M is a system-on-module (SoM) based on the AMD (Xilinx) Versal AI Edge series of Cortex-A72/R5 SoC FPGAs designed to deliver AI acceleration at relatively low power for demanding applications such as ADAS, robotics, and medical imaging. The module comes with up to 8GB 64-bit LPDDR4, 16GB eMMC Flash, 256MB QSPI Flash, delivers up to 45 TOPS of AI performance, and features eight transceivers that can be used for high-speed Ethernet, PCIe, MIPI DSI/CSI interfaces, and/or others as required by the customer’s specific project. iW-Rainbow-G57M specifications: FPGA SoC – AMD Xilinx Versal AI Edge/Prime SFVA784 package (VE2302, VE2202, VE2102, or VE2002) with Dual Arm Cortex-A72 core processor @ up to 1.6 GHz Dual-core Arm Cortex-R5F Up to 328K Logic cells & 150K LUTs Programmable Network on Chip (NoC) Up to 45 TOPS (INT4) AI compute 8x GTYP Transceivers @ 28.21 Gbps (VE2302 & VE2202 only) Memory – Up […]

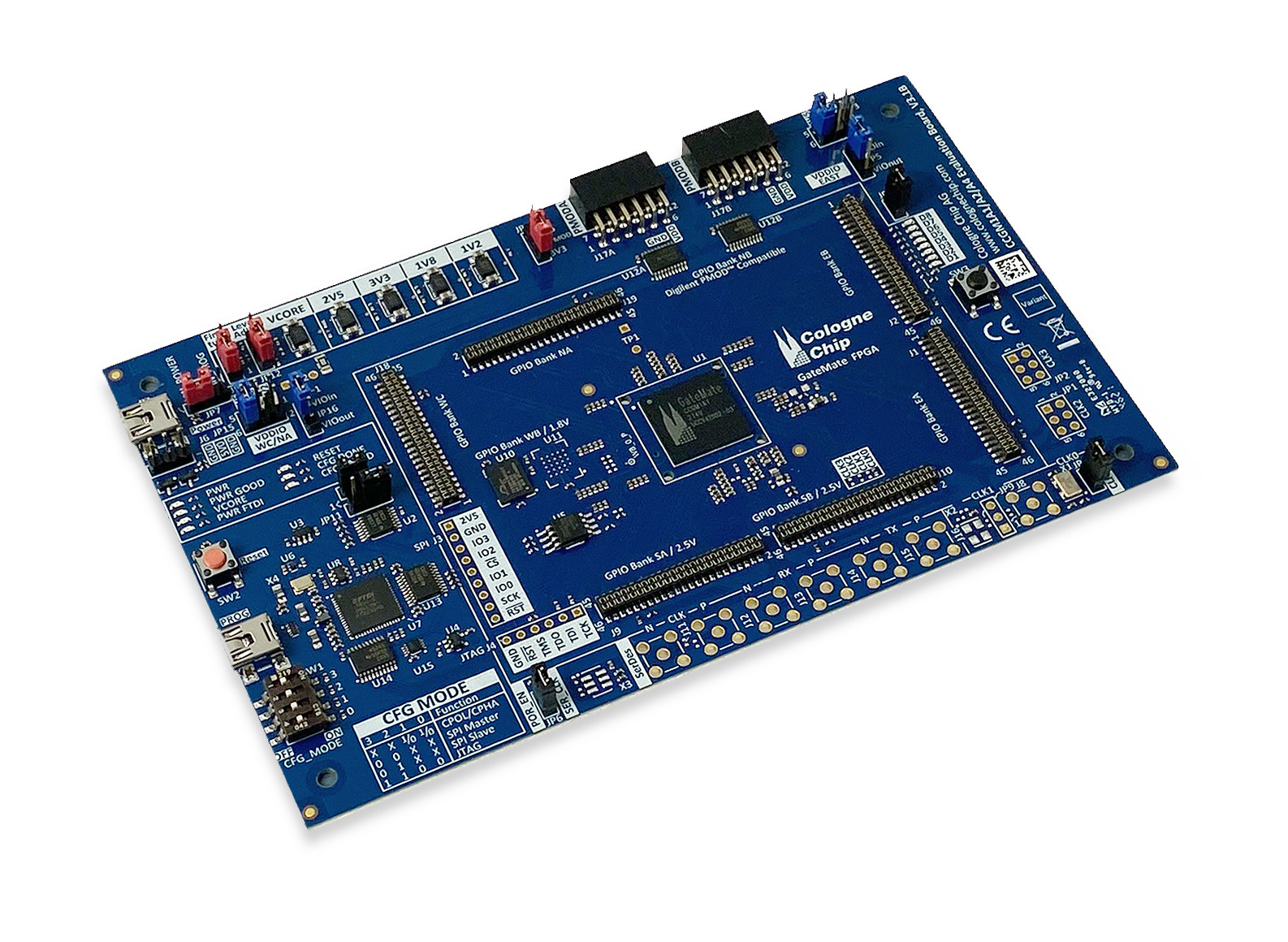

Cologne GateMate A1 FPGA chip with 20,480 LE is programmable with an open-source toolchain

Cologne Chip GateMate A1 is an FPGA with 20,480 logic elements best suited for lower-power applications and programmable with an open-source toolchain based on nMigen, Yosys, and other open-source tools. The A1 FPGA also comes with 1,280 Kbit block SRAM, four PLLs, a quad SPI interface up to 100 MHz, a 5Gbps SerDes interface, and the company offers an evaluation board to get started with development. GateMate A1 specifications: CPE Architecture 20,480 programmable elements (CPE) for combinatorial and sequential logic 40,960 Latches / Flip-Flops within programmable elements CPE consists of LUT-tree with 8 inputs Each CPE is configurable as a 2-bit full-adder or 2×2-bit multipliers Features 4x programmable PLLs quad SPI interface up to 100 MHz 1,280 Kbit dual-ported block RAM with variable data widths in 32 x 40 Kbit RAM cells Multipliers with arbitrary size implementable in CPE array Multiple clocking schemas All 162 GPIOs are configurable as single-ended […]

Linux 6.3 release – Notable changes, Arm, RISC-V and MIPS architectures

Linux Torvalds has just announced the release of Linux 6.3 on the Linux Kernel Mailing List (LKML): It’s been a calm release this time around, and the last week was really no different. So here we are, right on schedule, with the 6.3 release out and ready for your enjoyment. That doesn’t mean that something nasty couldn’t have been lurking all these weeks, of course, but let’s just take things at face value and hope it all means that everything is fine, and it really was a nice controlled release cycle. It happens. This also obviously means the merge window for 6.4 will open tomorrow. I already have two dozen pull requests waiting for me to start doing my pulls, and I appreciate it. I expect I’ll have even more when I wake up tomorrow. But in the meantime, let’s enjoy (and test) the 6.3 release. As always, the shortlog […]

Embedded Open Source Summit 2023 schedule – Zephyr OS, Security, IoT, Embedded Linux, and more

The Linux Foundation has just announced the full schedule for the Embedded Open Source Summit, which will take place on June 27-30, 2023 in Prague, Czech Republic, as well as virtually starting on June 26. Over 175 sessions, birds of a feather (BoF) tracks, and workshops related to embedded and open-source innovation will be presented at the event itself comprised of six micro conferences: Automotive Linux Summit Europe, Embedded IoT Summit, Embedded Linux Conference, LF Energy Embedded Summit, Safety-Critical Software Summit, and Zephyr Project Developer Summit. Even though I’m not going to attend personally, I’ve gone through the schedule to create my own little virtual schedule with some sessions relevant that should be interesting to me and hopefully to CNX Software readers. Monday, June 26 (Virtual sessions) The first day of the event will have a Yocto Dev training in the morning, and a bunch of virtual sessions that are […]

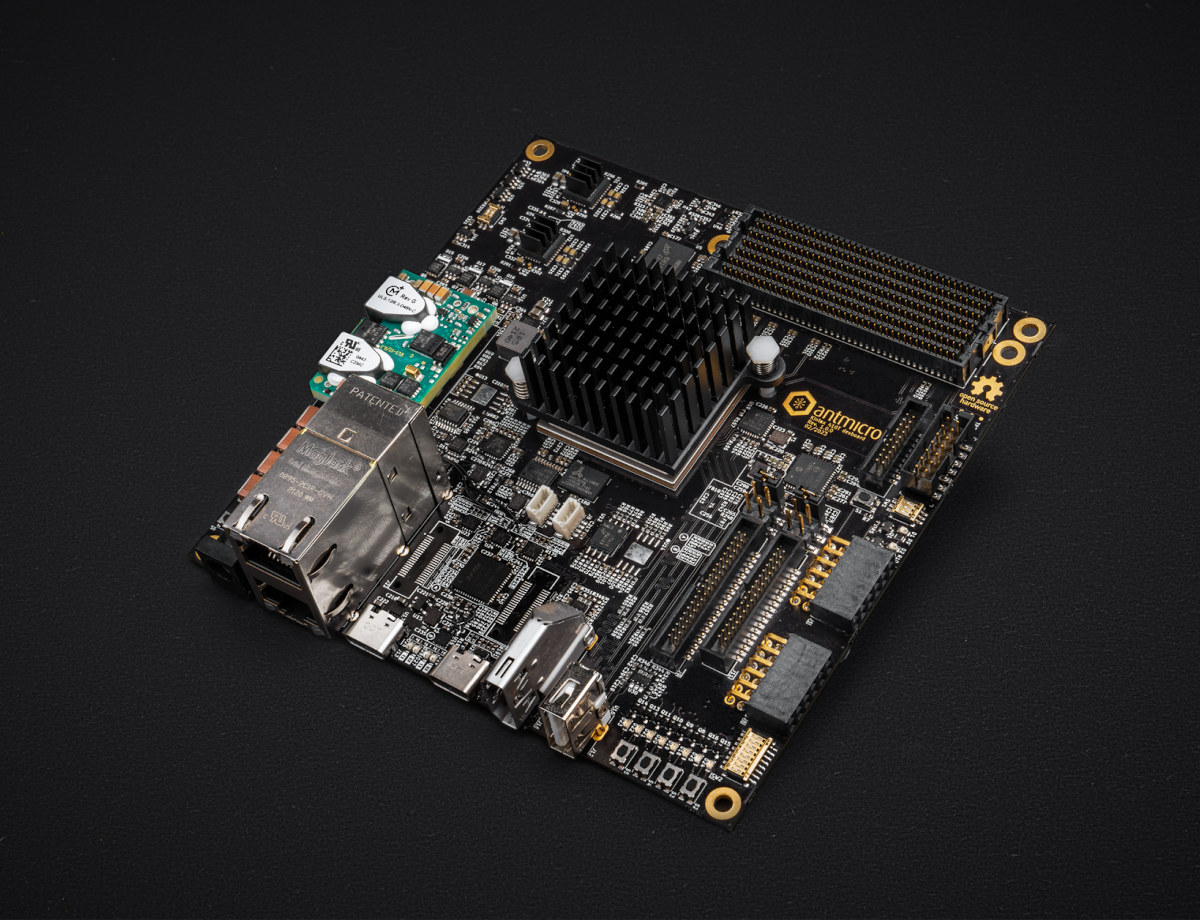

Antmicro releases open hardware AMD Kintex-7 K410T development board, launches open hardware portal

Antmicro has designed an open hardware AMD Xilinx Kintex-7 K410T FPGA development board in KiCad 6 mostly to synthesize custom RISC-V-based processing platforms and work on the OpenTitan Root of Trust project. Separately, the company has also launched an open hardware portal sharing some of the KiCad and Blender designs they’ve worked on over the years. Open-source hardware AMD Xilinx Kintex-7 K410T development board Key features and specifications: FPGA – AMD-Xilinx Kintex-7 K410T FPGA with 400K logic cells, 16 Gigabit transceivers operating at 12.5Gb/s. System Memory – 512MB of DDR3L memory, 8MB of SRAM memory Storage – 32MB (256Mbit) of (Q)SPI NOR flash, assembly option for 2x QSPI flash, microSD card slot Video Output – HDMI port Networking – 1x Gigabit Ethernet RJ45 port, 1x 10/100M Ethernet port USB USB 2.0 Type-A host connector USB Type-C connector for FTDI JTAG and debug Expansions 2x PMOD connectors FMC+ connector with PCIe […]