GOWIN Semiconductor has just announced the “Arora V” GW5AT-15 FPGA designed for high-speed video interfaces up to 4K at 120 FPS in space-constrained consumer and automotive applications. Manufactured with TSMC’s 22nm LP process, the new FPGA offers high-performance 12.5 Gbps SerDes, PCIe 3.0, MIPI CPHY, and DPHY interfaces. The GW5AT-15 FPGA also provides 15K LUTs of programmable logic, 118kbit of shadow SRAM, 630kbit of block SRAM (BSRAM), optional 64Mbit or 128Mbit of pseudo-SRAM (PSRAM), and optional 8Mbit of NOR Flash in a tiny 4.9mm x 5.3mm WLCSP package. Target applications include AR/VR headsets, 4K gaming tablets, and car infotainment systems. GOWIN GW5AT-15 FPGA specifications: FPGA Fabric 15120 logic elements (LUT4) 118kbit of shadow SRAM 630kbit of block SRAM (BSRAM) arranged as 35 x 18kbit 28x DSP slices, 12x DSP Lite slices PSRAM GW5ART-15: 64Mbit (in MG132P package) or 128Mbit (in CM90P package) of pseudo SRAM (PSRAM) GW5ANRT-15: 64Mbit PSRAM DDR […]

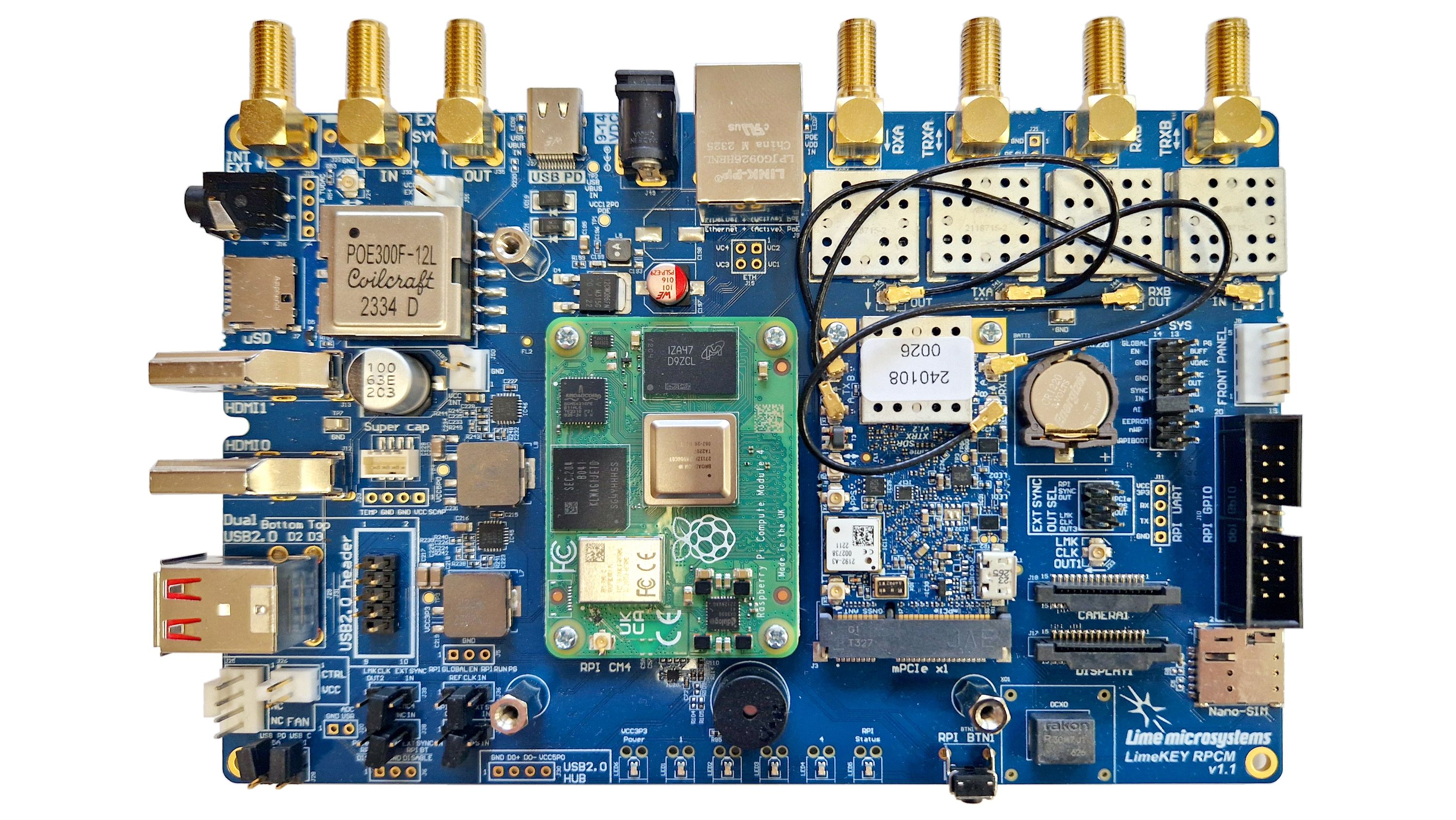

LimeNET Micro 2.0 Developer Edition board leverages Raspberry Pi CM4 and LimeSDR XTRX SDR module (Crowdfunding)

The LimeNET Micro 2.0 Developer Edition board is a modular software-defined radio (SDR) platform from Lime Microsystems that is based on the Raspberry Pi Compute Module 4 and the company’s own SDR board, the LimeSDR XTRX. It builds upon previous versions from Lime Microsystems, such as the LimeSDR Mini and LimeSDR Mini 2.0. It features a MIMO (multiple-input, multiple-output) radio and runs the more powerful Compute Module 4, an upgrade from the Raspberry Pi CM3 in earlier versions. The LimeSDR XTRX is an open-source, high-performance SDR in a compact, Mini PCIe form factor. It provides a platform for building logic-intensive digital and RF designs and can be used for MIMO antenna configurations from 2Tx2R to 32Tx32R. The platform is built around a planar system board, the LimePSB RPCM, which integrates the CM4, the XTRX, and other components and interfaces to make a complete baseband + RF solution for diverse wireless […]

The RPGA Feather dev board pairs RP2040 chip with a Lattice iCE40 FPGA for sensor fusion projects

Oak Development Technologies’ RPGA Feather board integrates the Raspberry Pi RP2040 microcontroller with the iCE5LP4K FPGA from Lattice Semiconductor into a compact development board in the Adafruit Feather form factor. The iCE5LP4K FPGA is an ultra-low-power chip in the iCE40 Ultra product family designed for mobile applications such as smartphones, tablets, and handhelds, while the Raspberry Pi RP2040 microcontroller makes it much easier to program the FPGA using CircuitPython. We have seen Oak Development Technologies’ earlier forays into FPGA Feather-compatible products such as the IcyBlue board (also based on iCE5LP4K FPGA) and the Lattice FeatherWing. RPGA Feather specifications: MCU – Raspberry Pi RP2040 dual-core Cortex-M0+ microcontroller @ 133 MHz with 264KB SRAM FPGA – Lattice Semiconductor iCE5LP4K FPGA Logic Cells – 3,520 logic cells Memory 80 Kbits of embedded Block RAM (EBR) Distributed RAM: 640 bits 2x hardware I2C blocks and 2x hardware SPI blocks 26 I/Os for customized interfaces […]

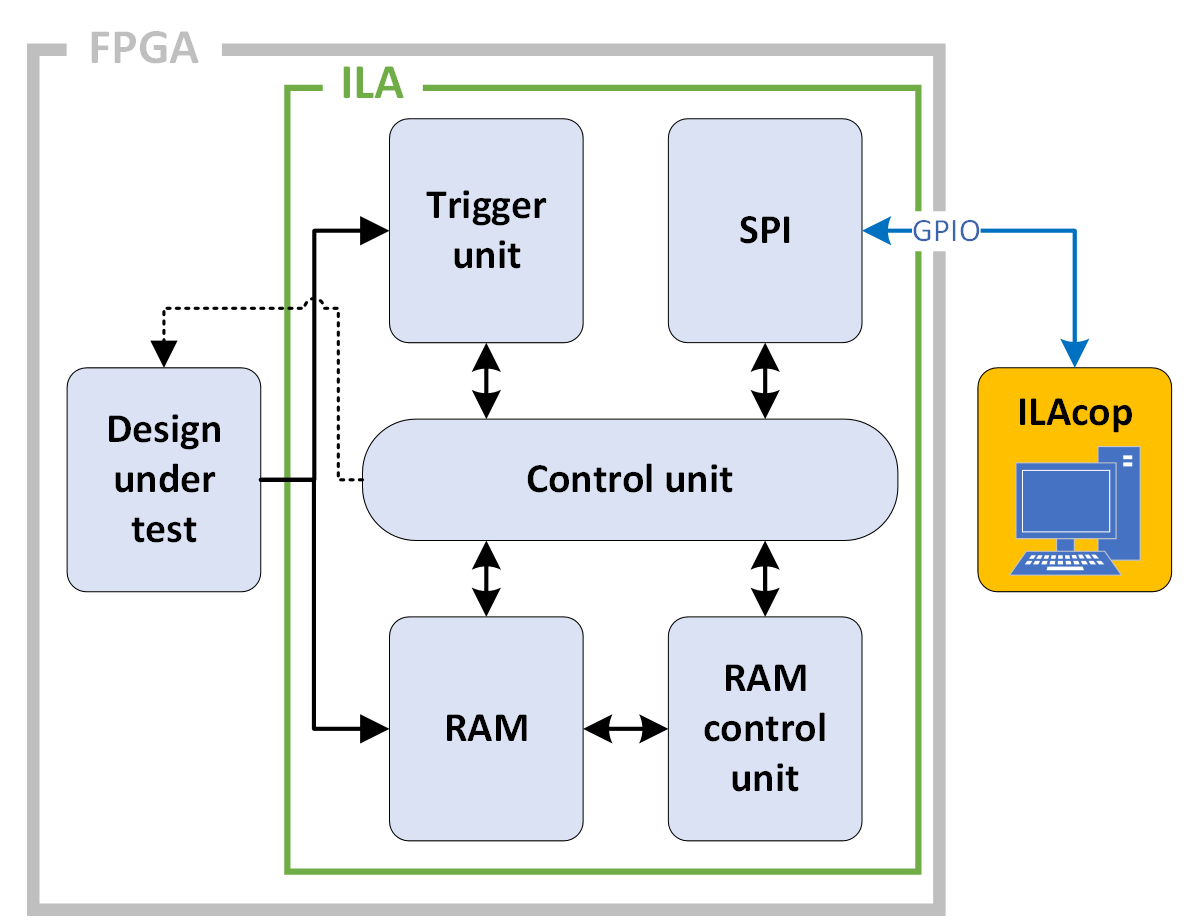

GateMate Integrated Logic Analyzer (ILA) deep dive

CNXSoft: This is a guest article by Dave Fohrn, Embedded Software Engineer at Cologne Chip AG, that goes into detail about the company’s open-source integrated logic analyzer (ILA) for GateMate FPGA chips. A field-programmable gate array (FPGA) is a highly flexible integrated circuit in which complex logic circuits can be configured. They are often used as custom computing units in digital circuits because of their ability to process data quickly and in parallel using individually configured circuits. The digital circuits designed specifically for FPGAs are usually developed in a hardware description language such as Verilog or VHDL and are known as gateware. The term “gate” refers to the configurable digital logic units in the FPGA on which the individual gate circuits are implemented. An effective design can accelerate the computing process by strategically utilizing the various resources available in the FPGA, processing data in parallel, and intelligent implementing pipelining. A […]

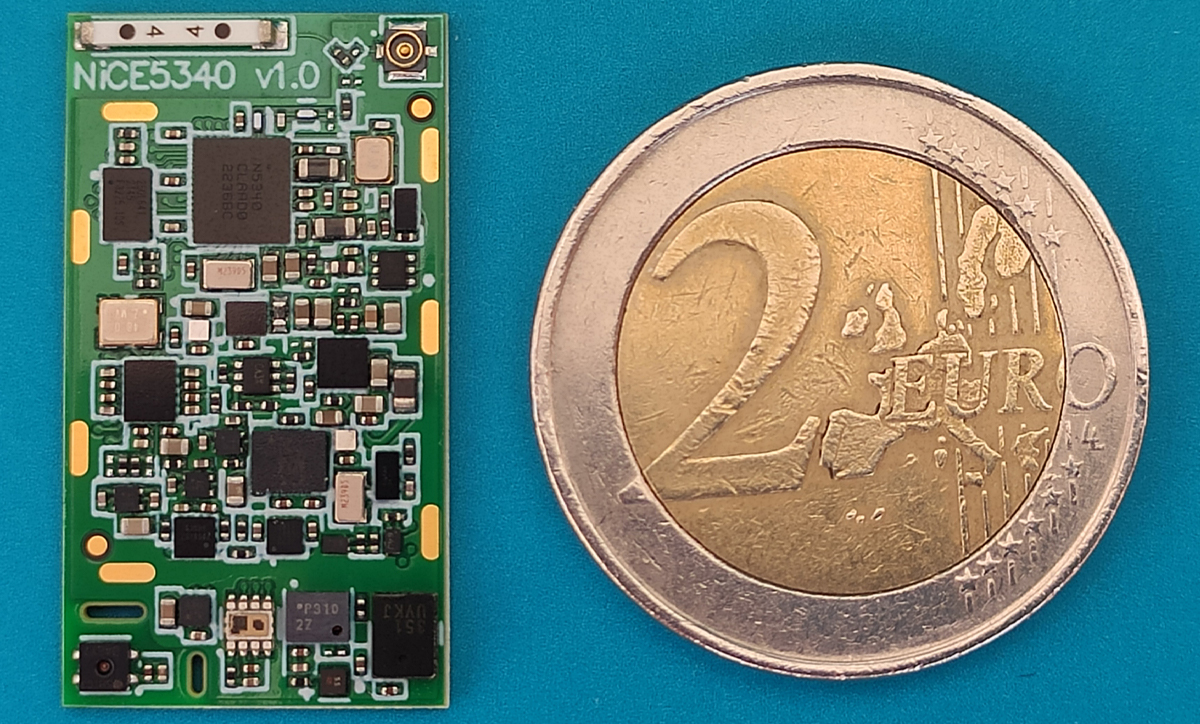

NiCE5340 SoM packs Nordic nRF5340 MCU, Lattice iCE40 FPGA, and 11 sensors into a tiny 29x16mm form factor

Stefano Viola’s NiCE5340 SoM is built around a Nordic Semi nRF5340 Bluetooth SoC, an iCE40 FPGA, 11 sensors, a battery charger, and various other peripherals in a 29×16 mm form factor. The nRF5340 used in the SoM is a low-power, dual-core Arm Cortex-M33 SoC with Bluetooth 5.4, Bluetooth LE (BLE), Thread, Zigbee, and other proprietary protocols. Meanwhile, the Lattice iCE40 FPGA features 3520 logic cells, 80 Kbits of embedded Block RAM, I2C, and SPI blocks, and many other features that make it suitable for applications like environmental monitoring, health tracking, and others. Previously, we have written about Unexpected Maker NANOS3, TinyS3, FeatherS3, and ProS3 boards, and ESP32-S3 4G dev board which all fall under the tiny and compact board category but this is the first time we have seen an MCU board with so many features built into a module of that size. Stefano Viola’s NiCE5340 SoM Specification ICs Nordic […]

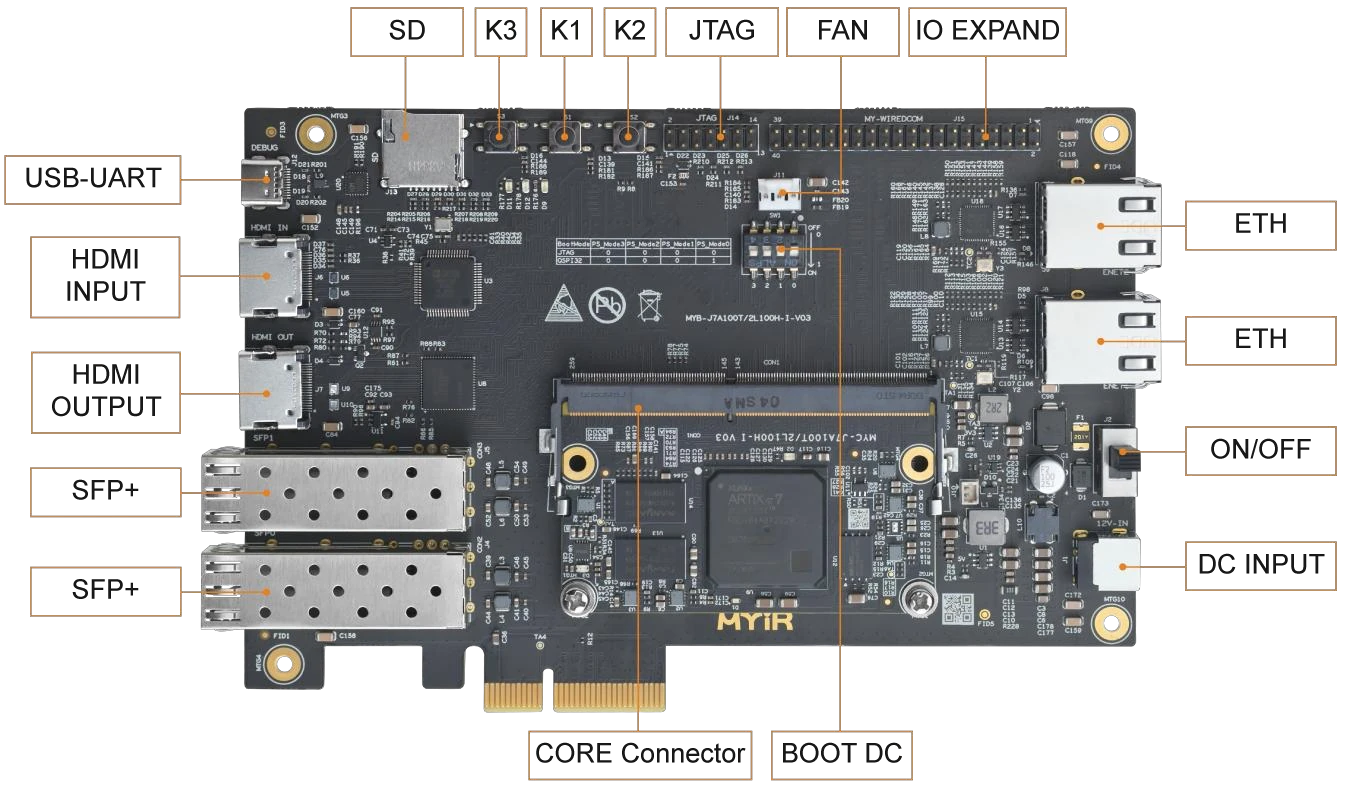

MYiR Tech launches AMD XC7A100T Artix-7 FPGA system-on-module and development board with PCIe, SFP+ cages, dual GbE

MYIR MYC-J7A100T is a System-On-Module (SoM) powered by an AMD/Xilinx Artix-7 XC7A100T FPGA with up to 101,440 logic cells, 512MB DDR3 memory, 32MB QSPI FLASH, 32KB EEPROM, DC-DC power management, and other integral circuits in a compact 69.6 x 40mm form factor. The module exposes up to 178 FPGA I/Os, four pairs of GTP high-speed transceiver interfaces, and a JTAG interface through its 260-pin edge connector. MYiR also provides a development board for the MYC-J7A100T module which looks like a PCIe 2.0 card and comes with SFP+ cages, HDMI input and output ports, dual GbE, and a GPIO expansion header. MYIR MYC-J7A100T system-on-module Specifications: FPGA – AMD/Xilinx XC7A100T Artix-7 FPGA (XC7A100T-2FGG484I) with 101,440 logic cells 4,860 Kb of Block RAM 240 DSP slices 8 GTP transceivers capable of reaching speeds up to 6.6Gb/s PCIe Gen2 x4 interface Up to 300x single-ended I/Os System Memory – 512MB DDR3 Storage – 32MB […]

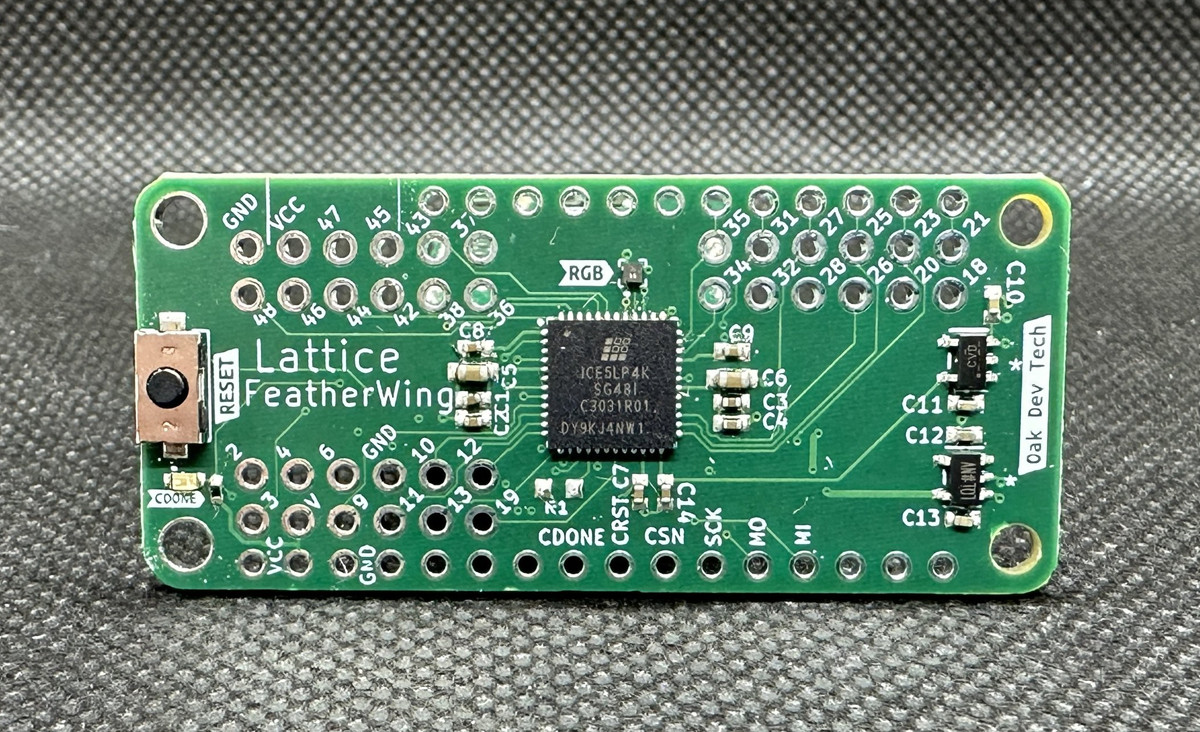

Lattice FeatherWing – An iCE40-powered add-on FPGA board for Adafruit Feather

Oak Development Technologies has recently announced Lattice FeatherWing – An iCE40-based development board designed to be controlled by Adafruit Feather. Previously we wrote about the IcyBlue Feather V2, a standalone development built around a Lattice Semi iCE5LP4K FPGA. But this FeatherWing board is designed to add functionality to your existing Adafruit Feather board. The Lattice FeatherWing expands your Adafruit Feather with a Lattice iCE5LP4K FPGA. It connects and gets programmed over SPI so you can use all the FPGA’s GPIO pins through the header blocks. There’s also a built-in RGB LED directly connected to the FPGA’s open-drain pins, for visual feedback. Previously, we have written about many Lattice Semi FPGA-based development boards, such as the tinyVision.ai Pico-Ice board, Silicon Witchery S1, and ULX3S Education Board. Feel free to check those out if you want a standalone FPGA board. FPGA – Lattice Semi iCE40 Family ICE5LP4K-SG48ITR Logic Cells – Approximately 3520 logic cells Memory – 80 Kbits […]

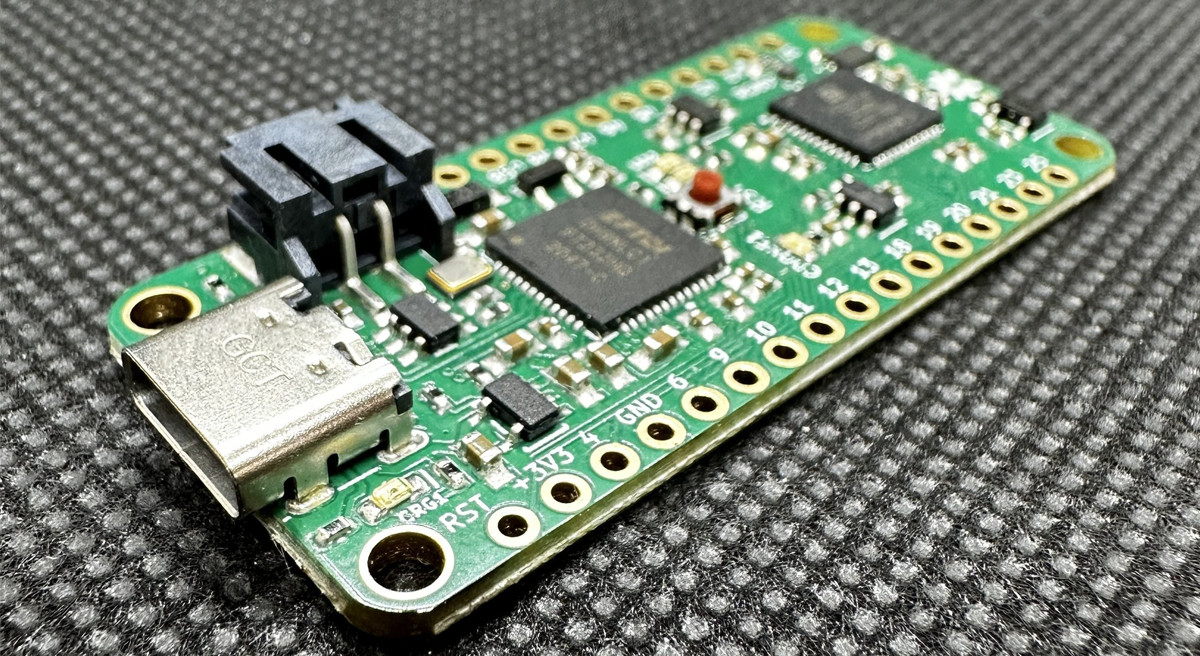

IcyBlue Feather V2 board features Lattice Semi iCE5LP4K FPGA in Adafruit Feather form factor

The IcyBlue Feather V2 from Oak Development Technologies is a powerful and compact dev board that combines the Lattice Semi iCE5LP4K FPGA with the Adafruit Feather form factor. This unique combination allows this FPGA board to be compatible with the Adafruit FeatherWings ecosystem, providing functionalities such as additional GPIOs, displays, connectivity modules, and more. This new board features a USB-C port for powering and programming the FPGA. Additionally, it features two hardware I2C and SPI blocks that do not consume FPGA resources while operating. The board also includes 22 accessible GPIOs, a bright RGB LED for status indication, and two user-programmable LEDs. Previously, we have discussed many similar tiny FPGA-based development boards, such as the Lattice Semi MachXO2 FPGA, tinyVision.ai Pico-Ice board, Silicon Witchery S1, and ULX3S Education Board. Feel free to explore these if you are looking for similar options. IcyBlue Feather V2 Specification FPGA – Lattice Semi iCE40 […]