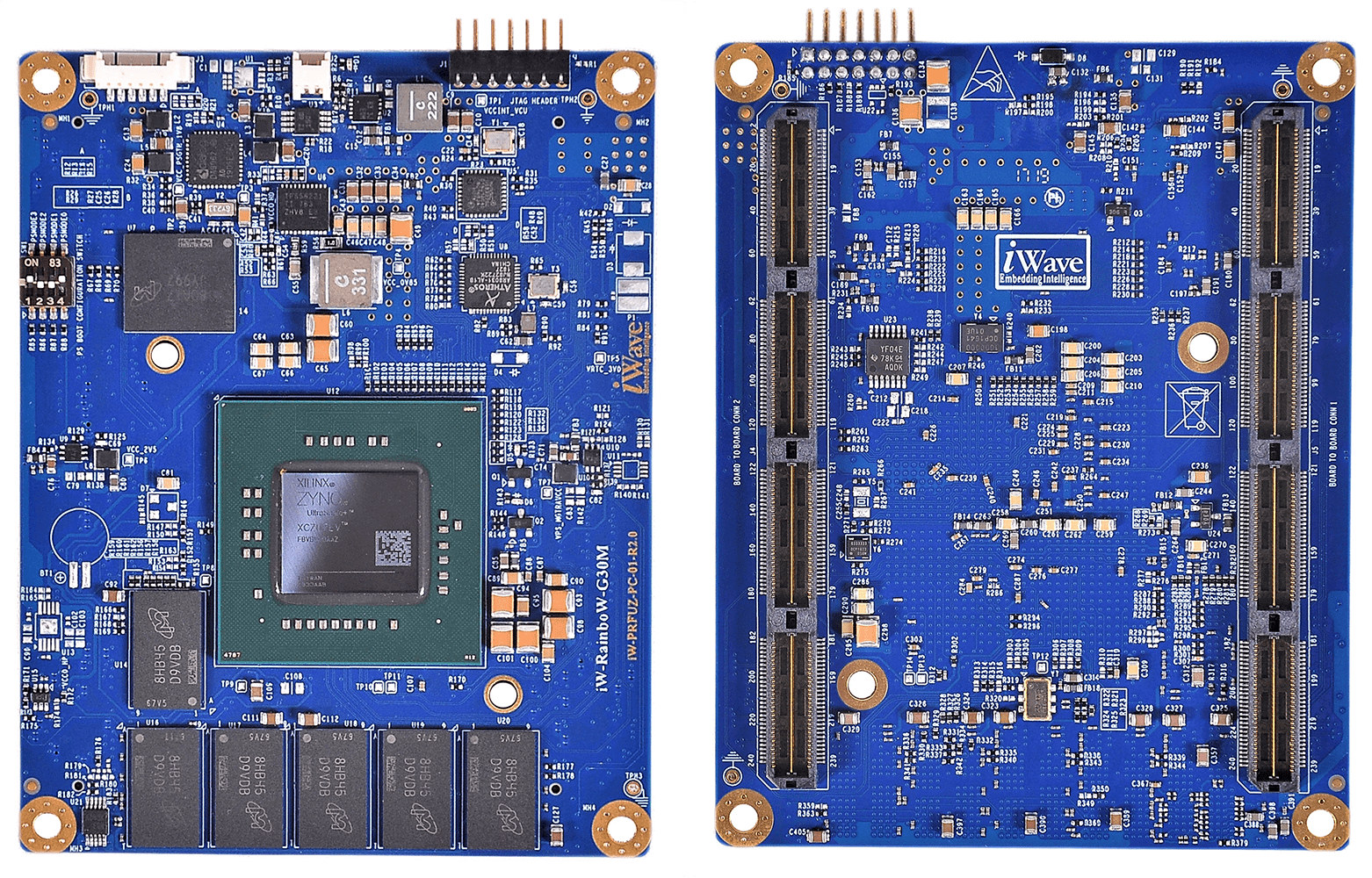

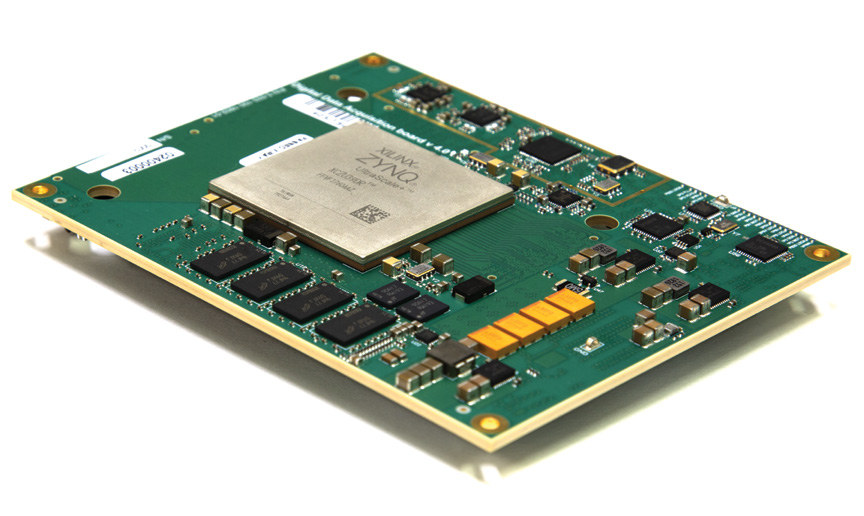

iWave Systems iW-RainboW-G30M is a system-on-module (SoM) based on AMD Xilinx Zynq UltraScale+ ZU4/ZU5/ZU7 FPGA MPSoC specially geared towards LiDAR applications for scientific and military applications. The module comes with up to 12GB of RAM, 4GB for the programmable logic (PL) and 8GB for the Arm Cortex-A53/R5-based Processing System (PS), two 240-pin high-density, high-speed connectors with 142 user I/Os, 16x GTH transceivers up to 16.3Gbps, and four GTR transceivers up to 6Gbps. iW-RainboW-G30M specifications: FPGA MPSoC – AMD Xilinx Zynq Ultrascale+ ZU4, ZU5, or ZU7 MPSoC with Processing System (PS) featuring 2x or 4x Arm Cortex-A53 core @ 1.5 GHz, two Cortex-R5 cores @ 600MHz, H.264/H.265 Video Encoder/Decoder (VCU), ARM Mali-400MP2 GPU @ 677MHz, and Programming Logic (PL)/FPGA with up to 504K Logic cells & 230K LUTs System Memory 4GB DDR4 64-bit RAM with ECC for PS (upgradeable up to 8GB) 2GB DDR4 16-bit RAM for PL (upgradeable up to […]

Linux 6.0 release – Main changes, Arm, RISC-V, and MIPS architectures

Linux 6.0 has just been released by Linus Torvalds: So, as is hopefully clear to everybody, the major version number change is more about me running out of fingers and toes than it is about any big fundamental changes. But of course there’s a lot of various changes in 6.0 – we’ve got over 15k non-merge commits in there in total, after all, and as such 6.0 is one of the bigger releases at least in numbers of commits in a while. The shortlog of changes below is only the last week since 6.0-rc7. A little bit of everything, although the diffstat is dominated by drm (mostly amd new chip support) and networking drivers. And this obviously means that tomorrow I’ll open the merge window for 6.1. Which – unlike 6.0 – has a number of fairly core new things lined up. But for now, please do give this most […]

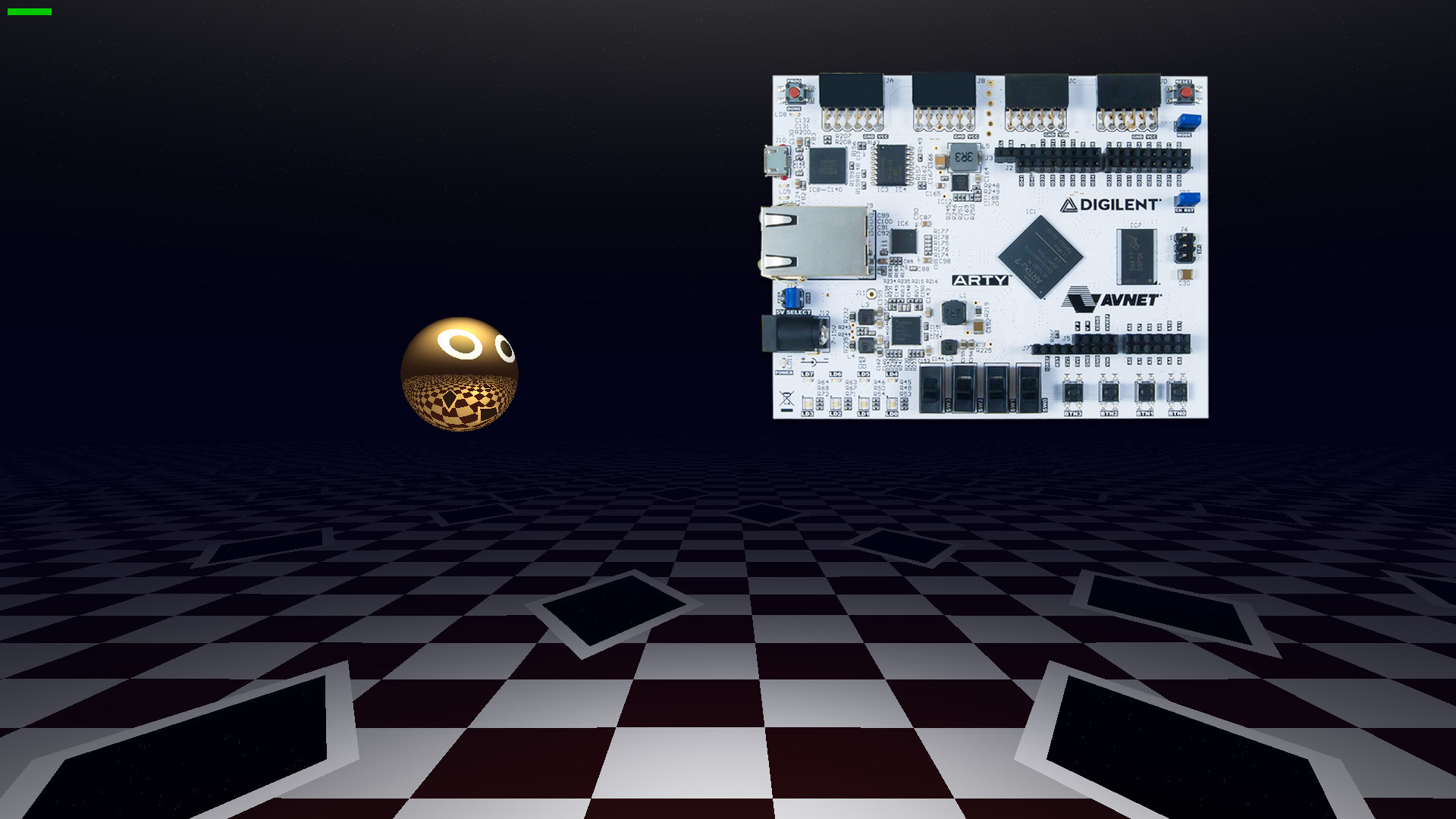

3D game running on FPGA shown to be 50x more efficient than on x86 hardware

Sphery vs. shapes is an open-source 3D raytraced game written in C and translated into FPGA bitstream that runs 50 times more efficiently on FPGA hardware than on an AMD Ryzen processor. Verilog and VHDL languages typically used on FPGA are not well-suited to game development or other complex applications, so instead, Victor Suarez Rovere and Julian Kemmerer relied on Julian’s “PipelineC” C-like hardware description language (HDL) and Victor’s CflexHDL tool that include parser/generator and math types library in order to run the same code on PC with a standard compile, and on FPGA through a custom C to VHDL translator. More details about the game development and results are provided in a white paper. Some math functions were needed, including: floating point addition, subtraction, multiplication, division, reciprocals, square root, inverse square roots, vector dot products, vector normalization, etc. Fixed point counterparts were also used for performance reasons and to […]

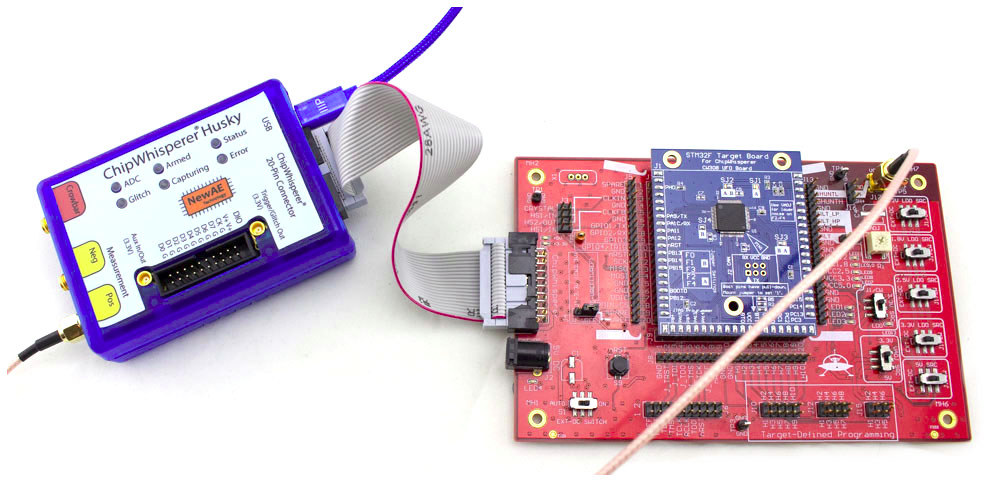

ChipWhisperer-Husky is a palm-sized power analysis and fault injection tool (Crowdfunding)

NewAE Technology’s ChipWhisperer-Husky is a compact tool designed for side-channel power analysis and fault injection with features such as a high-speed logic analyzer used to visualize glitches, real-time data streaming for attacking asymmetric algorithms, and support for JTAG/SWD programming. The security research company explains its device delivers a more stable and reliable experience compared to other off-the-shelf test gear such as oscilloscopes and function generators thanks to features such as synchronous sampling, which means the sample clock of your target device and the sample clock of ChipWhisperer-Husky can be perfectly aligned, or the ability to generate glitches, including clock glitches that can be less than a nanosecond wide. ChipWhisperer-Husky key features and hardware specifications: Synchronous clock for capture board and target board for significantly improved performance over a typical asynchronous oscilloscope setup 12-bit 200MS/s ADC for capturing power traces – It can be clocked at both the same clock […]

Ztachip open-source RISC-V AI accelerator performs up to 50 times faster

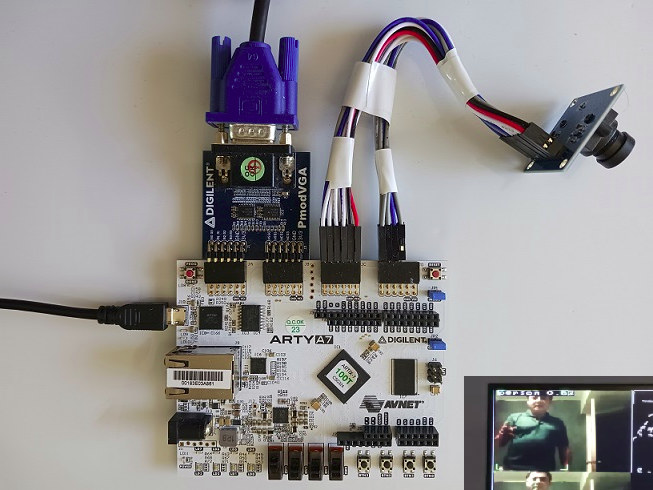

Ztachip is an open-source RISC-V accelerator for vision and AI edge applications running on low-end FPGA devices or custom ASIC that is said to perform 20 to 50 times faster than on non-accelerated RISC-V implementations, and is also better than RISC-V cores with vector extensions (no numbers were provided here). Ztachip, pronounced zeta-chip, is not tied to a particular architecture, but the example code features a RISC-V core based on the VexRiscv implementation and can accelerate common computer vision tasks such as edge detection, optical flow, motion detection, color conversion, as well as TensorFlow AI models without retraining. The open-source AI accelerator has been tested on Digilent ArtyA7-100T FPGA board in combination with a PMOD VGA module to connect to a display and an OV7670 VGA camera module. You can then build the sample found on Github with the Xilinx Vivado Webpack free edition and flash it to the board […]

$5 CH347 board is a USB 2.0 bridge to I2C, SPI, UART, JTAG, and GPIO

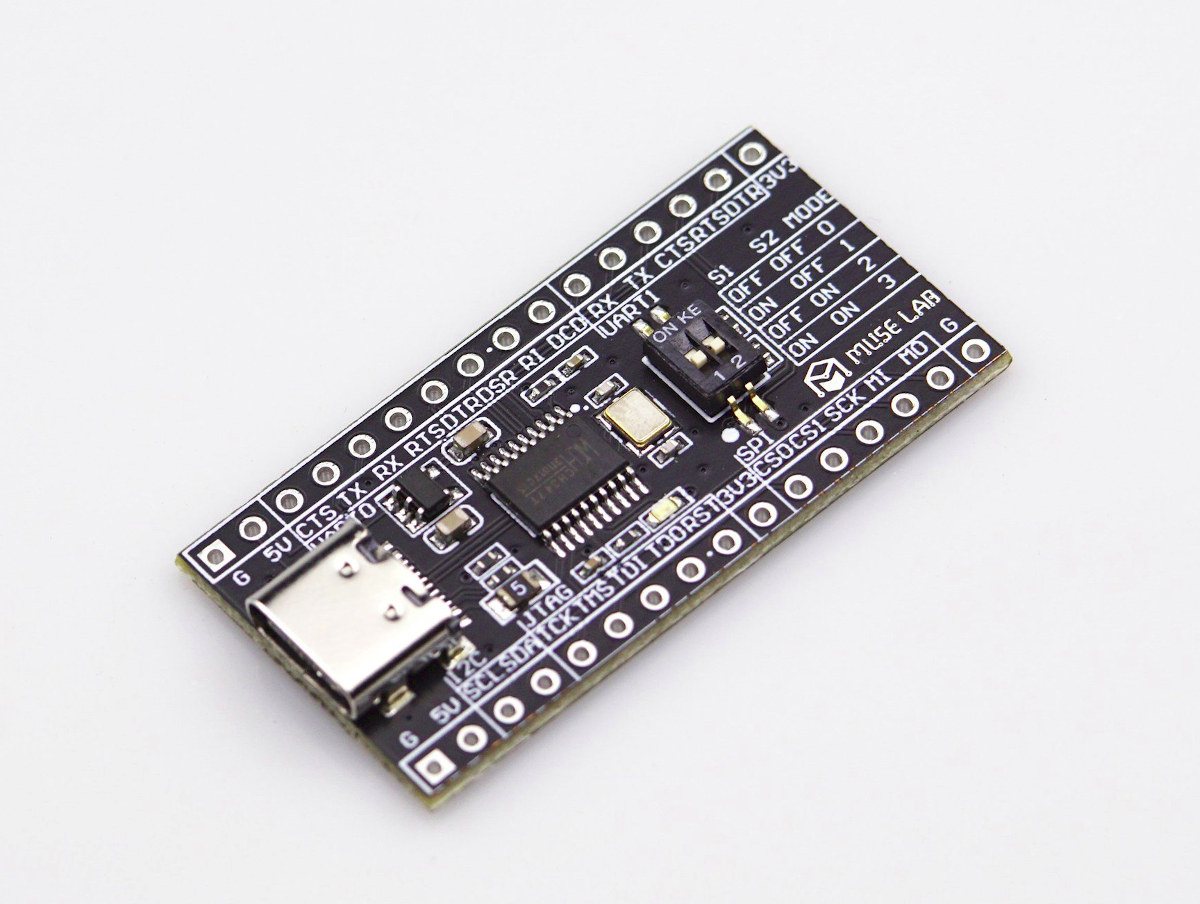

MuseLab USB-HS-Bridge is an inexpensive ($5) board based on WCH CH347 chip with a USB 2.0 Type-C interface that acts as a bridge for I2C, SPI, UART, and JTAG interfaces, as well as GPIOs. It’s notably useful to debug and download bitstreams to FPGA development boards, but it can also be used to connect various peripherals such as I2C sensors, SPI flash devices, UART devices to basically any host with a spare USB 2.0 host port. USB-HS-Bridge specifications: Chip – WCH CH347 high-speed USB to UART, I2C, SPI and JTAG chip (See link to the datasheet for details) USB – 1x USB 2.0 Type-C port with up to 480 Mbps data rate I/Os – 2x 16-pin header with 2x UART interfaces up to 9 Mbps baudrate 1x I2C for EEPROM or sensors 1x SPI master interface with 2 chip select signals to control up to 2x SPI slave devices. The […]

Acromag XMC-7A50-AP323 – An XMC module based on AMD Xilinx Artix-7 FPGA

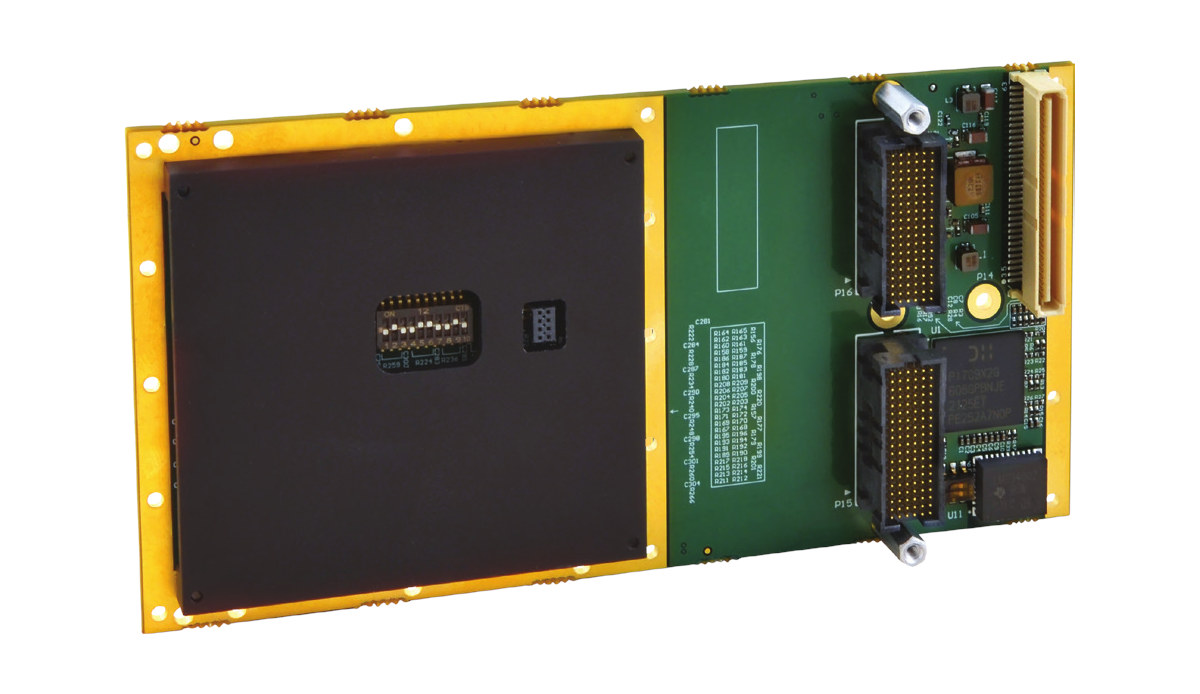

Acromag XMC-7A50-AP323 is an XMC (Switched Mezzanine Card) module based on a Xilinx Artix-7 FPGA with 48 TTL I/O channels plus a 16-bit ADC for 20 differential or 40 single-ended analog inputs. Designed for commercial off-the-shelf (COSTS) applications, Acromag XMC modules are RoHS compliant, and suitable for automation applications, scientific development labs, as well as aerospace and military applications. Acromag XMC-7A50-AP323 module specifications: FPGA – AMD Xilinx Artix-7 (XC7A050) FPGA with 52,160 logic cells, 65,200 Flip flops, 2,700 kb block RAM, 120 DSP slices Storage – 32Mbit QSPI flash memory FPGA Digital I/O 48x I/O channels controlled in groups of eight channels, 5V tolerant TTL, RS485, and LVDS interface options: Build Option A: 24x EIA-485/422 channels Build Option B: 24x TTL and 12x EIA-485/422 channels Build Option C: 24x LVDS channels Analog Input 20 differential or 40 single-ended inputs Flexible scan control 16-bit A/D resolution 8μs conversion time FIFO buffer […]

XRF16 Gen3 SOM features Xilinx Zynq UltraScale+ ZU49DR RFSoC with up to 6GHz bandwidth

We’ve written about Xilinx Zynq UltraScale+ MPSoCs that combine Arm Cortex-A53/R5 cores and Mali-400 GPU with Ultrascale FPGA fabric several times over the course of a few years. But AMD-Xilinx also offers the Zynq UltraScale+ RFSoC single-chip adaptable radio platforms that support up to 7.125GHz analog bandwidth. The topic came to my attention because of an upcoming ZU49DR SoM from iWave Systems that seems to be under development but also noticed Avnet had launched a solution last year with the XRF16 Gen3 SoM featuring the same third-generation Zynq Ultrascale+ ZU49DR RFSoC with 16 RF-ADC, 16 RF-DAC channels, and 6GHz RF bandwidth. Avnet XRF16 specifications: Main chip – Xilinx Zynq UltraScale+ Gen3 ZU49DR RFSoC with Quad-core Arm Cortex-A53 processing subsystem Dual-core Arm Cortex-R5F MPCore up to 533MHz 16x ADCs, 14-bit up to 2.5 GSPS 16x DACs, 14-bit up to 9.85 GSPS (10 GSPS Available) 1 GbE, PCIe Gen1/2, SATA, USB2/3 UltraScale+ […]