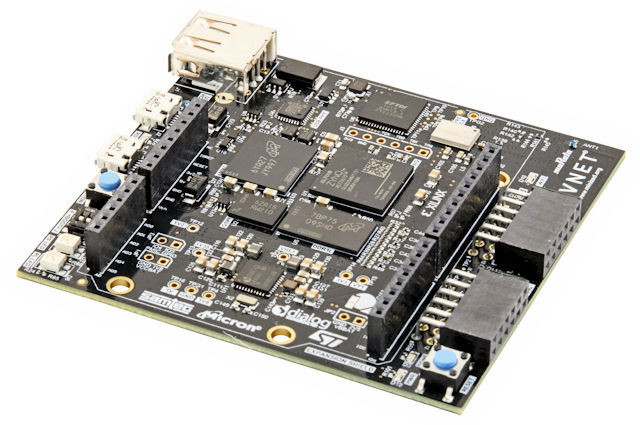

Avnet has unveiled MiniZed development board – part of ZedBoard family – powered by a Xilinx Zynq Z-7007s SoC with an ARM Cortex A9 processor and FPGA fabric, supporting WiFi and Bluetooth connectivity, and equipped with Arduino and PMOD headers. MiniZed board (AES-MINIZED-7Z007-G) specifications: SoC – Xilinx Zynq-7007S single ARM Cortex A9 processor up to 677 MHz + FPGA with 23K logic cells, 1.8 Mb block RAM, 60 DSP slices System Memory – 512 MB DDR3L Storage – 8 GB eMMC flash, 128 Mbit QSPI flash Connectivity – Wi-Fi 802.11b/g/n and Bluetooth 4.1 plus EDR and BLE via Murata “Type 1DX” wireless module USB – 1x USB 2.0 host port Sensors – 3-axis accelerator and temperature sensor (LIS2DS12); Digital Microphone (MP34DT05) Expansion Interfaces: 2x Pmod compatible connectors with 16x GPIOs Arduino UNO R3 compatible header with 22x GPIOs Debugging – JTAG and serial console via micro USB port Misc – 2x […]

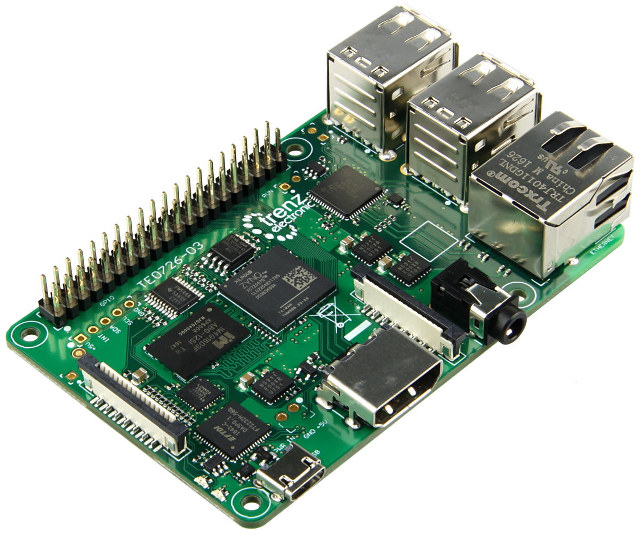

Meet Zynqberry, a Xilinx Zynq FPGA Board with Raspberry Pi 2/3 Form Factor

Earlier this year, I wrote about Trenz Electronic’s Xilinx Zynq Ultrascale+ system-on-module, but I’ve just found out I missed another interesting product from the company. The ZynqBerry is a board powered by Zilinx Zync Z-7007S or Z-7010 ARM + FPGA SoC with Raspberry Pi 2/3 form factor. ZynqBerry specifications: SoC Xilinx Zynq XC7Z007S-1CLG225C (Z-7007S) single core ARM Cortex-A9 MPCore up to 766MHz + FPGA with 23K logic cells Xilinx Zynq XC7Z010-1CLG225C (Z-7010) dual core ARM Cortex-A9 MPCore up to 866 MHz + FPGA with 28K logic cells System Memory – 128 or 512 MB DDR3L Storage – 16 MB Flash SPI flash + micro SD card slot Video Output – HDMI, MIPI DSI interface Audio Output – HDMI, 3.5mm audio jack (PWM audio only) Connectivity – 100 MBit Ethernet via (LAN9514 USB Hub with Ethernet USB – 4x USB 2.0 host ports Camera – MIPI CSI-2 interface Expansion – 40-pin Raspberry […]

LEDE 17.01.0 “Reboot” Router Operating System Released

LEDE (Linux Embedded Development Environment) is a fork of OpenWrt after some disagreements between developers, and while there are talks about merging OpenWrt and LEDE development, this is not done yet, and LEDE 17.01 has been released a few days ago. Some of notable LEDE 17.01 changes include: Linux kernel updated to version 4.4.50 (from 3.18 in Chaos Calmer) Update to dnsmasq 2.76, busybox 1.25.1, mbedtls 2.4.0, openssl 1.0.2k Improved Security Features Improved Networking Support Added new targets: apm821xx (AppliedMicro APM821xx) arc770 (Synopsys DesignWare ARC 770D) archs38 (Synopsys DesignWare ARC HS38) armvirt (QEMU ARM Virtual Machine) ipq806x (Qualcomm Atheros IPQ806X) layerscape (NXP Layerscape) zynq (Xilinx Zynq 7000 SoCs) Reorganized x86 target – Drop dedicated Xen DomU target, merged with x86/generic * Enable AES-NI support Build system improvements Image Builder / SDK – Rework library bundling to allow for better portability between different Linux distributions, added support for building kernel modules […]

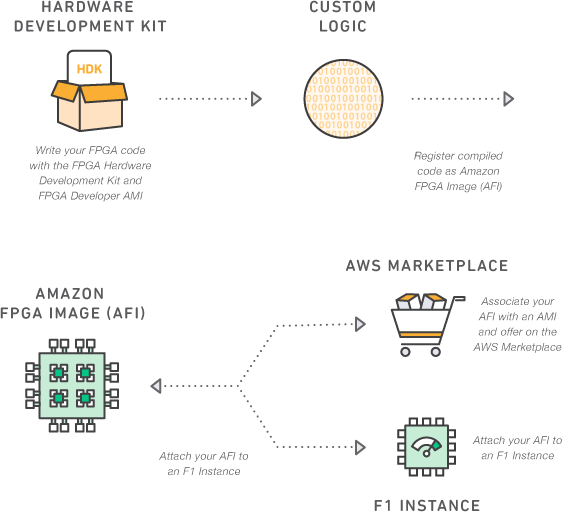

Amazon EC2 F1 Instances Put Xilinx Virtex Ultrascale+ FPGA Boards into the Cloud

We’ve covered several board and modules based on Xilinx Zynq Ultrascale+ MPSoC such as the AXIOM Board and Trenz TE0808 SoM, both featuring ZU9EG MPSoC, with systems selling for several thousands dollars. But I’ve been informed you may not need to purchase a board to use Virtex UltraScale+ FPGAs, which are different from Zynq UltraScale+ since they lack the ARM CPU & GPU and normally feature a more capable FPGA, as last November, Amazon launched a developer preview of F1 instances giving access to this type of hardware from their cloud. That’s the FPGA hardware you’ll be able to access from one F1 instance: Xilinx UltraScale+ VU9P manufactured using a 16 nm process. 64 GB of ECC-protected memory on a 288-bit wide bus (four DDR4 channels). Dedicated PCIe x16 interface to the CPU. Approximately 2.5 million logic elements. Approximately 6,800 Digital Signal Processing (DSP) engines. Virtual JTAG interface for debugging. […]

Trenz Electronic TE0808 UltraSOM+ is a Xilinx Zynq Ultrascale+ ZU9EG System-on-Module

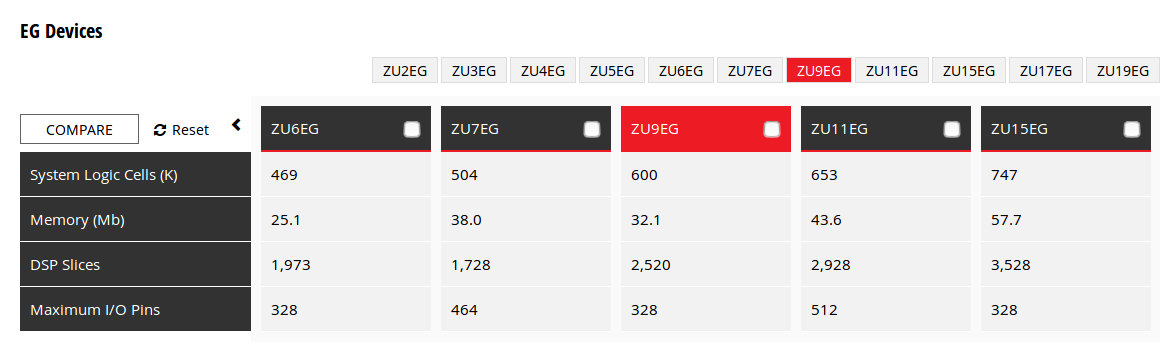

Xilinx Zynq Ultrascale+ ARM Cortex A53 + FPGA SoC have now started to show up in boards such as AXIOM Board based on Zynq Ultrascale+ ZU9EG. Price for the board has not been announced, and while a similar Xilinx development kit goes for close to $3,000, some people are expecting the board to sell for $400 to $600. Since the price of FPGA vary a lot from a few dollars to $40,000 for the top end chips, I decided to find pricing info about Xilinx Zynq Ultrascale+ MPSoCs which lead me to Trenz Electronic TE0808 system-on-module, which was unveiled in May last year, and I’ll cover in the second part of this post, after – hopefully quickly – describing Zynq Ultrascale+ family and nomenclature, and addressing the price “issue”. First, there are three sub-families within Zynq Ultrascale+ MPSoC portfolio: CG models with 2x Cortex A53, 2x Cortex R5, FPGA fabric […]

EU funded AXIOM Board is Powered by Xilinx Zynq UltraScale+ FPGA + ARM SoC

Back in 2015, Xilinx unveiled Zynq Ultrascale+ MPSoC combining ARM Cortex A53 & Cortex R5 cores, a Mali-400MP2 GPU, and UltraScale FPGA, and the company recently launched ZCU102 Evaluation Kit based on the SoC, which sells for just under $3,000. But if you are based in the European Union, you’ll be glad to learn about 4 millions Euros of your taxes have been spent to design a board based on the same MPSoC family as part of the AXIOM project, which was developed in collaboration with European universities and companies with the “aim of researching new software/hardware architectures for Cyber-Physical Systems (CPS) to meet the expectations” in terms of computational power, energy efficiency, scalability through modularity, easy programmability, and leverage of the best existing standards at minimal costs. AXIOM (Agile, eXtensible, fast I/O Module) board’s key specifications: SoC – Xilinx Zynq Ultrascale+ ZU9EG MPSoC with four ARM Cortex A53 cores […]

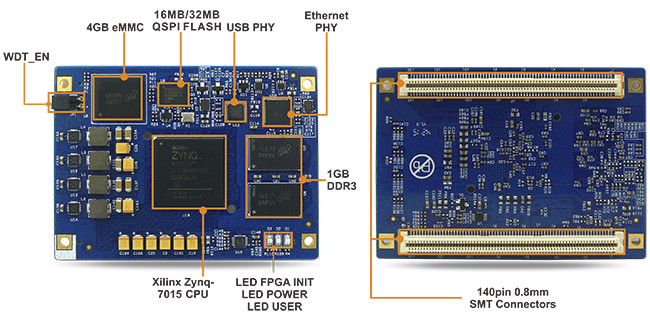

MYIR Tech Latest SoM and Development Board Feature Xilinx Zynq-7015 ARM + FPGA SoC with 4 High Speed Transceivers

MYIR Tech launched the low cost Z-Turn board powered by Xilinx Zynq-7010/7020 ARM+FPGA SoC last year, and the company has now introduced a new system-on-module powered by Xilinx Zynq-7015 SoC as well as a corresponding development kit. MYC-C7Z015 CPU Module specifications: SoC – Xilinx XC7Z015-1CLG485C (Zynq-7015) dual core ARM Cortex-A9 processor @ 667 MHz (up to 866MHz) with Artix-7 class FPGA subsystem with 74K logic cells, 46,200 LUTs, 160 DSP slices, 4x high-speed SerDes transceivers up to 6.25 Gbps, 4x four PCIe Gen2 hardened, integrated IP blocks System Memory – 1GB DDR3 SDRAM Storage – 4GB eMMC flash, 32MB QSPI Flash (16MB optional) Connectivity – 1x Ethernet PHY, 1x USB PHY I/Os and peripherals via 2x 140-pin board-to-board connectors: 1x Gigabit Ethernet 1x USB OTG 2.0 Up to 2x serial ports, up to 2x I2C, up to 2x CAN BUS, 1x SPI 1x independent differential ADC, 16-channel ADC 1x SDIO […]

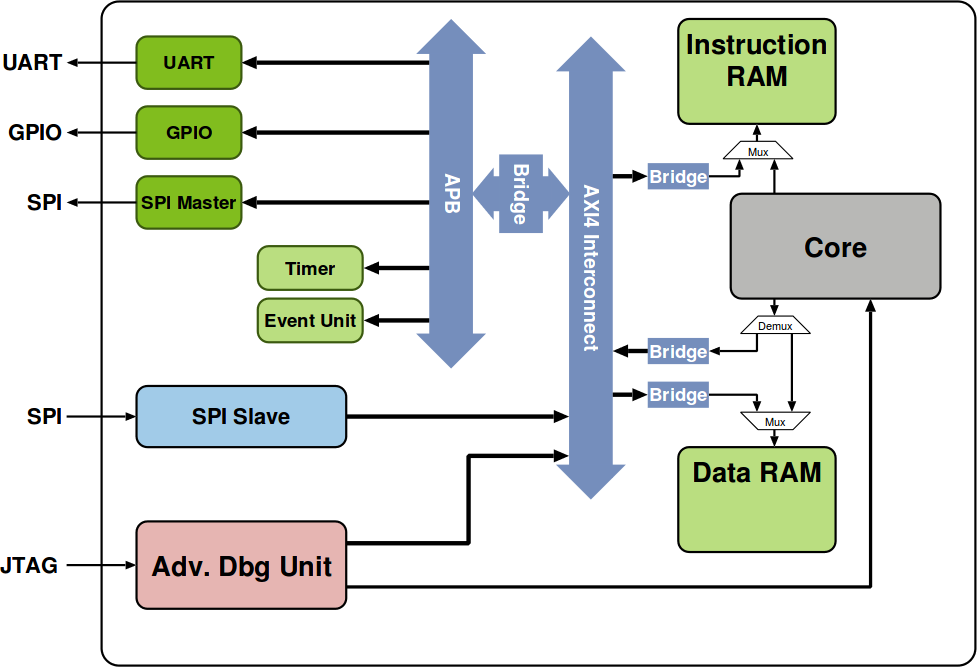

PULPino Open Source RISC-V MCU is Designed for IoT and Wearables

lowRISC is not the only open source processor project based on RISC-V instructions, as researchers at ETH Zurich university and the University of Bologna have developed PULPino open-source processor based on RISC-V instructions set, optimized for low power consumption, and targeting wearables and the IoT applications. PULPino is a single core processor derived from the PULP project (Parallel Ultra-Low-Power Platform) featuring a quad core RISC-V SoC with new RI5CY Signal Processing ISA extensions designed by the universities. The core has an IPC (instructions per cycle) close to 1, full support for the base integer instruction set (RV32I), compressed instructions (RV32C) and partial support for the multiplication instruction set extension (RV32M). PULPino also features peripherals such as I2S, I2C, SPI and UART. PULPino has already been taped out as an ASIC in UMC 65nm at the beginning of the year, but the RTL code be run on Xilinx Zynq-7010 powered Zedboard, […]