Linux 5.18 is out! Linus Torvalds has just announced the release on lkml: No unexpected nasty surprises this last week, so here we go with the 5.18 release right on schedule. That obviously means that the merge window for 5.19 will open tomorrow, and I already have a few pull requests pending. Thank you everybody. I’d still like people to run boring old plain 5.18 just to check, before we start with the excitement of all the new features for the merge window. The full shortlog for the last week is below, and nothing really odd stands out. The diffstat looks a bit funny – unusually we have parsic architecture patches being a big part of it due to some last-minute cache flushing fixes, but that is probably more indicative of everything else being pretty small. So outside of the parisc fixes, there’s random driver updates (mellanox mlx5 stands out, […]

Linux 5.17 release – Main changes, Arm, RISC-V, and MIPS architectures

Linus Torvalds has just released Linux 5.17: So we had an extra week of at the end of this release cycle, and I’m happy to report that it was very calm indeed. We could probably have skipped it with not a lot of downside, but we did get a few last-minute reverts and fixes in and avoid some brown-paper bugs that would otherwise have been stable fodder, so it’s all good. And that calm last week can very much be seen from the appended shortlog – there really aren’t a lot of commits in here, and it’s all pretty small. Most of it is in drivers (net, usb, drm), with some core networking, and some tooling updates too. It really is small enough that you can just scroll through the details below, and the one-liner summaries will give a good flavor of what happened last week. Of course, this means […]

StarFive Dubhe 64-bit RISC-V core to be found in 12nm, 2 GHz processors

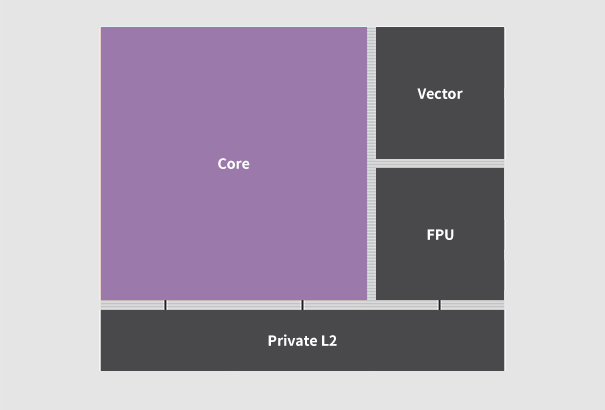

StarFive has just announced customers’ delivery of the 64-bit RISC-V Dubhe core based on RV64GC ISA plus bit manipulation, user-level interrupts, as well as the latest Vector 1.0 (V) and Hypervisor (H) instructions. StarFive Dubhe can be clocked up to 2 GHz on a 12nm TSMC process node, and the company also released performance numbers with a SPECint2006 score of 8.9/GHz, a Dhrystone score of 6.6 DMIPS/MHz, and a CoreMark score of 7.6/MHz. A third-party source told CNX Software it should be equivalent to the SiFive Performance P550 RISC-V core announced last summer, itself comparable to Cortex-A75. StarFive Dubhe highlights: Typical frequency – 2.0 GHz @ TSMC 12nm “Industry-leading” Power and Area Efficiency (TSMC 12nm) RISC-V Vector Extension Data types: floating point, fixed point and integer VLEN=128-1024bits ALU & data path width=128 or 256 bits Full vector register grouping (LMUL) support RISC-V Virtualization Extension Pre-integrated Multi-Core with Memory Coherency Support […]

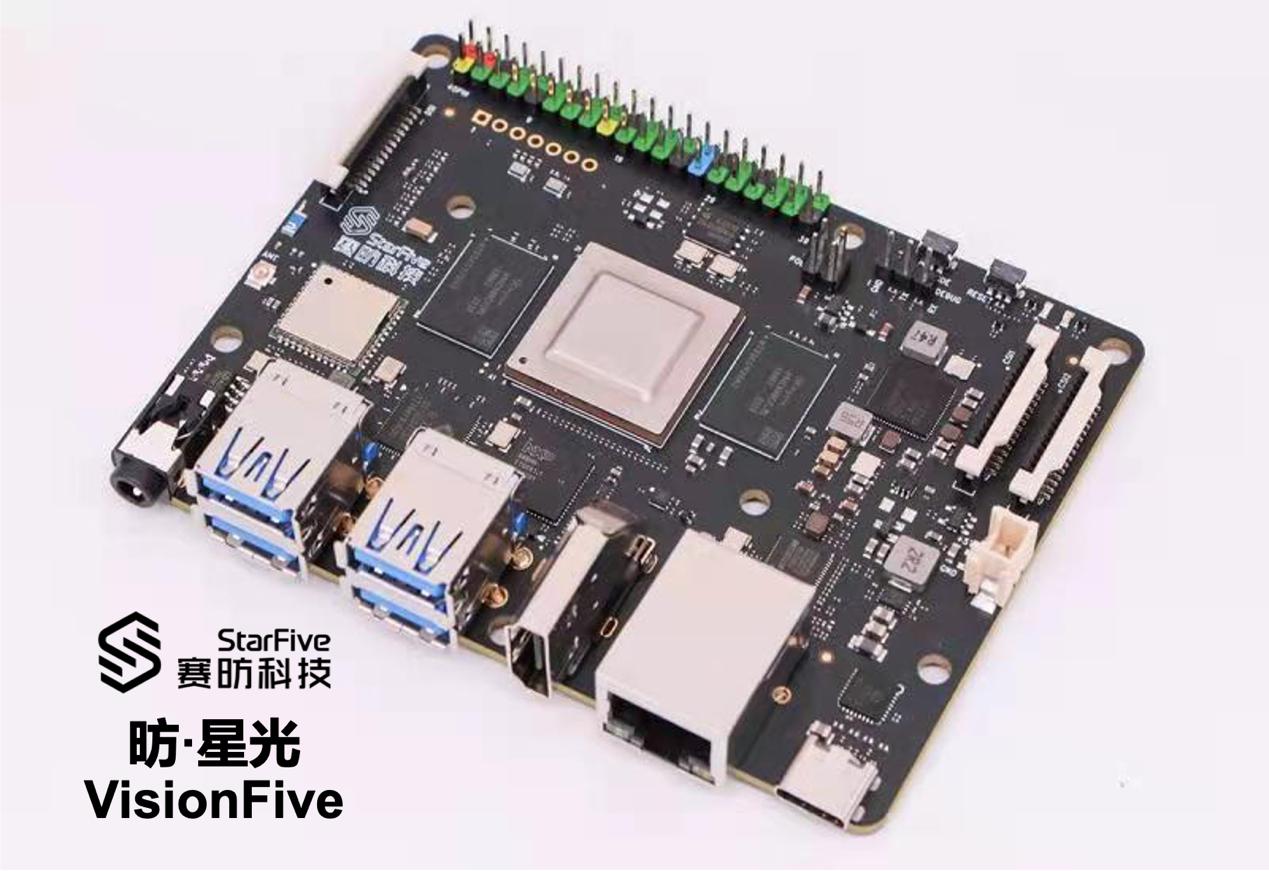

StarFive VisionFive single board computer officially for sale, accelerating RISC-V ecosystem development (Sponsored)

San Francisco, U.S. – Dec. 8, 2021- at RISC-V Summit 2021, StarFive Technology Co., Ltd. (hereinafter “StarFive”), the leader of RISC-V software and hardware ecosystem in China, announced that “VisionFive” single-board computer is officially for sale. The availability of VisionFive signifies a breakthrough in RISC-V hardware for high-end applications to help accelerate the innovations of the global RISC-V industry and promote the improvement and development of the open-source software ecosystem to drive the realization of more innovative top-layer RISC-V applications. VisionFive open-source hardware enables a new level of innovation for the RISC-V ecosystem VisionFive, the first generation of cost-effective RISC-V single-board computer is designed to run Linux, with StarFive’s JH7100 vision processing SoC. The JH7100 SoC is equipped with a 64-bit high-performance RISC-V dual-core processor with a 2MB L2 cache, running at 1.5GHz, which is excellent for high-performance computing. The JH7100 SoC is further equipped with the deep learning processing […]