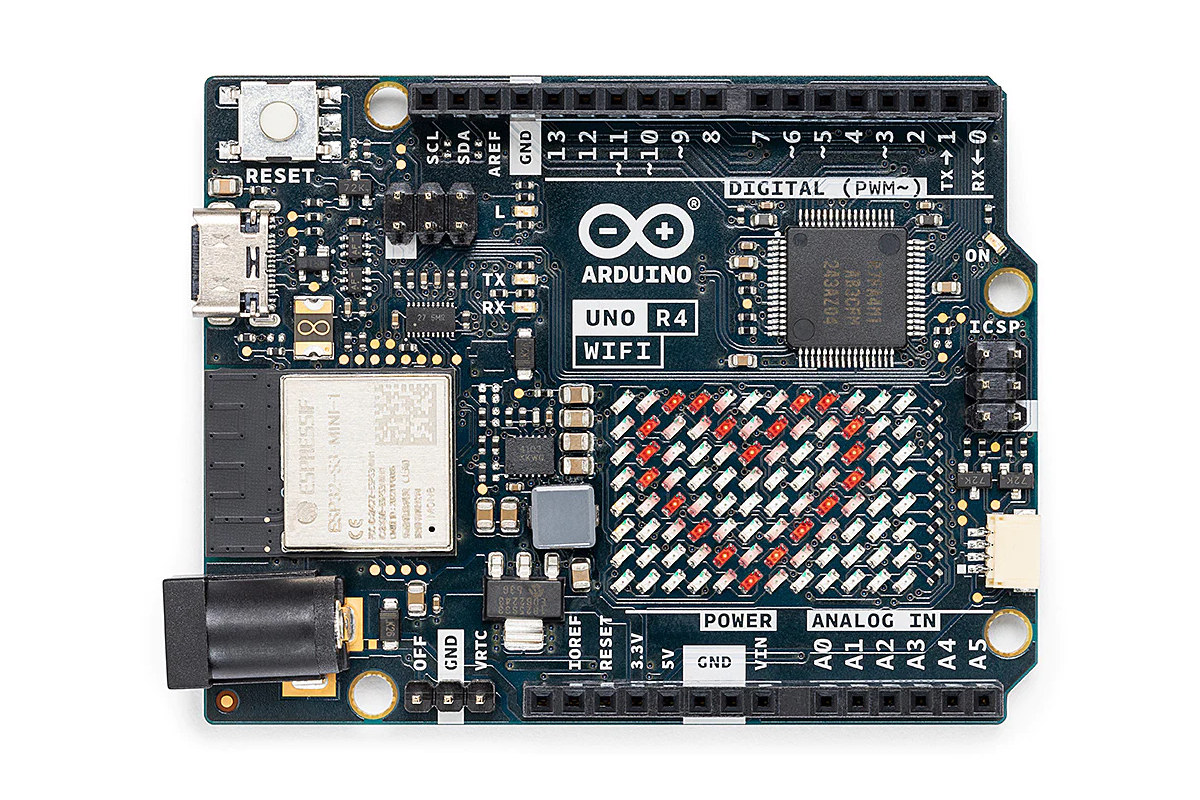

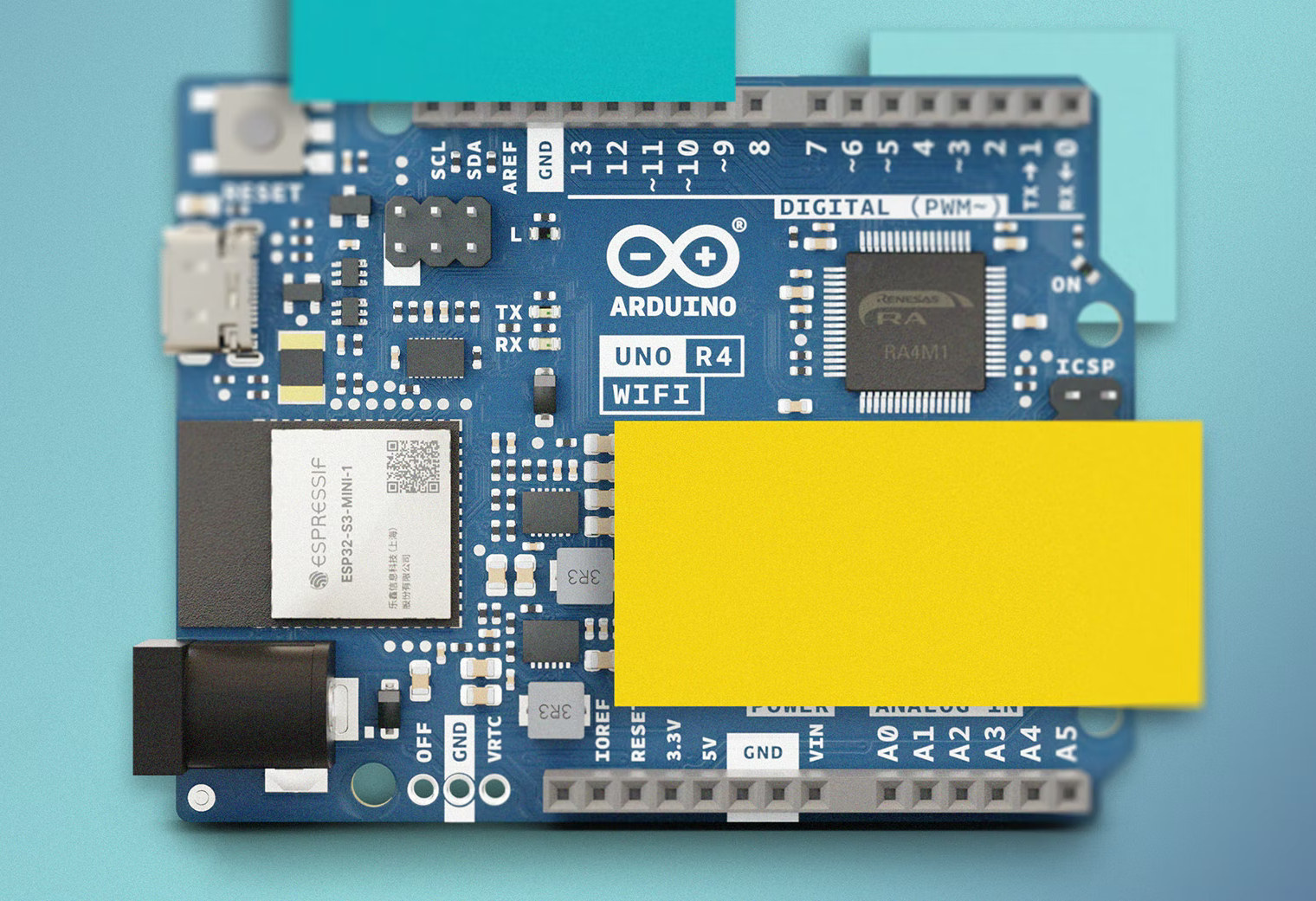

Arduino UNO R4 Minima and WiFi boards powered by a Renesas RA4M1 32-bit Arm Cortex-M4F microcontroller and equipped with an optional ESP32-S3 WiFI & BLE module are now available for respectively $20 (18 Euros) and $27.50 (25 Euros) on the Arduino store. The Arduino UNO R4 Renesas RA4M1 board was initially unveiled during Arduino Day with most details, but not everything as the company had hidden one part of the board which we now know is for a 12×8 LED matrix and a Qwiic connector for expansion present on the UNO R4 WiFi only. Arduino UNO R4 specifications: Microcontroller – Renesas RA4M1 Arm Cortex-M4F MCU @ 48 MHz with 32KB SRAM, 256KB flash Wireless (Arduino UNO R4 WiFi only) – ESP32-S3-MINI-1 module based on ESP32-S3 dual-core Xtensa LX7 microcontroller with 512KB SRAM, 384KB ROM, WiFi 4 and Bluetooth 5.0 connectivity, PCB antenna Display (UNO R4 WiFi only) – 12×8 LED […]

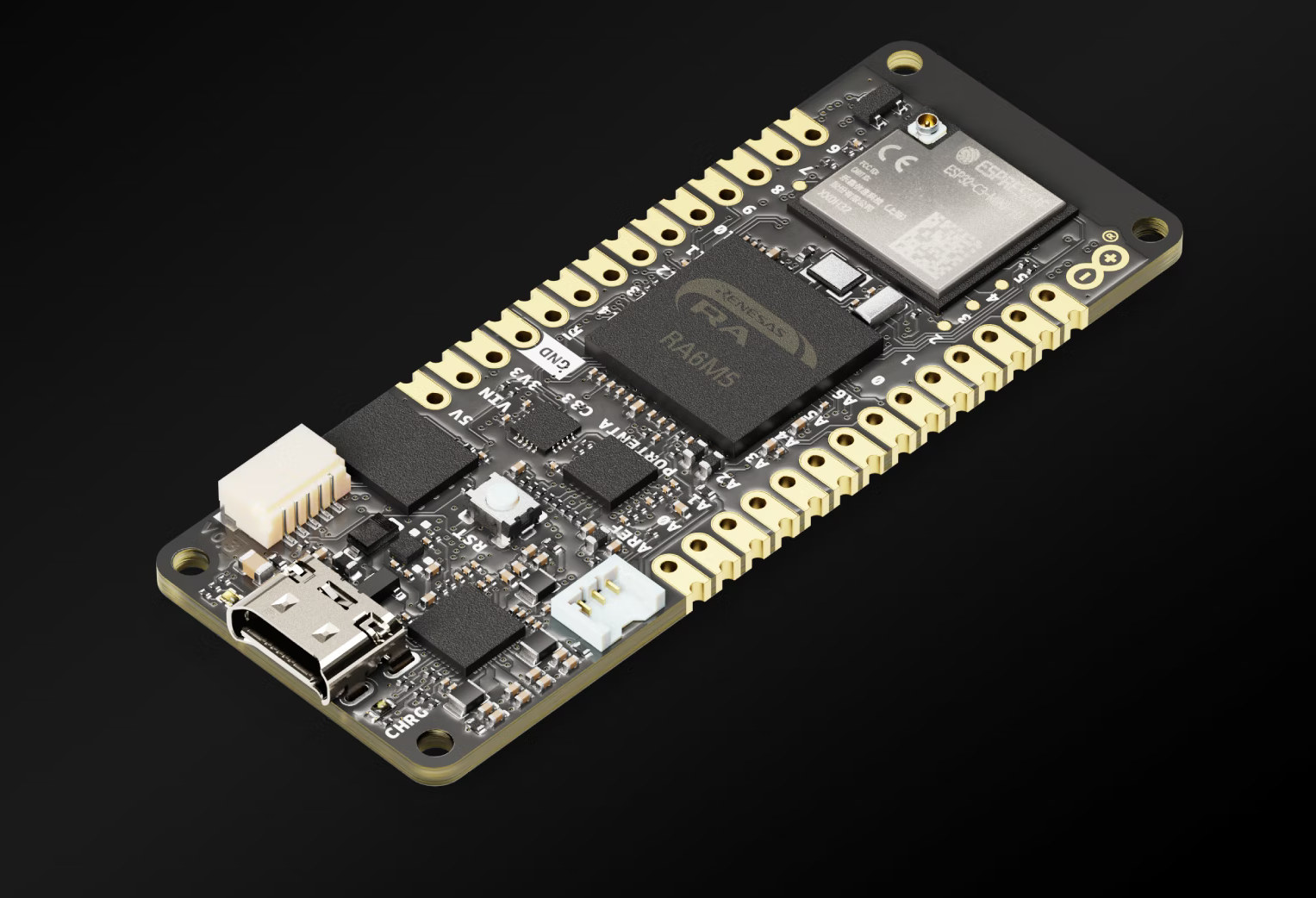

Portenta C33 is a $64 Arduino Pro board based on Renesas RA6M5 Arm Cortex-M33 MCU

Arduino Portenta C33 is the latest board from the Arduino Pro family which the company dubs a “high-performance, low-price” solution based on a 200 MHz Renesas RA6M5 Arm Cortex-M33 microcontroller and equipped with a ESP32-C3 Wi-Fi and Bluetooth Low Energy module. The new board provides a cost-effective alternative to the Portenta H7 and X8 boards, but still offers wireless connectivity, a secure element for industrial-grade security, and compatibility with Portenta, MKR, and Nicla components. Portenta C33 specifications: Microcontroller – Renesas R7FA6M5BH2CBG Arm Cortex-M33 microcontroller @ up to 200 MHz with 512KB SRAM, 2MB Flash, Arm TrustZone, and Secure Crypto Engine 9 Storage – 16 MB QSPI Flash Connectivity 10/100M Ethernet PHY ESP32-C3 WiFi and BLE module USB – 1x USB Type-C high-speed port with Power Delivery support I/Os via 2x 80-pin high-density connectors, Arduino MKR headers with castellated hole, and a 5-pin I2C connector Storage – SD Card Networking – […]

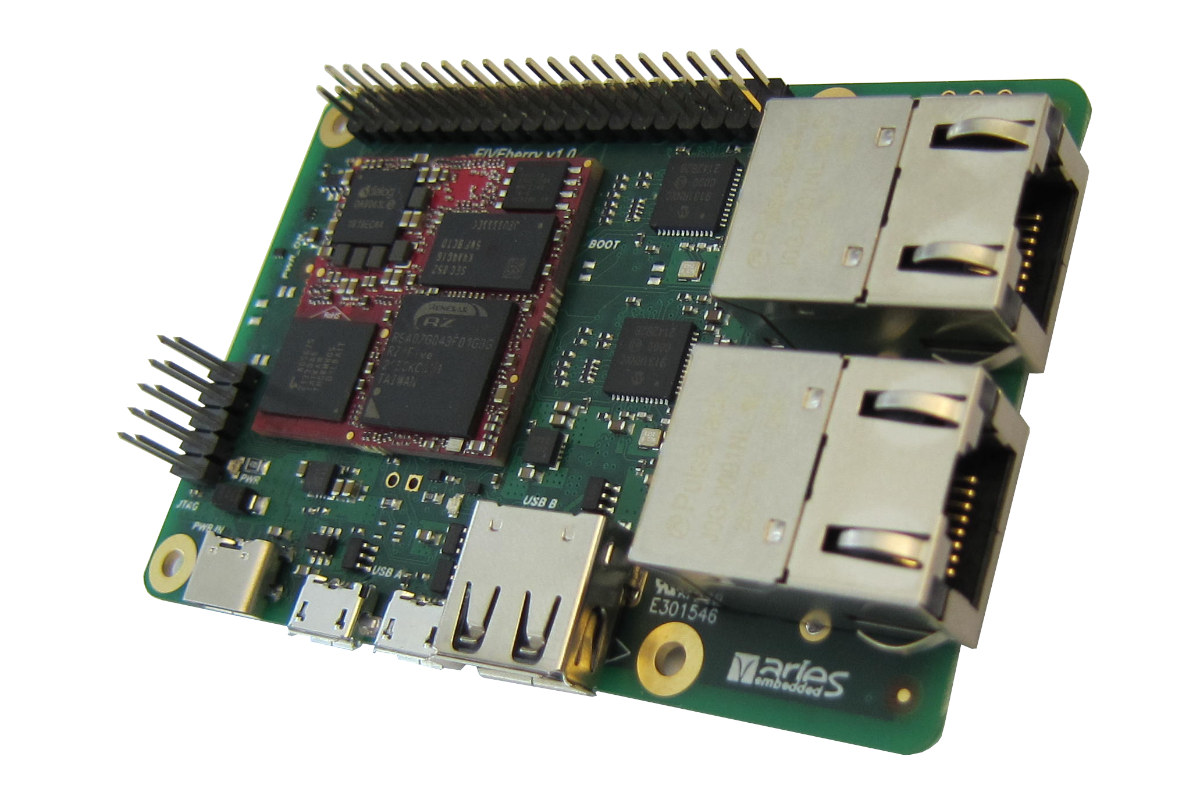

ARIES FIVEberry – A Community RISC-V SBC powered by Renesas RZ/Five processor

ARIES Embedded has unveiled the FIVEberry 64-bit RISC-V community board for fast prototyping fitted with an OSM-compatible MSRZFive system-in-package (SiP) powered by a 1GHz Renesas RZ/Five microprocessor. The board is equipped with a module with 512 DDR4, a 128MBit SPI NOR flash, a microSD card on the bottom of the board, two Gigabit Ethernet ports, two USB 2.0 ports, a micro USB port for serial console, and a JTAG header for further debugging, as well as a 40-pin GPIO header for expansion. FIVEberry specifications: SoM – ARIES Embedded MSRZFive-A0A system-on-module SoC – Renesas RZ/Five R9A07G043F01GBG single-core RISC-V AX45MP processor @ to 1.0 GHz System Memory – 512MB DDR4 RAM Storage – 128Mbit SPI NOR flash 332 contacts as per OSM Size-S specifications Storage – MicroSD card slot Networking – 2x Gigabit Ethernet ports USB – 1x USB 2.0 host port, 1x micro USB 2.0 OTG port Expansion – 40-pin GPIO […]

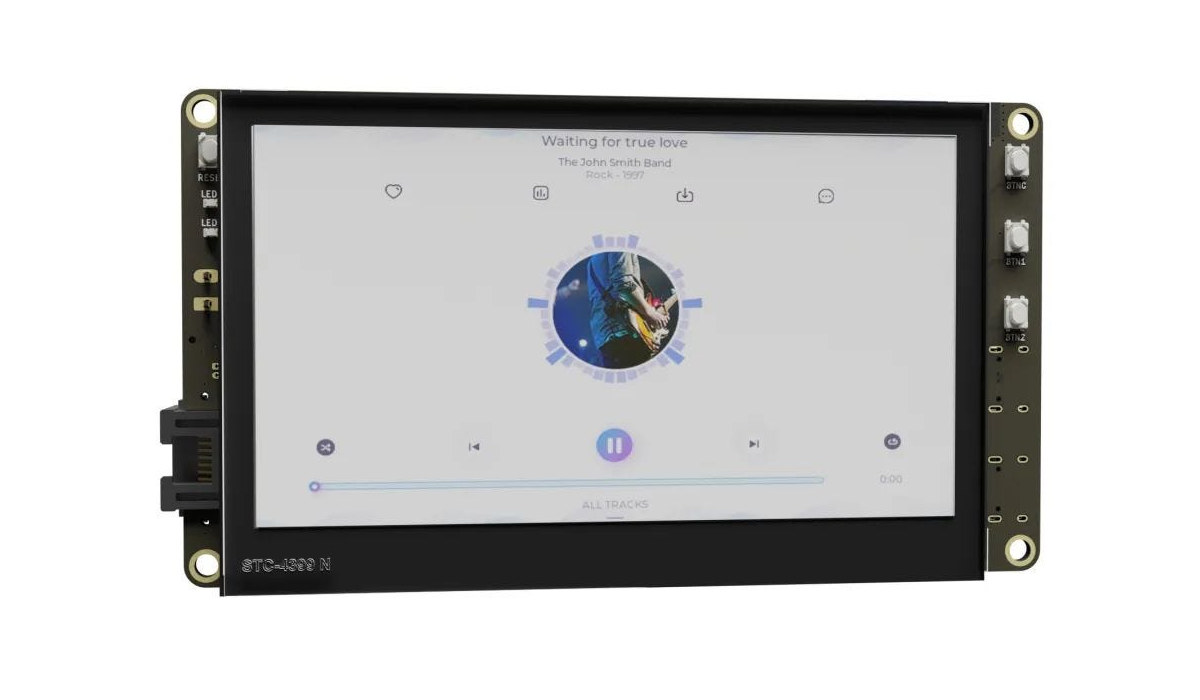

$25 Renesas “HMI Board” features RA6M3 microcontroller for RT-Thread & LVGL development

The Renesas HMI board is a Renesas RA6M3 Cortex-M4F development board with a 4.3-inch LCD developed in collaboration with the teams behind the RT-Thread RTOS project and LVGL open-source graphics library. Besides a color display for HMI (Human Machine Interface), the board also features a microSD card for data storage, Ethernet and WiFi connectivity, Arduino headers and PMOD connectors for expansion, a microphone and a speaker, a CAN bus terminal block, and two USB-C ports for debugging and power. Renesas HMI board specifications: MCU – Renesas RA6M3 (R7FA6M3AH3CFB) Arm Cortex-M4F microcontroller @ 120MHz with 2MB Flash, 640KB RAM, TFT controller, 2D accelerator, and JPEG decoder. Storage – MicroSD card slot Display – 4.3-inch LCD (RGB 888) Audio – Microphone and speaker Networking Low-profile 10/100M Ethernet RJ45 port RW007 SPI WiFi module by Shanghai Ruiside Electronic Technology USB – 2x USB Type-C ports Serial – 2-pin CAN bus terminal block Expansion […]

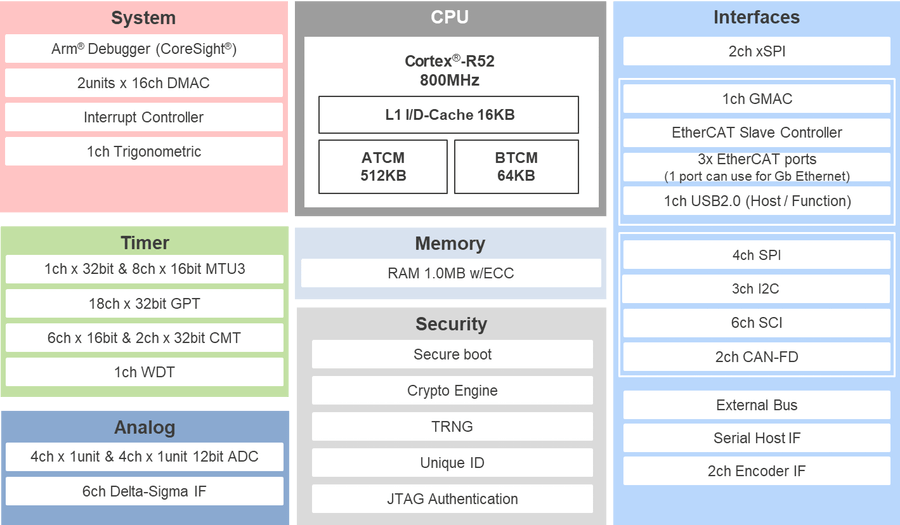

Renesas RZ/T2L Arm Cortex-R52 microprocessor embeds EtherCAT controller

Renesas RZ/T2L is a cost-optimized single-core Arm Cortex-R52 microprocessor (MPU) with an EtherCAT controller based on the same architecture as the higher-end Renesas RZ/T2M dual-core Cortex-R52 processor introduced last year, but at about half the size. The new MPU enables high-speed and accurate real-time processing performance required for AC servo drives, inverters, industrial robots, collaborative robots, etc.. used in factory automation (FA), medical equipment, building automation (BA), and other sectors and applications where EtherCAT is being adopted. Renesas RZ/T2L key features and specifications: CPU – Arm Cortex-R52 clocked at up to 800MHz with 16KB L1 I/D cache, 512KB ATCM, 64KB BTCM Memory – 1MB RAM with ECC Trigonometric function accelerator Ethernet EtherCAT slave controller: 3x ports 1x Ethernet MAC Motor control 2-channel encoder interface with support for A-format, EnDat2.2, BiSS-C, HIPERFACE DSL, FA-CODER Functional safety (FuSa) software up to SIL3 Motor current loop < 1µs 3-phase complementary PWM output for […]

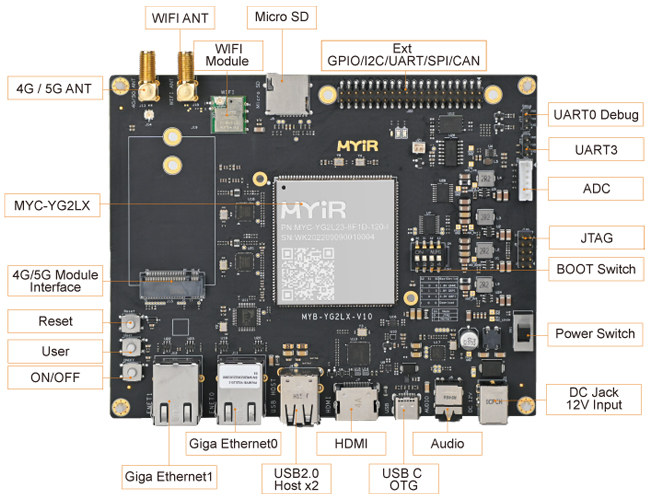

Renesas RZ/G2L CPU module targets HMI and IoT gateway applications

MYIR MYC-YG2LX is Renesas RZ/G2L CPU module with up to 4GB DDR4, 32GB eMMC flash, and various I/Os such as gigabit Ethernet, USB 2.0, camera and display interfaces accessible through 222 castellated holes, and designed for advanced HMI, IoT edge gateways, and other embedded devices with video capabilities. As a reminder, the Renesas RZ/G2L microprocessor comes with up to two Arm Cortex-A55 cores clocked at 1.2 GHz, one 200 MHz Cortex-M33 real-time core, a Mali-G31 GPU for 3D graphics interfaces, and a VPU capable of H.264 encoding/decoding. The company also offers the MYD-YG2LX development board based on the 45x43mm MYC-YG2LX CPU module with easy access to its interfaces. MYIR MYC-YG2LX Renesas RZ/G2L CPU module MYC-YG2LX module specifications: SoC – Renesas RZ/G2L (R9A07G044L23GBG) dual-core Cortex-A55 processor with Cortex-M33 core @ 200 Mhz, Arm Mali-G31 GPU, H.264 hardware video decoding/encoding System Memory – 1 or 2GB DDR4 (option for up to 4GB) […]

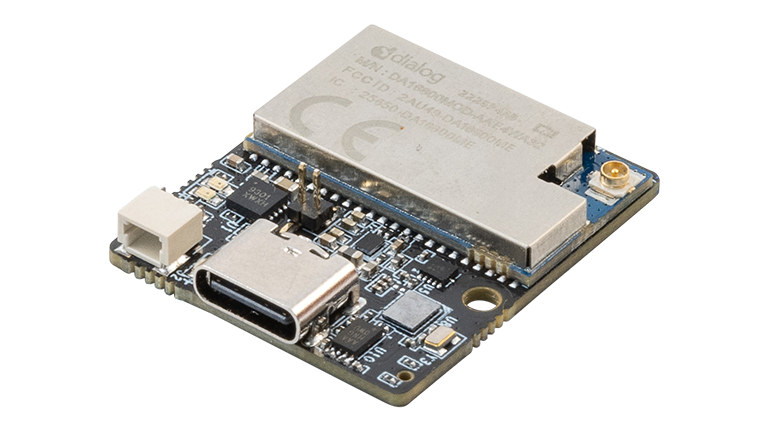

Tiny RASynBoard combines Renesas RA6M4 MCU with Syntiant NDP120 ML accelerator, WiFi & BLE module, and some sensors

Avnet RASynBoard is a tiny board that packs a lot of features in a 30x25mm form factor with a Renesas RA6M4 Cortex-M33 microcontroller, a Syntiant NDP120 Neural Decision Processor, a Renesas (Previously Dialog Semi) DA16600 Wi-Fi 4 & Bluetooth 5.1 combo module, and a 6-axis inertial measurement unit (IMU) and digital microphone from TDK. The RASynBoard is offered as part of an EVK with the Core Board described above plus an IO board with headers, a Pmod connector, a MikroE Shuttle Click header, a microSD card slot for storage, and a built-in debugger, plus two buttons and an RGB LED. RASynBoard specifications: Main microcontroller – Renesas RA6M4 Arm Cortex-M33 microcontroller @ 200 MHz with 1 MB flash memory, 256 KB SRAM ML accelerator – Syntiant NDP120 Neural Engine based on Syntiant Core 2 Deep Neural Network, Arm Cortex M0 and HiFi 3 DSP Wireless module – Renesas DA16600 2.4 […]

Arduino UNO R4 Renesas RA4M1 32-bit maker board offered with optional ESP32-S3 WiFI & BLE module

Arduino have launched an upgrade to their 8-bit Arduino UNO R3 board with the Arduino UNO R4 featuring a 48 MHz Renesas RA4M1 Arm Cortex-M4F 32-bit microcontroller, and an optional ESP32-S3 module for WiFi 4 and Bluetooth 5.0 connectivity. The new Arduino UNO R4 offered improved performance and greater resources since the MCU is clocked three times faster than the 8bit AVR MCU found in the UNO R3, the board gets sixteen times more RAM (32KB vs 2KB to 32kB) and eight times more flash memory (256KB vs 32kB). The USB Type-B device port has been upgraded to a more modern USB Type-C port and the UNO R4 can take up to 24V supply voltage. Arduino UNO R4 (preliminary) specifications: Microcontroller – Renesas RA4M1 Arm Cortex-M4F MCU @ 48 MHz with 32KB SRAM, 256KB flash. 8KB dataflash Wireless (Arduino UNO R4 WiFi only) – ESP32-S3-MINI-1 module based on ESP32-S3 dual-core […]