zigpy-zboss is a Python library that adds support for Nordic Semiconductor nRF52840 modules to zigpy open-source Python Zigbee stack project, as well as other Network Co-Processor radios that run firmware based on ZBOSS Open Initiative (ZOI). This enables integration with compatible Zigbee gateway implementations such as Home Assistant’s ZHA integration component and allows users to directly control Zigbee devices from a wide range of manufacturers such as IKEA, Philips Hue, SmartSung SmartThings, ITEAD SONOFF, Xiaomi Aqara, and others. Home Assistant’s ZHA integration already worked with Zigbee dongles based on Silicon Labs Mighty Gecko EFR32MG21 or Texas Instruments CC2652P microcontrollers, but now it’s possible to use nRF52840 dongles and development as Zigbee Coordinators thanks to the zigpy-zboss library. The zigpy-zboss ZBOSS radio library for zigpy source code and resources can be found on GitHub, but note that this is still an unofficial and experimental port, so testers need to manually […]

Linux 6.3 release – Notable changes, Arm, RISC-V and MIPS architectures

Linux Torvalds has just announced the release of Linux 6.3 on the Linux Kernel Mailing List (LKML): It’s been a calm release this time around, and the last week was really no different. So here we are, right on schedule, with the 6.3 release out and ready for your enjoyment. That doesn’t mean that something nasty couldn’t have been lurking all these weeks, of course, but let’s just take things at face value and hope it all means that everything is fine, and it really was a nice controlled release cycle. It happens. This also obviously means the merge window for 6.4 will open tomorrow. I already have two dozen pull requests waiting for me to start doing my pulls, and I appreciate it. I expect I’ll have even more when I wake up tomorrow. But in the meantime, let’s enjoy (and test) the 6.3 release. As always, the shortlog […]

Linux 5.15 LTS release – Main Changes, Arm, RISC-V and MIPS architectures

Linus Torvalds released Linux 5.15, an LTS version, this past Sunday: It’s been calm, and I have no excuse to add an extra rc, so here we are, with v5.15 pushed out, and the merge window starting tomorrow. Which is going to be a bit inconvenient for me, since I also have some conference travel coming up. But it’s only a couple of days and I’ll have my laptop with me. Sometimes the release timing works out, and sometimes it doesn’t.. Anyway, the last week of 5.15 was mainly networking and gpu fixes, with some random sprinkling of other things (a few btrfs reverts, some kvm updates, minor other fixes here and there – a few architecture fixes, couple of tracing, small driver fixes etc). Full shortlog appended. This release may have started out with some -Werror pain, but it calmed down fairly quickly and on the whole 5.15 was […]

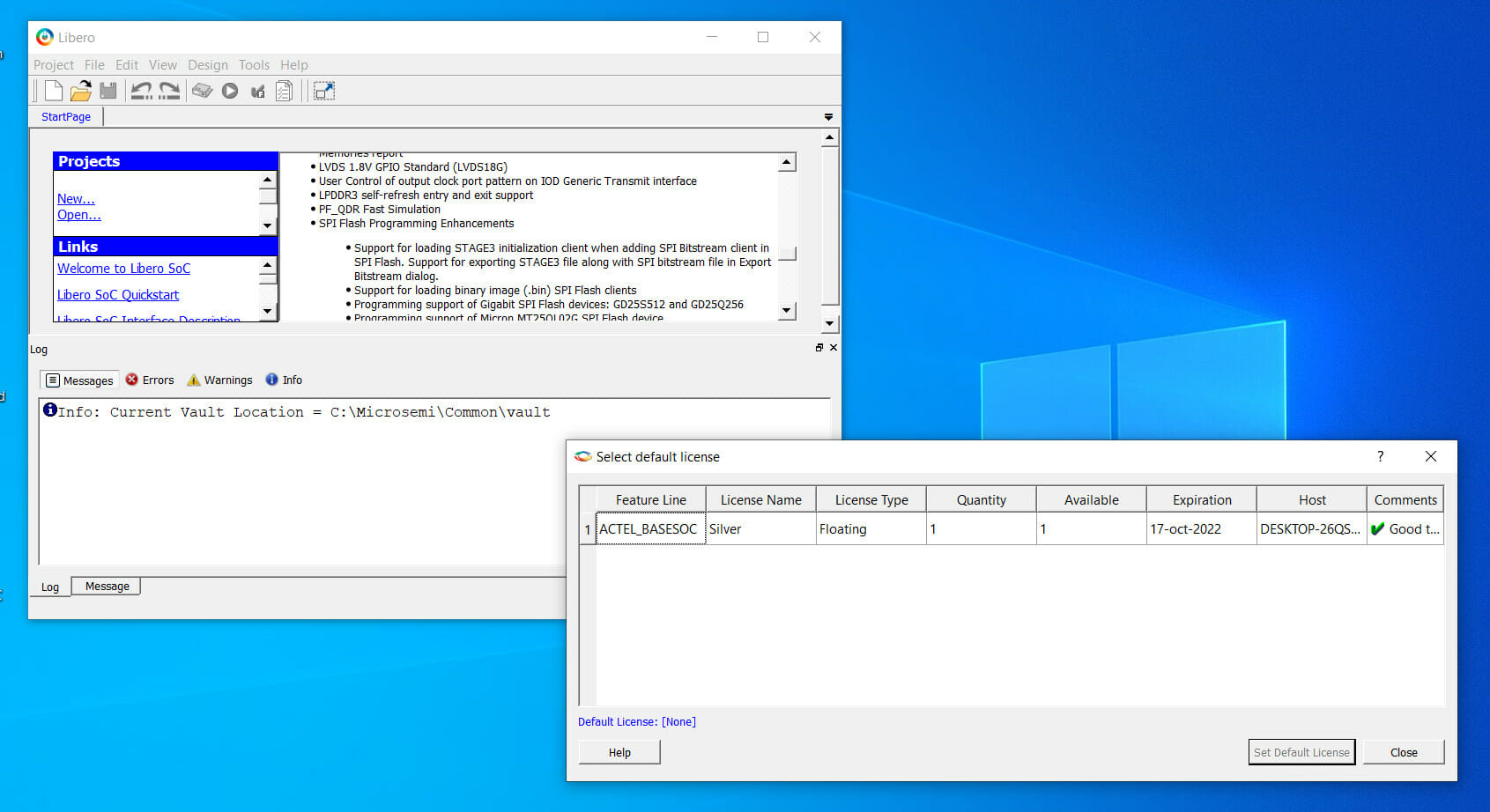

My experience installing Libero SoC in Ubuntu and Windows 10

A few weeks ago, I received Microchip PolarFire SoC FPGA Icicle Kit with FPGA fabric and hard RISC-V cores capable of handling Linux. I wrote “Getting Started with Yocto Linux BSP” tutorial for the board, and I had initially titled the current post “Getting Started with FPGA development using Libero SoC and Polarfire FPGA SoC”. I assumed I would write one or two paragraphs about the installation process, and then show how to work with Libero SoC Design Suite to create an FPGA bitstream. But instead, I spent countless hours trying to install the development tools. So I’ll report my experience to let readers avoid some of the pitfalls, and hopefully save time. (Failing to) Install Libero SoC v2021.v2 on Ubuntu 20.04 If we go to the download page, we’ll see Libero SoC v2021.2 for Windows and Libero SoC v2021.2 for Linux. Since my computer is running Ubuntu 20.04, I decided […]

OpenBSD 7.0 adds 64-bit RISC-V, improves Apple Arm silicon support

OpenBSD 7.0, the 51st release of the UNIX-like operating system, was outed on October 14, 2021, with the introduction of 64-bit RISC-V support for HiFive Unmatched and PolarFire SoC Icicle Kit boards, as well as further improvements to ARM64 targets, notably for Apple Silicon Macs, although it’s not quite ready for general use yet. You’ll find the complete list of new features and updates on the OpenBSD website, but here are some of the highlights: New platforms – OpenBSD 7.0 add 64-bit RISC-V support Extended platforms arm64 Improvements to Apple Silicon Macs support USB 3, NVMe storage, GPIO driver, power management, etc… Enabled LEDs for the LAN7800 chip as found on the Raspberry Pi 3 Model B+. Added Type-C PHY controller found on the Rockchip RK3399. Implemented multicast support to Marvell ARMADA chips Various other changes to mips64, amd64, armv7, powerpc64 Kernel improvements Enabled dynamic tracker (dt) for GENERIC kernels […]

Getting Started with the Yocto Linux BSP for Polarfire SoC FPGA Icicle Kit

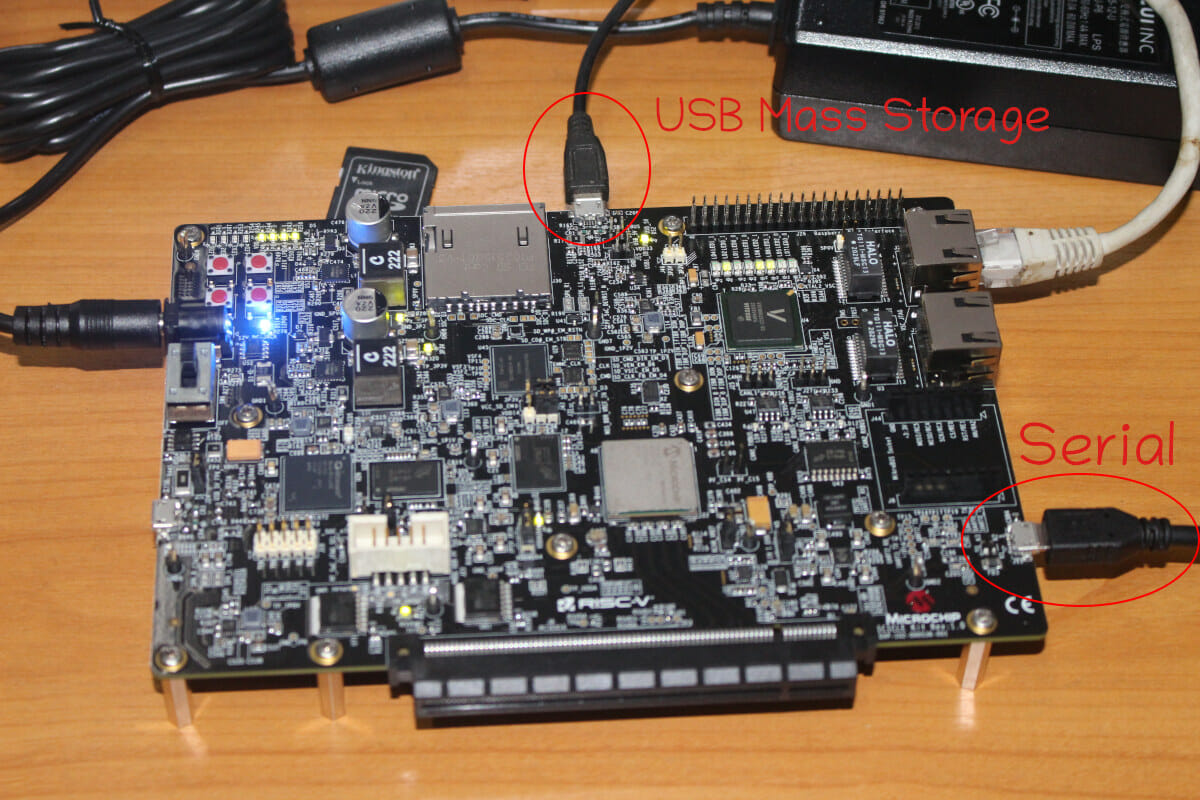

Last month I received Microchip PolarFire SoC FPGA Icicle development kit that features PolarFire SoC FPGA with a Penta–core 64-bit RISC-V CPU subsystem and an FPGA with 254K LE, and booted it into the pre-installed Linux operating systems based on OpenEmbedded. Today, I’ll show how to get started with the Yocto BSP and run the EEMBC CoreMark benchmark, and I’ll check out the FPGA with Libero SoC Design Suite in a couple of weeks. Operating Systems supported by PolarFire SoC FPGA My initial idea was to focus this part of the review on Linux on RISC-V status, checking some system information, running some benchmarks (e.g. SBC-Bench), compiling the Linux kernel, and installing services like a LEMP stack (Linux, Nginx (pronounced Engine-X), MySQL, PHP) which could be used for WordPress hosting for instance. But then I looked at the operating systems supported with Microchip PolarFire SoC FPGA. There’s a Yocto Linux […]

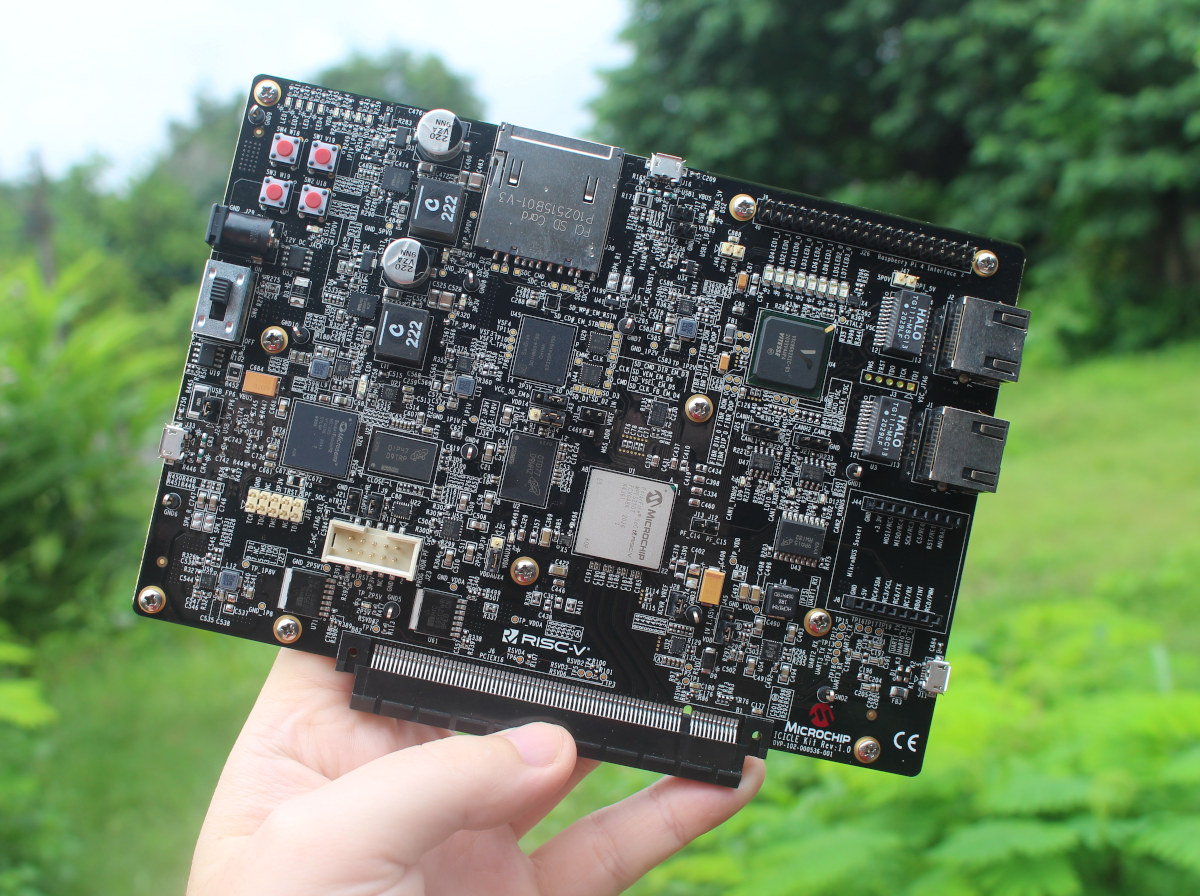

A first look at Microchip PolarFire SoC FPGA Icicle RISC-V development board

Formally launched on Crowd Supply a little over a year ago, Microchip PolarFire SoC FPGA Icicle (codenamed MPFS-ICICLE-KIT-ES) was one of the first Linux & FreeBSD capable RISC-V development boards. The system is equipped with PolarFire SoC FPGA comprised a RISC-V CPU subsystem with four 64-bit RISC-V (RV64GC) application cores, one 64-bit RISC-V real-time core (RV64IMAC), as well as FPGA fabric. Backers of the board have been able to play with it for several months ago, but Microchip is now sending the board to more people for evaluation/review, and I got one of my own to experiment with. That’s good to have a higher-end development board instead of the usual hobbyist-grade board. Today, I’ll just have a look at the kit content and main components on the board before playing with Linux and FPGA development tools in an upcoming or two posts. Microchip PolarFire SoC FPGA Icicle Unboxing The board […]

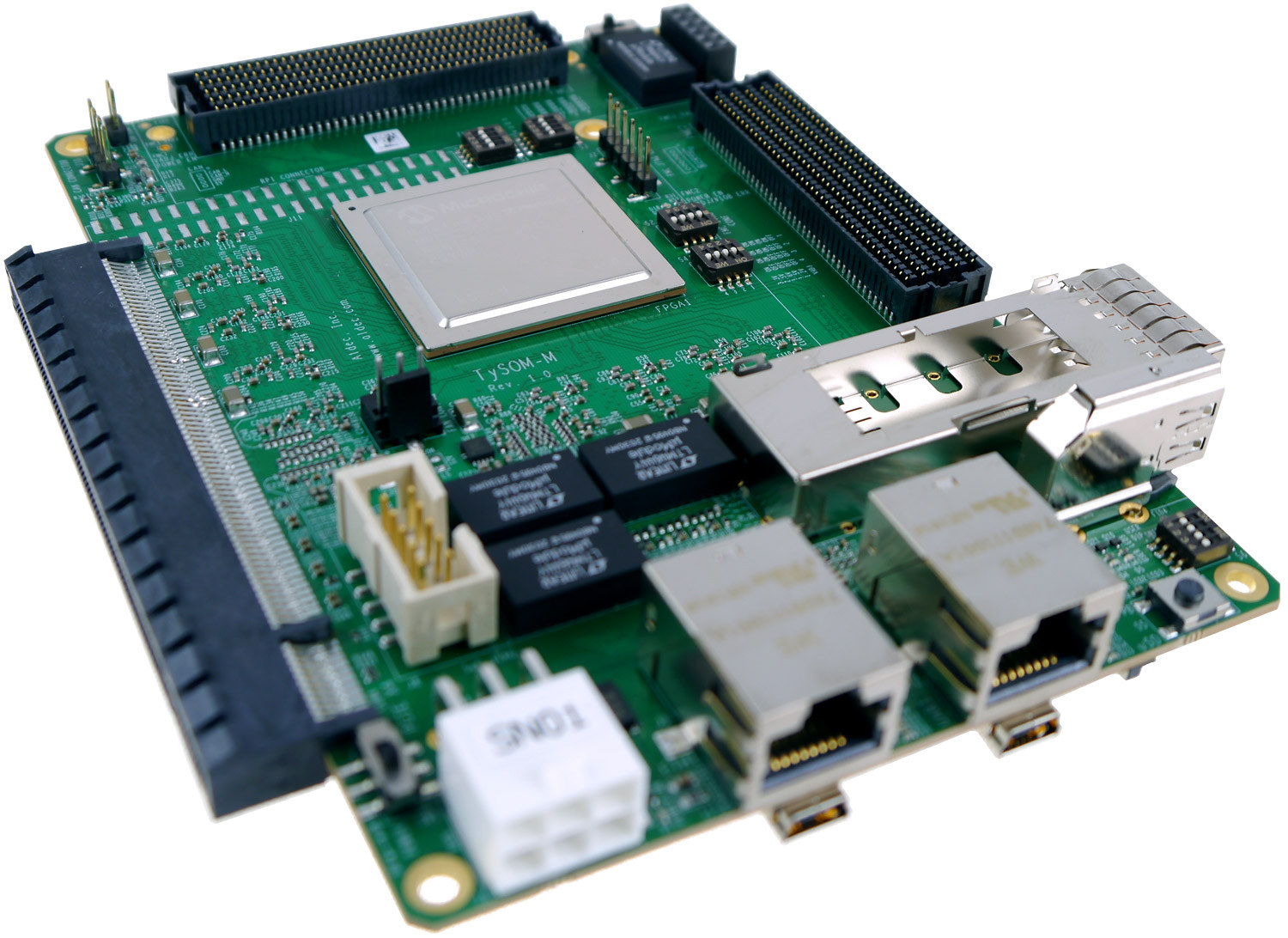

Embedded development board features Microchip PolarFire RISC-V FPGA SoC

Microchip/MicroSemi first introduced PolarFire RISC-V FPGA SoC at the end of 2018, with the chip being like the RISC-V equivalent of Xilinx Zynq Ultrascale+ Arm & FPGA MPSoC. The following year, ARIES Embedded unveiled the ARIES M100PF system-on-module and evaluation board, before Microchip launched PolarFire SoC Icicle 64-bit RISC-V and FPGA development board, followed by the more compact PolarBerry SBC in 2020. There’s now at least a fourth platform based on PolarFire SoC with Aldec TySOM-M-MPFS250 embedded development board. Aldec TySOM-M-MPFS250 specifications: SoC – Microchip PolarFire MPFS250T-FCG1152 SoC with 4x SiFive U54 RV64GC application cores (similar to Cortex-A35 performance), 1x SiFive E51 RV64IMAC monitor core, FPGA fabric with 254K logic cells, 17.6 Mb RAM System Memory 2GB (16Gbit) 32-bit DDR4 for the FPGA 2GB (16Gbit) 36-bit RAM with ECC for the RISC-V cores (aka MSS = Microprocessor Subsystem) Storage – MicroSD card socket, eMMC flash, SPI flash, 64 Kbit […]