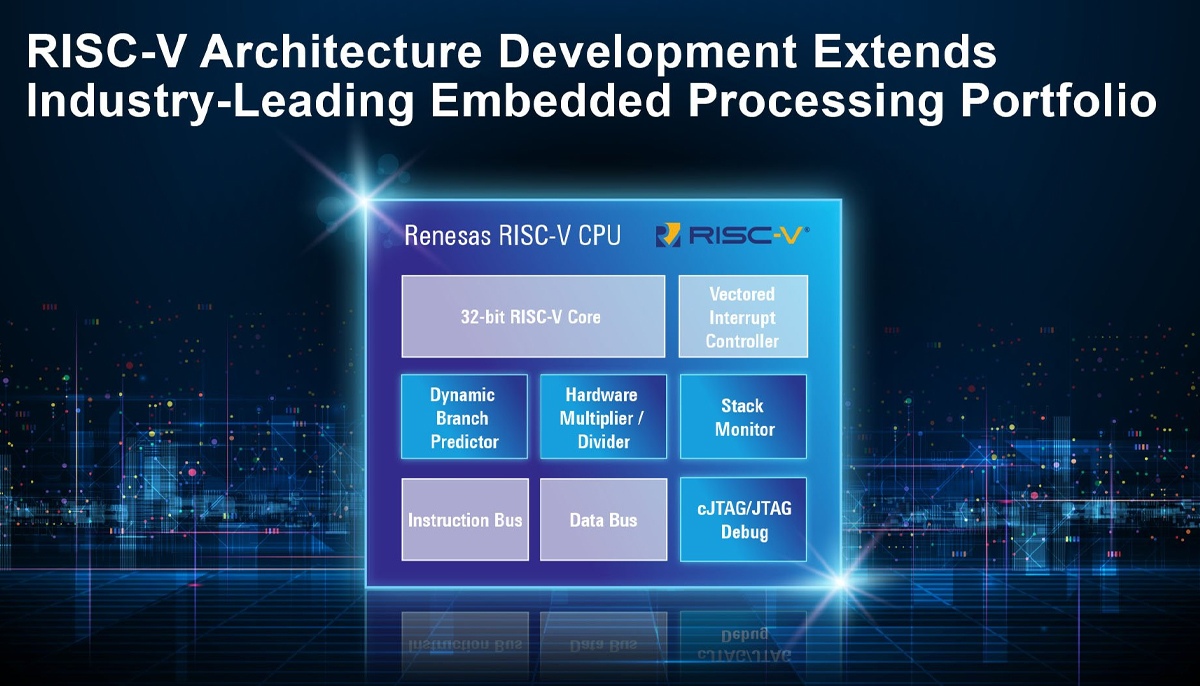

Renesas has recently announced its first homegrown 32-bit RISC-V CPU core based on the open-standard instruction set architecture (ISA). This CPU core is compatible with Renesas’ e2 studio IDE and supports other third-party IDEs for RISC-V MCUs. According to Renesas, the CPU achieved a remarkable 3.27 CoreMark/MHz performance outperforming similar RISC-V architectures in this category. RISC-V, an open ISA, is rapidly gaining popularity in the semiconductor industry. Many MCU providers have formed joint investment alliances to expedite their RISC-V product development. Previously, Renesas released two CPUs developed by Andes Technology Corp: the R9A02G020, an ASSP EASY MCU for Motor Control, and the R9A06G150, an ASSP EASY MCU for Voice HMI, both based on RISC-V. Additionally, they have introduced the RZ/Five, a Linux-capable 64-bit RISC-V microprocessor family, and RH850/U2B, an automotive System on Chip (SoC). However, with the release of their new CPU, Renesas independently enters the RISC-V market, highlighting their […]

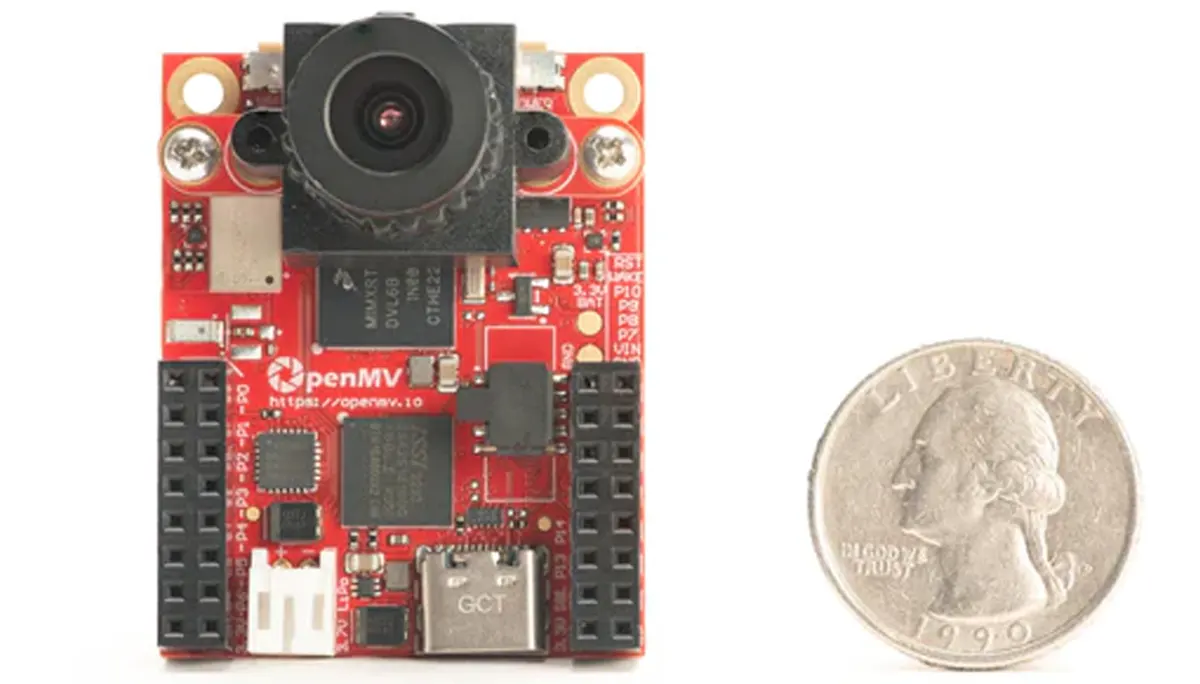

OpenMV CAM RT1062 camera for machine vision is programmable with MicroPython

Following the success of the OpenMV Cam H7 and the original OpenMV VGA Camera, OpenMV recently launched the OpenMV CAM RT1062 powered by NXP’s RT1060 processor. This new camera module integrates a range of features, including a high-speed USB-C (480Mbps) interface, an accelerometer, and a LiPo connector for portability. Similar to its predecessor, this camera module also features a removable camera system, and it is built around the OV5640 image sensor which is more powerful in terms of resolution and versatility. However, the previous Omnivision OV7725 sensor, used in the OpenMV Cam H7 has a far superior frame rate and low-light performance. OpenMV provides a Generic Python Interface Library for USB and WiFi Comms and an Arduino Interface Library for I2C, SPI, CAN, and UART Comms which can be used to interface your OpenMV Cam to other systems. To program the board, you can use MicroPython 3 with OpenMV IDE, […]