As a StarFive Technology in-house developed RISC-V 64-bit ultra-high-performance core, Dubhe showcases the best performance RISC-V CPU core IP yet. It utilizes the latest RISC-V instruction set which includes RV64GC, bit operation extension (B), vector extension (V) V1.0, and hypervisor extension H (Hypervisor), making it ideal for high-performance computing.

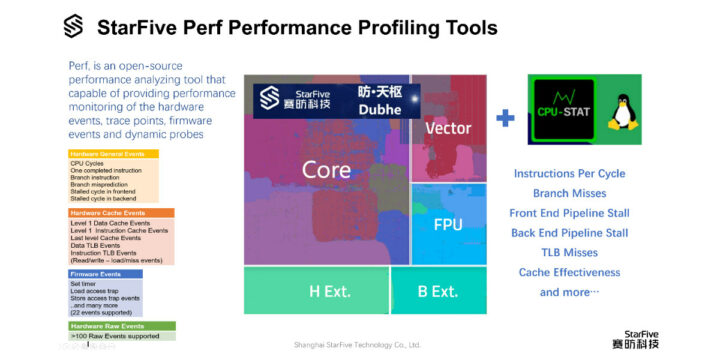

To pair with the Dubhe performance core, StarFive is now releasing “StarFive Perf Performance Profiling Tool”.

StarFive has made Perf compatible with the hardware performance monitor (HPM) and micro-architecture events at the hardware level. Perf provides a reliable performance verification platform that not only facilitates customers to further discuss the Dubhe technical specifications but also accelerates the implementation of high-performance applications with RISC-V processors.

Perf is an open-source and Linux-based performance analyzing tool capable of providing performance monitoring of the hardware events, tracepoints, firmware events, and dynamic probes. With the Perf profiling tool, we can monitor the performance of the predefined hardware events, predefined hardware cache events, and hardware raw events with programmable hardware performance monitor counters. It provides per task, per core, and per-workload counters sampling on these hardware events. A good example of usage is

|

1 |

perf stat -e cycles -e instructions -e branches -e branch-misses -e stallled-cycles-backend dhrystone 10000000 |

For more information about “StarFive Perf Performance Profiling Tool”, please visit https://github.com/starfive-tech/meta-starfive, or contact [email protected].

This account is for paid-for, sponsored posts. We do not collect any commission on sales, and content is usually provided by the advertisers themselves, although we sometimes write it for our clients.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress