Allwinner D1s (aka F133) is a cost-down version of Allwinner D1 RISC-V processor introduced earlier this year together with a Linux capable development board, with the main difference being the integrated 64MB DDR2.

Besides the built-in RAM, Allwinner D1s comes with many of the same features as D1 RISC-V SoC, but loses HDMI output and the HiFi 4 audio DSP, and Allwinner made some tweaks to the IOs with one less I2S audio interface, and general-purpose ADC.

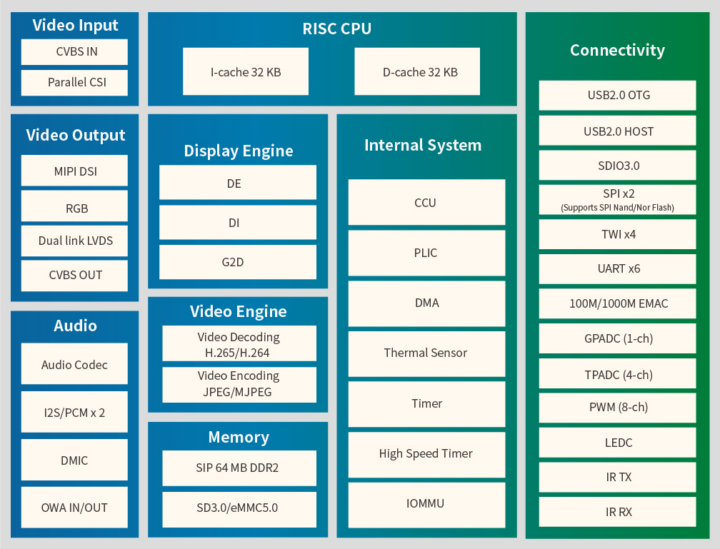

Allwinner D1s/F133 specifications:

- CPU – RISC core with 32 KB I-cache + 32 KB D-cache (CNXSoft: not specified, but probably the same Alibaba/T-Head Xuantie C906 RISC-V core as used in Allwinner D1)

DSP – HiFi4 DSP 600MHz with 32 KB I-cache + 32 KB D-cache, 64 KB I-ram + 64 KB D-ram- Memory – 64 MB DDR2 (SIP)

- Storage I/F – SD3.0, eMMC 5.0, SPI Nor/Nand Flash

- Video Engine

- Video decoding

- H.265 up to 1080p @ 60fps

, or 4K @ 30fps - H.264 up to 1080p @ 60fps

, or 4K @ 24fps - MPEG-1/2/4, JPEG, VC1 up to 1080p @ 60fps

- H.265 up to 1080p @ 60fps

- Video encoding – JPEG/MJPEG up to 1080p @ 60fps

- Supports input picture scaler up/down

- Video decoding

- Video OUT

- RGB LCD output interface up to 1920 x 1080 @ 60fps

- Dual-link LVDS interface up to 1920 x 1080 @ 60fps

- 4-lane MIPI DSI interface up to 1920 x 1080 @ 60fps (Note: shown in block diagram, but not in the specs)

HDMI V1.4 output interface up to 4K@30fps- CVBS OUT interface, supporting NTSC and PAL format

- Video IN

- 8-bit parallel CSI interface

- CVBS IN interface, supporting NTSC and PAL format (only for F133-B processor)

- Display Engine – Allwinner SmartColor 2.0 post-processing engine, de-interlace support, G2D hardware accelerator

- Audio

- 2x DAC’s and 3x ADC’s

- Analog audio interfaces – MICIN3P/N, LINEINL/R, FMINL/R, HPOUTL/R

- Digital audio interfaces – I2S/PCM, DMIC, OWA IN/OUT

- Networking – 10/100/1000M EMAC with RMII and RGMII interfaces

- USB – USB2.0 OTG, USB2.0 Host

- Other peripherals

- SDIO 3.0, SPI x 2, UART x 6, TWI x 4

- PWM (8-ch), GPADC (1-ch),

LRADC (1-ch), TPADC (4-ch), IR TX & RX

- Security Subsystem

- AES, DES, 3DES encryption and decryption algorithms

- RSA signature verification algorithm

- MD5/SHA and HMAC tamper-proofing

- Hardware random number generator

- Integrated 2 Kbits OTP storage space

- Package – eQFPA 128 14×14 mm

- Manufacturing process – 22nm

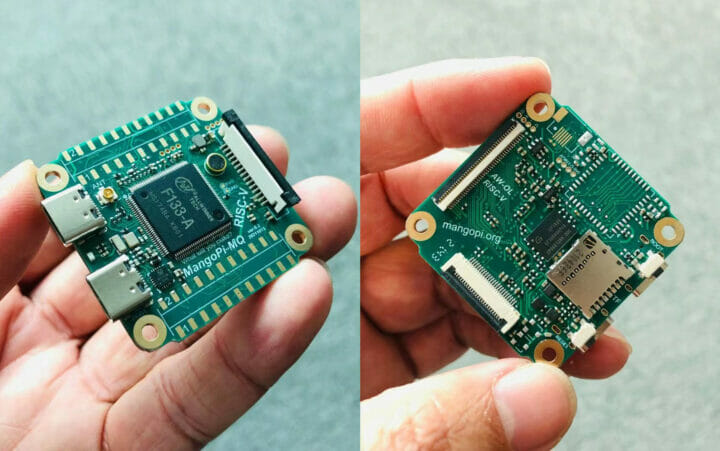

The processor page on Allwinner’s website does not mention RISC-V at all, only RISC, but I found about the processor via the MangoPi team who teased us with the upcoming MangoPi-MQ1 SBC based on Allwinner F133-A processor, so I can confirm it’s indeed a RISC-V processor.

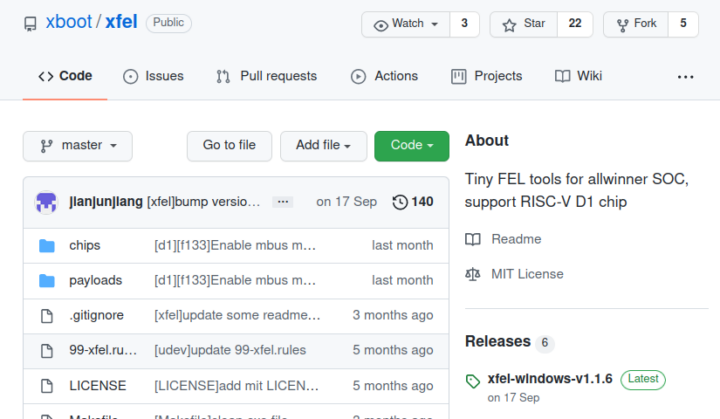

For further confirmation, the xfel FEL tool for Allwinner D1 on Github also supports F133. Supported operating systems include Melis RTOS based on RT-Thread, and Tina Linux (OpenWrt).

Allwinner D1s looks to be designed for cameras and smart displays and offers peripherals, embedded RAM just like Allwinner V3s or SigmaStar SSD210 Arm-based processors. Boards based on Allwinner D1s/F133 should be very cost-effective with Linux-capable RISC-V SBCs likely to sell for $10+ and up. We’ll know soon, as MangoPi-MQ1 mass production is scheduled for November, and the board should start selling on Taobao and Seeed Studio soon after.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress