Formally launched on Crowd Supply a little over a year ago, Microchip PolarFire SoC FPGA Icicle (codenamed MPFS-ICICLE-KIT-ES) was one of the first Linux & FreeBSD capable RISC-V development boards. The system is equipped with PolarFire SoC FPGA comprised a RISC-V CPU subsystem with four 64-bit RISC-V (RV64GC) application cores, one 64-bit RISC-V real-time core (RV64IMAC), as well as FPGA fabric.

Backers of the board have been able to play with it for several months ago, but Microchip is now sending the board to more people for evaluation/review, and I got one of my own to experiment with. That’s good to have a higher-end development board instead of the usual hobbyist-grade board. Today, I’ll just have a look at the kit content and main components on the board before playing with Linux and FPGA development tools in an upcoming or two posts.

Microchip PolarFire SoC FPGA Icicle Unboxing

The board comes with a 60W (12V/5A) power adapter, power cord, as well as an Ethernet cable, and a micro USB to USB cable for the serial console.

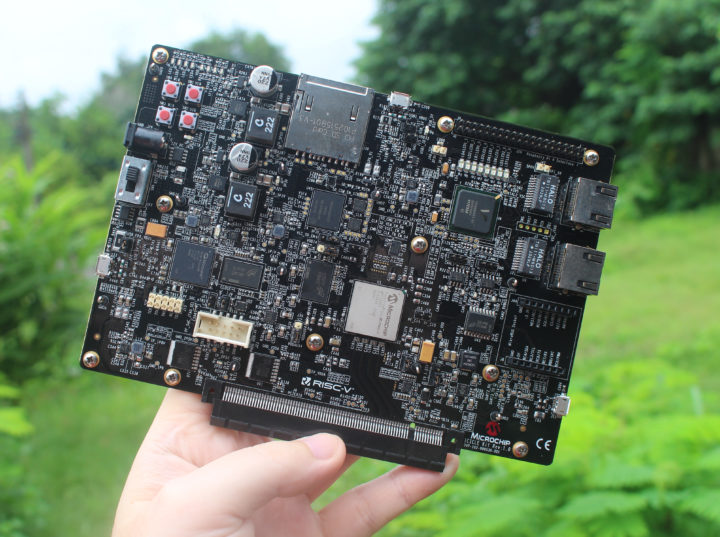

The main interfaces are the two Gigabit Ethernet RJ45 ports, three Micro USB ports including one for the serial console, one for embedded programming, and the last as a standard USB OTG port. SD card socket, Raspberry Pi & Mikrobus headers, as well as a PCIe x4 Gen2 connector. That means it’s a headless system. An earlier version had an HDMI 2.0 port, but it was removed from the final version.

The Microchip PolarFire SoC MPFS250T-FCVG484EES SoC FPGA is the silver IC in the middle of the board, and we’ll also find an 8GB eMMC flash (Sandisk SDINBDG4-8G), 2GB RAM from Micron, an SPI flash, a Microsemi Smarfusion2 SoC FPGA with a Cortex-M3 core that appears to be used for embedded programming, as well as a Vitesse VSC8662XIC-03 “dual-port Gigabit Ethernet and 100BASE-FX/1000BASE-X SerDes with Recovered Clock Outputs”. I had never heard about Vitesse Semiconductor, but the company was acquired by Microsemi in 2015, which in turn became part of the Microchip Technology family in 2018.

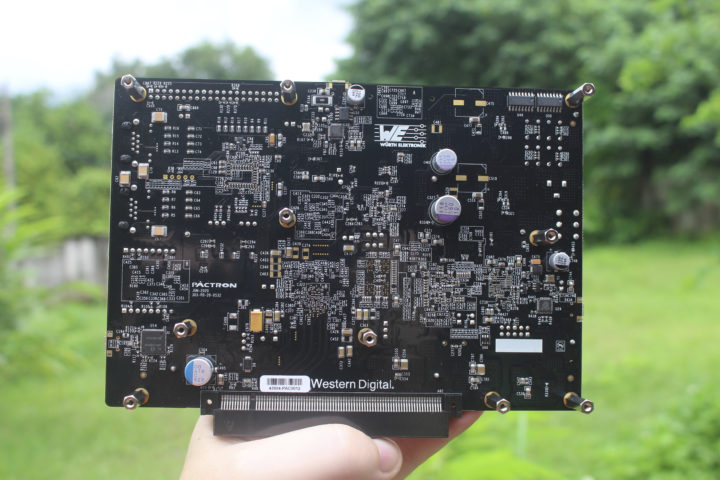

The bottom of the board comes with some large capacitors, a Silicon Labs CP2108 chip providing four UART interfaces, and two other USB chips for the remaining micro USB ports.

Getting started

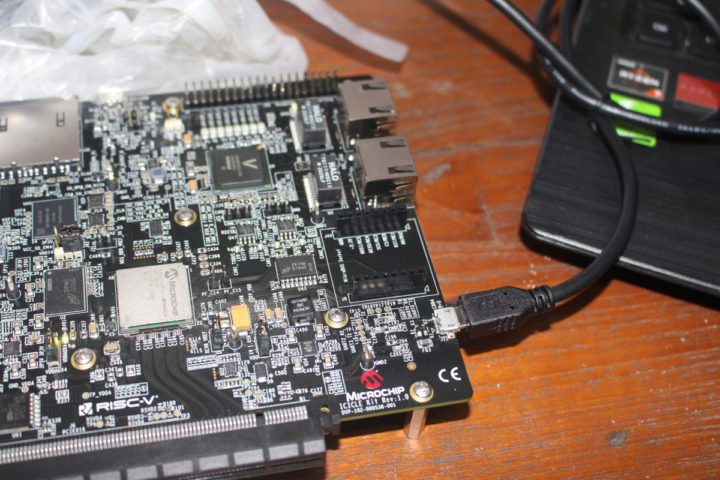

I don’t have access to Ethernet right now, so what I can do is limited, but I can still boot the board, as we just need to connect the micro USB to USB cable to access the board.

Bootterm reports four new serial interfaces.

|

1 2 3 4 5 6 7 |

bt -l port | age (sec) | device | driver | description ------+------------+------------+------------------+---------------------- 0 | 50 | ttyUSB0 | cp210x | CP2108 Interface 0 1 | 50 | ttyUSB1 | cp210x | CP2108 Interface 1 2 | 50 | ttyUSB2 | cp210x | CP2108 Interface 2 * 3 | 50 | ttyUSB3 | cp210x | CP2108 Interface 3 |

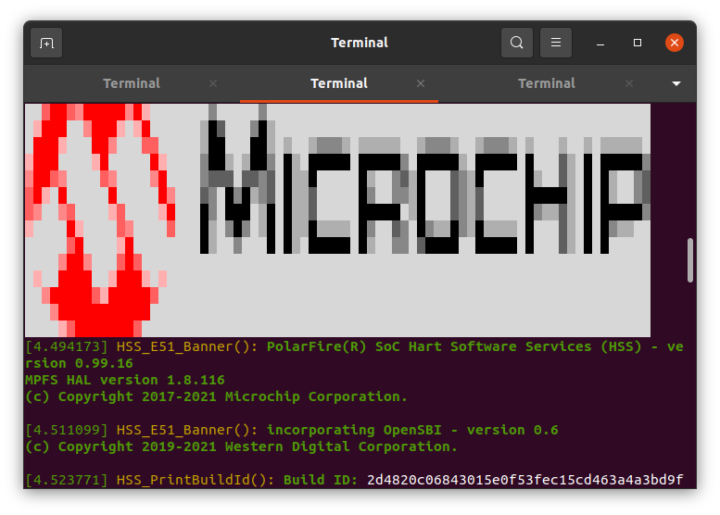

The documentation explains that the first two ports are used for “Hart Software Services (HSS) boot messages” (ttyUSB0) and U-Boot and Linux boot messages with a terminal prompt (ttyUSB1).

The output from COM0 is pretty with a Microchip logo followed by messages from HSS which handles boot and system monitoring functions.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 |

[ OK ] Reached target Multi-User System. Starting Update UTMP about System Runlevel Changes... [ OK ] Started Update UTMP about System Runlevel Changes. OpenEmbedded nodistro.0 icicle-kit-es ttyS0 icicle-kit-es login: root root@icicle-kit-es:~# cat /etc/issue OpenEmbedded nodistro.0 \n \l root@icicle-kit-es:~# cat /proc/cpuinfo processor : 0 hart : 1 isa : rv64imafdc mmu : sv39 uarch : sifive,rocket0 processor : 1 hart : 2 isa : rv64imafdc mmu : sv39 uarch : sifive,rocket0 processor : 2 hart : 3 isa : rv64imafdc mmu : sv39 uarch : sifive,rocket0 processor : 3 hart : 4 isa : rv64imafdc mmu : sv39 uarch : sifive,rocket0 root@icicle-kit-es:~# |

It’s a Yocto built Openembedded Linux image. We’ll only see the four RISC-V application cores here, as the real-time core runs FreeRTOS, Zephyr, or another RTOS. You can find the full U-boot & Linux boot log on pastebin.

Going further I plan to do some more testing on the RISC-V cores using the preinstalled Linux image, and try out the FPGA development tools notably Libero IDE software with comes with a free Libero Silver License. Let me know if you’d like me to check anything in particular.

If you are interested in the board, it’s available from various distributors for under $500, but right now only Mouser seems to have proper stock.

Continue reading:

- Getting Started with the Yocto Linux BSP for Polarfire SoC FPGA Icicle Kit

- My experience installing Libero SoC in Ubuntu and Windows 10

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress