SiFive has announced two RISC-V “Performance” cores with Performance P550 that should be the fastest 64-bit RISC-V processor so far with a SPECInt 2006 score of 8.65/GHz, as well as a Performance P270 Linux capable processor with full support for the RISC-V vector extension v1.0 rc.

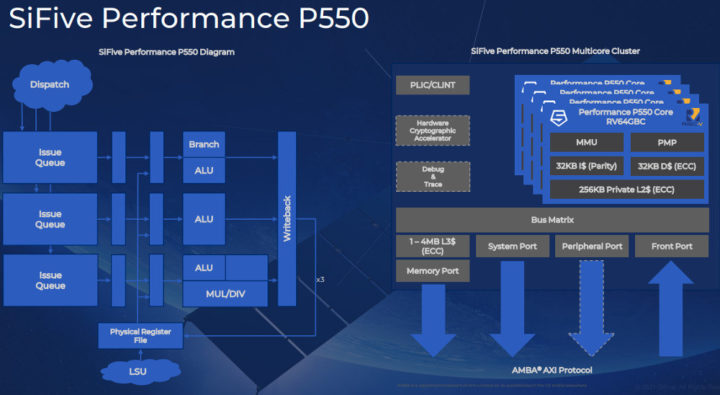

SiFive Performance P550

P550 highlights:

- RISC-V RV64GBC ISA

- 13 stage, 3-issue high-performance out-of-order pipeline

- Supports multicore coherence with up to 4 cores in a core complex

- Private 32KB+32KB L1 cache and a private 256KB L2 cache per core

- Up to 4MB L3 cache in a four-core cluster

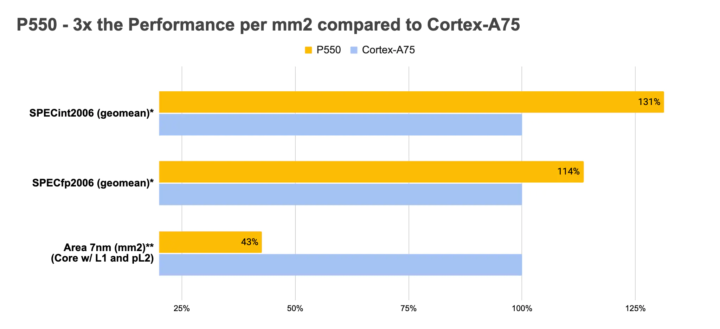

- SPECint 2006 – 8.65/GHz

- 2.4 GHz in 7nm with a footprint of less than 0.25 mm

There have been some rumors about Intel’s plan to acquire SiFive in recent days, and while the acquisition news still has to be confirmed, Intel says it will be using the P550 Performance core in an upcoming 7nm Intel Horse Creek platform. Amber Huffman, Intel Fellow and CTO of IP engineering group at Intel, says:

We are pleased to be a lead development partner with SiFive to showcase to mutual customers the impressive performance of their P550 on our 7nm Horse Creek platform . By combining Intel’s leading-edge interface IP such as DDR and PCIe with SiFive’s highest performance processor, Horse Creek will provide a valuable and expandable development vehicle for cutting-edge RISC-V applications.

It’s unclear whether Horse Creek will mix x86 cores with the RISC-V core in a hybrid processor like the Lakefield platform, or as a pure RISC-V processor. Anandtech has more speculations about the “development platform”.

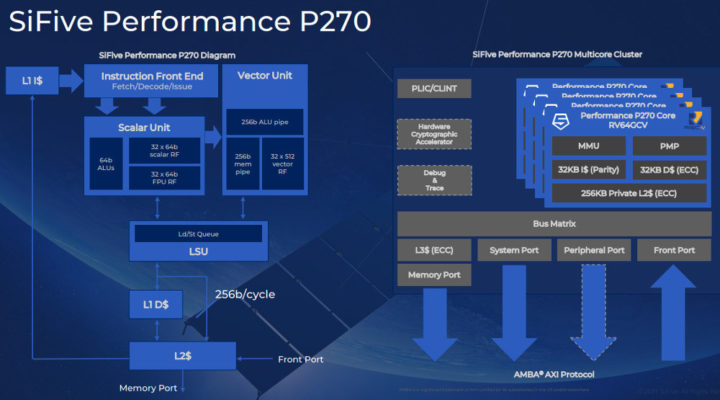

SiFive Performance P270

- RISC-V RV64GCBV ISA

- 8-Stage, dual-issue, in-order processor

- 256-bit Vector Unit enabling compute capabilities with full support for the RISC-V Vector Extension v 1.0RC

- Supports multicore coherence with up to 4 cores in a core complex

- Private 32KB+32KB L1 cache and a private 256KB L2 cache per core

- SPECint 2006 – 4.6/GHz

Just like the previously announced SiFive Intelligence X280, the Performance P270 core supports the translation of legacy SIMD/NEON code to SiFive vector assembly using the SiFive Recode utility.

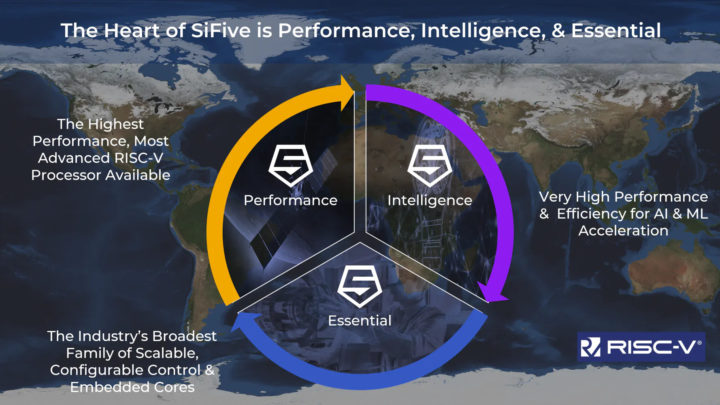

SiFive Performance, Intelligence, and Essential families

Patrick Little joined SiFive as President & CEO last year, and one of the things he did was to split SiFive’s products into three families:

- Essential – Legacy SiFive embedded RISC-V core likes U-Series, S-Series, E-Series

- Intelligence – RISC-V cores optimized for low-power AI & ML acceleration

- Performance – Highest performance RISC-V cores designed for networking,

edge compute, autonomous machines, 5G base stations, virtual/augmented reality

The product page about the new SiFive Performance cores only has limited information at this point in time, and the company will host a webinar on July 14 to provide more details.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress