Calista Redmond, CEO of RISC-V International, detailed the growth in memberships:

This year, our technical community has grown 66 percent to more than 2,300 individuals in our more than 50 technical and special interest groups. We’re seeing increased market momentum of RISC-V cores, SoCs, developer boards, software and tools across computing from embedded to enterprise

…

We’re proud of our growing global membership, which has more than doubled in the last year to 1,000 total members, including 222 organizations.”

RISC-V also launched the RISC-V Exchange now listing over 124 RISC-V cores, SoCs, and developer boards, as well as 129 RISC-V software applications and tools.

RISC-V Cores launched in 2020

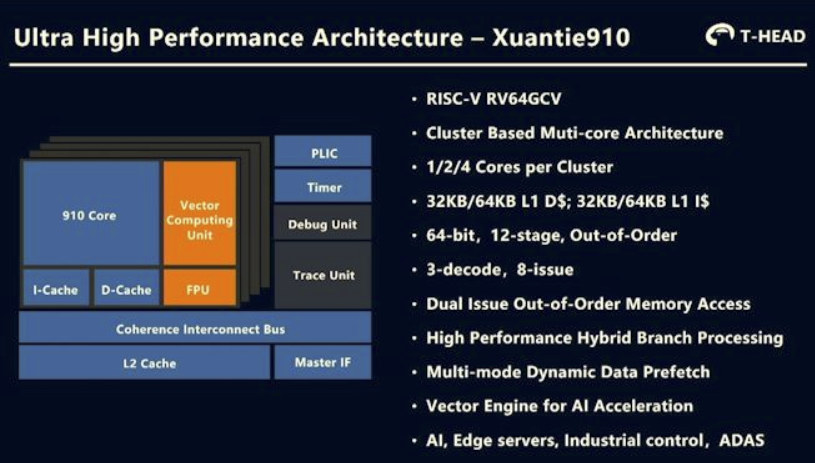

There are too many RISC-V cores to list them all here, but some of the most notable announcements included Alibaba XT910 64-bit RISC-V core, Andes adding L2 cache to its 32-bit and 64-bit 27-series RISC-V cores as well as multicore support to the 45-series family. Unless I’m mistaken SiFive did not launch new cores in 2020, but the SiFive Core IP 20G1 release enhanced the company’s existing RISC-V cores with performance improvements, higher efficiency, and a smaller footprint.

One great thing about RISC-V is that it is open, so it’s great for students who can create RISC-V soft cores running on FPGA platforms, and this year the University of Chinese Academy of Sciences (UCAS) developed NutShell, a 64-bit SoC which operates at up to 200MHz and can run Linux. RISC-V international could even promote the RISC-V ISA as being suitable for 13-year old kids as the young Nicholas Sharkey participated in a workshop and managed to create his own RISC-V core…

2020 RISC-V SoC announcements

Cores are nice, but for practical applications, they need to be integrated into chips or modules. There have been some interesting developments in 2020, notably in the microcontroller side of the market.

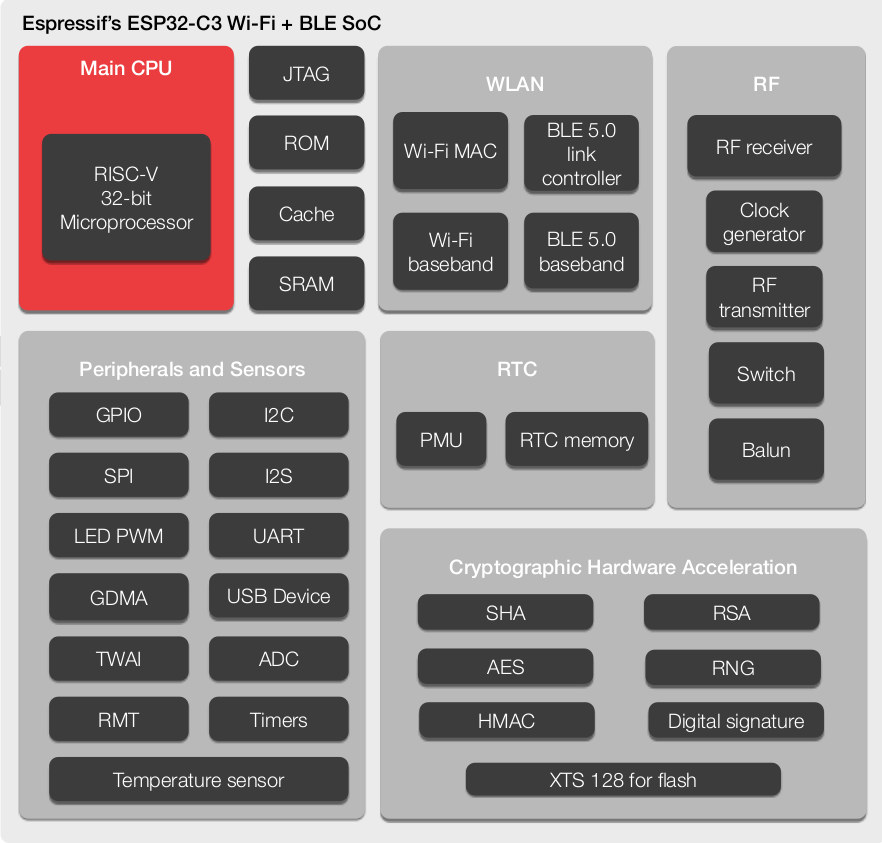

While announced at the very end of 2019, we’ll still add Greenwaves GAP9 multi-core AIoT RISC-V processor to our 2020 SoC list since it only became available this year. zGlue and Antimicro then unveiled the GEM2 chiplet-based ASIC featuring a hard RISC-V core and a Lattice iCE40 FPGA. But the most interesting announcements, or at least the ones that create the most buzz, happened in the second part of the year, with first BL602/BL604 RISC-V WiFi and BLE SoC promising to compete in price against ESP8266, then Allwinner working on a Linux capable Xuantie C906 based RISC-V processor, and finally Espressif introducing their own RISC-V WiFi & BLE IoT chip with ESP32-C3.

RISC-V development boards and SBC’s

We also had some pretty exciting announced on the RISC-V SBC’s front with Polarfire SoC Icicle RISC-V + FPGA board‘s crowdfunding campaign starting in July, then Sipeed launched a neat, fully integrated MAIX Amigo portable RISC-V AI development kit in August, and news about Picorio RISC-V alternative to Raspberry Pi broke out in September, although it’s a long term project, so it may take a while before it becomes available.

People wanting a native RISC-V development platform will have been pleased with the announcement of SiFive Unmatched RISC-V mini-ITX motherboard with a Freedom U740 quad-core processor which should have Cortex-A55 performance levels, and 16GB RAM (just upgraded from 8GB RAM in the initial announcement). RISC-V also has made its way into the education market with BBC “Doctor Who” HiFive inventor coding kit targeting STEM education for young kids. Finally, we have Pine64′ Pinecil that’s a hybrid tool and devkit since it’s a programmable RISC-V soldering iron with I/O expansion board and based on GD32V microcontroller.

RISC-V software development tools

Most people are probably using the GNU toolchain to build projects for RISC-V targets, but some commercial tools added support for the open ISA including the IAR Embedded Workbench adding support for GigaDevice Semiconductor RISC-V MCU (e.g. GD32V), and advanced trace for RISC-V based applications in collaboration with SiFive.

The obvious choice for people who want to experiment without hardware is to use QEMU emulator supporting RISC-V, but for professional who may need more advanced features and performance, Imperas OVPsim may be a better option, and the company added the first reference model with UVM encapsulation for RISC-V verification last February.

Since RISC-V ISA is open, there’s a fairly large number of cores to choose from before starting a design, and to help you select the best one for your application, Bluespec released the RISC-V Explorer, a free tool to evaluate and compare RISC-V cores.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress