Bluespec is a US company that provides RISC-V processors and development tools that “speed integration, debugging and verification of embedded systems”. Their first RISC-V release was the Piccolo 3-stage in-order processor targeting low end embedded systems and IoT applications.

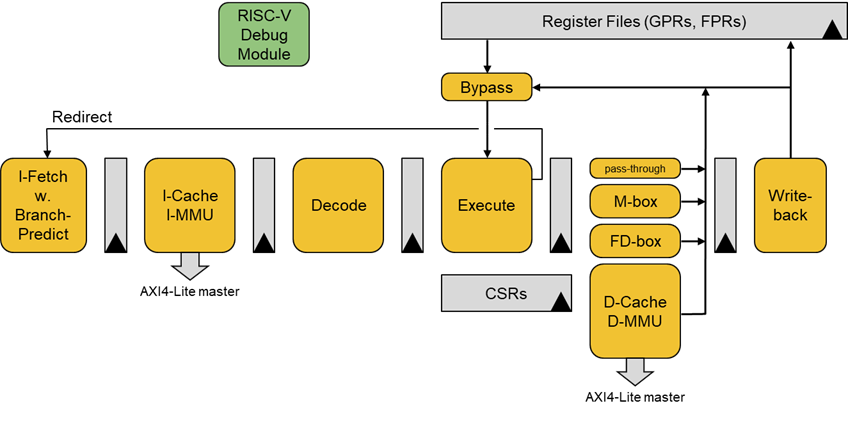

The company has now announced Bluespec Flute a 5-stage in-order open source RISC-V processor with the release of a synthesizable Verilog for a bare metal RV32IMA core and a supervisor level RV64IMA core.

- RV32IMU with ‘M’ extension (integer multiply/divide)

- RV64IMASU with ‘A’ extension (atomic memory ops) and ‘M’ extension (integer multiply/divide)

- AXI4-Lite interface

- 5-stage pipeline

- 100 MHz (Xilinx UltraScale)

- < 5000 LUTs (Xilinx UltraScale)

- 4KB Instruction & Data caches

- Hardware multiply-divide

- RISC-V Debug Module

You’ll find the source code in BSV (Bluespec SystemVerilog) and instructions to get started in Github. Bluespec Flute core has been tested in Xilinx UltraScale/UltraScale+ boards so far. In the future, the company will add floating point and compressed instructions (RV32GC/RV64GC), as well as work on Linux and FreeRTOS support.

At least one company is currently developing a commercial product based on Bluespec Flute: Calligo Technologies, an HPC/AI Company based in Bangalore, India. Anantha Kinnal, Co-founder & Director of the company, explains: “we are using Bluespec’s Flute core as a fast and efficient way to take to market our Posit Numeric Unit IP”.

Beside the Github repository, more details about Flute RISC-V core can be found on the product page.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress