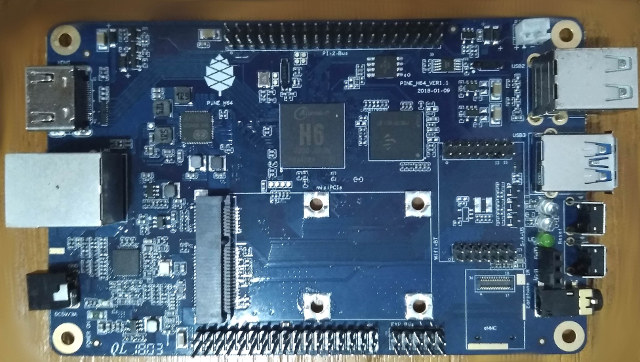

As expected, Pine64 has now launched Pine H64 development board, powered by Allwinner H6 quad core processor, and contrary to Orange Pi H6 boards, it exposes both Gigabit Ethernet, and a USB 3.0 port, which should please people wanting fast storage combined with Gigabit Ethernet.

The board comes in three variants with 1, 2 or 3GB of memory, with all also equipped with a mini PCIe interface, and various I/O headers.

Pine H64 specifications:

- SoC – Allwinner H6 quad core Cortex A53 processor with Arm Mali-T720MP2 GPU

- System Memory – 1, 2 or 3GB LPDDR3 PC-1600 RAM

- Storage – 128 Mbit SPI flash, micro SD card slot, and eMMC flash module connector (all bootable)

- Video Output – HDMI 2.0a up to 4K @ 60 Hz

- Audio – HDMI audio output,

- Video Decoding – 10-bit H.265 up to 4K @ 60 fps, VP9 and H.264 up to 4K @ 30 fps

- Connectivity – Gigabit Ethernet, headers for SDIO 3.0/UART wireless module

- USB – 1x USB 3.0 port, 2x USB 2.0 host ports

- Expansion

- 1x mini PCIe slot

- 40-pin Pi2 GPIO bus

- Euler GPIO bus

- Misc – IR receiver, RTC

- Power Supply – 5V/3A

- Dimensions – 127 x 79 mm (Same as Pine A64 board)

It’s worth noting there’s no information on the Wiki yet, and the company clearly states “PINE H64 is still in early stage development cycle, the current board condition is only suitable for developer and early adopter”, so it’s not for everybody, as software support is not there yet. We do know the board will support both Android and Linux distributions, and that Allwinner will/has release(d) a Linux 4.9 BSP, so a fairly recent kernel will be used with the board, and linux-sunxi will likely be working on mainline Linux and U-boot support for the SoC and board.

Price is quite competitive with the 1GB RAM version selling for $25.99, the 2GB RAM version for $35.99, and the 3GB board for $45.00. This does not include shipping, and accessories like the power supply. You’ll find the purchase links on Pine64 store.

In other news, the company also launch SOPINE clusterboard taking 7 Sopine64 systems-on-module for $99 with one free SoM for a limited time, but I cover this into more details tomorrow.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress