GIGABYTE, Socionext and Linaro have partnered to design a software development platform compliant with 96Boards Enterprise specifications, with GIGABYTE taking care of manufacturing the hardware based on Socionext SC2A11 processor, while Linaro will provide support via 96Boards community.

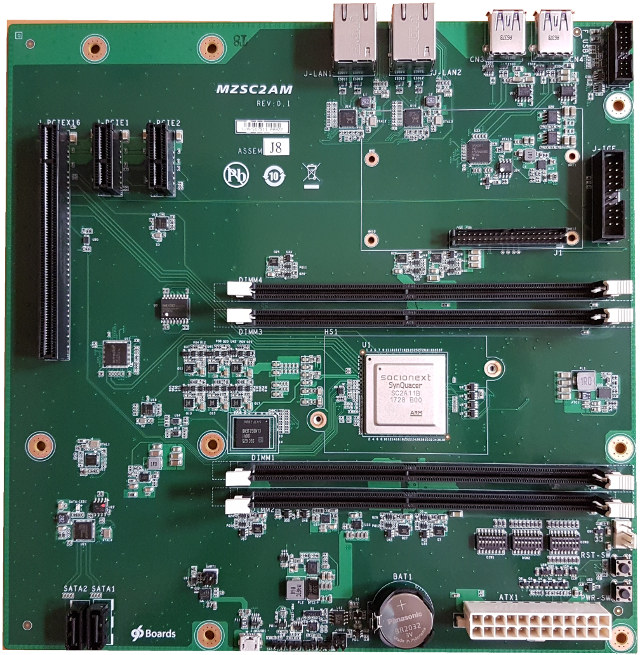

GIGABYTE SynQuacer platform preliminary specifications (based on photos and SC2A11 specifications):

- SoC – Socionext SynQuacer SC2A11 24x ARM Cortex-A53 MPCore cores @ up to 1GHz, with 32KB/32KB I/D L1 cache, 256 KB L2 cache, and 4MB L3 cache (5W power consumption)

- System Memory – 4x DIMM slots for 64-bit DDR4-2133Mbps with ECC up to 64GB

- Storage – 32GB Samsung KLMBG2JENB-B041 eMMC 5.1 flash + 2x SATA interfaces

- Connectivity – 2x Gigabit Ethernet (RJ45) with IPSec Network Offload Engine

- USB – 2x USB 3.0 ports on motherboard (via Renesas D720201), 4x USB ports on front panel via expansion board

- Audio – 1x microphone input, 1x speaker output on front panel

- Expansion – 1x PCie x16 slot (limited to 4-lanes), 2x PCIe x4 slots, other headers for expansion and/or debugging

- Misc – Power button, power and activity LEDs, reset and power switches, configuration switches, RTC battery

- Power Supply – ATX connector + ATX power supply

- Dimensions – board: microATX board (96Board Enterprise compliant)

Linaro have been working on Socionex SC2A11 SoC using their PEC boards for a while, and if you want more details you may check out Linaro Connect Budapest 2017’s presentation. Multiple PEC boards can be interconnected offering up to 1536-core servers, with those systems suitable for IoT gateways, edge computing and servers running programs such as Hadoop/Spark, e-Commerce platforms, OpenStack, and so on. As of March 2017, Socionext SC2A11 supported ARM Trusted firmware, UEFI (edk2), Linux 4.5 with all drivers, Centos 7 Aarch64 rootfs, and Hadoop.

The new development platform should become available in December 2017, and a prototype will be demonstrated during Linaro Connect San Francisco next week on September 25-29, and Yasuo Nishiguchi (Socionext) will present a related keynote at the event.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress