Historically software could only be tested and debugged when the first silicon sample was ready, and the software team could not participate in the design process.

But thanks to Virtual Hardware Platforms, software can be executed at speeds close to real time on an abstract model of the hardware, available long before a design has been completed. The virtual platform is designed to simplify the creation and support of virtual prototypes and allow design teams to begin developing software weeks to months before a hardware prototype is available, and software teams can use it as their application development platform. For example, Freescale is using a Virtual Hardware Platform for their new Vybrid Controllers to emulate both Cortex A5 and Cortex M4 cores, as well as peripherals and run OS such as Linux or MQX before the Controllers are ready (Q2 2012).

One Virtual Hardware Platform has just won the ACE AWARDS ULTIMATE PRODUCTS of 2011 in the Software category. The Cadence’s Virtual System Platform (part of Cadence System Development Suite) is based on SystemC TLM 2.0 and IEEE 1666 standard (open SystemC models), supports third-party processor models (ARM Fast Models, Imperas OVP models), Legacy RTL languages (Verilog, VHDL and SystemVerilog), third-party software debuggers (ARM DS 5, Lauterbach, GDB) and scales from single-core to multi-core software development and debug with performance reaching hundreds of MHz.

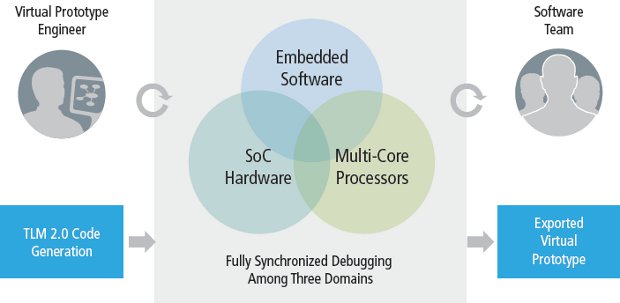

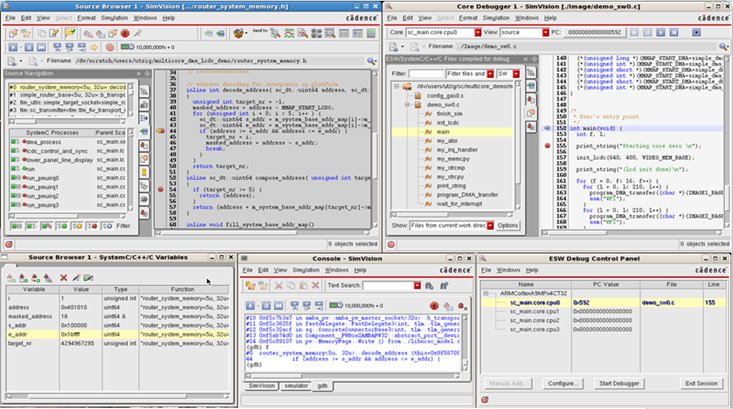

The Virtual System Platform debug GUI provides fully synchronized, coherent multi-core hardware/software (HW/SW) debugging. It comes with consistent breakpoints, single stepping, probing, tracing, and memory/register source-level debugging in either HW or SW models. Hardware debugging is based on a virtual platform-aware abstraction, built on a core of TLM-aware and SystemC debugging features. The GUI itself is segmented and can be configured for the views most familiar to software or hardware engineers, or a combination of the two for efficient HW/SW debugging.

You can use models for all sort of basics I/O including UART, keyboard/mouse controller, real time clock, programmable timer, interrupt controller, multimedia card, audio codec interface, programmable LED, color LCD, etc. Cadence also provides most advanced models for Ethernet, controller, I2C, SPI, bus controller,

serial interface, buffer, memory logger, battery, touch screen input, flash memory, initiator, multi-plexor, arbiter, router and more.

In your use such software to create a system, you’ll need a Linux machine with the following requirements:

- 64-bit Red Hat Enterprise or SUSE Enterprise

- 32GB of RAM

For software development in C/C++/Assembler, a 32-bit or 64-bit Red Hat or Suse Linux distribution with at least 2 GB of RAM is required.

You can get more information on Cadence Virtual System Platform page. Other virtual hardware platforms include Wind River Simics Virtual Platforms and the open source Imperas OVPsim simulator with examples for different processor models (ARM, MIPS, ARC, NEC v850, openCores OR1K, PowerPC). All of processor and peripheral models are a;sp open source and can be downloaded (after free registration) on OVPWorld.org forum.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress