MIPS first unveiled the MIPS P8700 series IP along with the I8500 multiprocessor IP cores in 2022, and the company has now announced the general availability of the P8700 64-bit RISC-V core. Built for Advanced Driver Assistance Systems (ADAS), ML, and software-based automotive applications, the MIPS P8700 Multiprocessing System (MPS) scales up to 64 heterogeneous clusters of out-of-order, multi-threaded multi-core MIPS CPUs.

P8700 series RISC-V processor’s RISC-V architecture

The P8700 is MIPS’ first RISC-V IP. It implements the RISC-V RV64GCZba_Zbb instruction set architecture. It allows the MPS to execute atomic operations, single-precision, and double-precision floating-point operations and incorporates bit manipulation extensions, which streamline data processing tasks. This capability with compressed instructions through the RISC-V C extension (RVC) allows for out-of-order multi-threading.

P8700 series’ out-of-order multi-threading and heterogeneous clustering

Out-of-order multi-threading simply means that the MPS processes multiple instructions simultaneously without following an order. Hence, the MPS can process even co-dependent instructions simultaneously, cluster the results, and provide the desired result faster, reducing latency. MIPS claims that the P8700 achieves up to 60% performance gains compared to in-order execution. Meanwhile, an 8-wide instruction fetch, 7-wide issue, and 4-wide decode pipeline ensure high throughput.

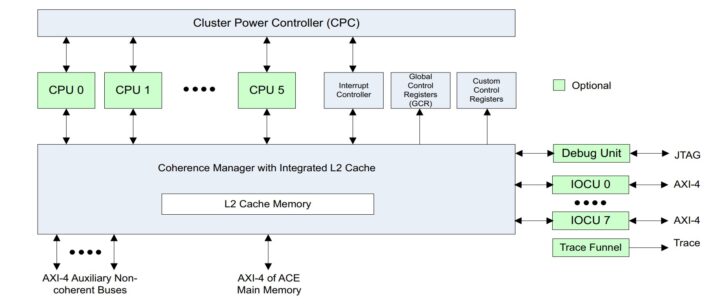

The P8700 Multiprocessing System (MPS) employs a highly scalable and configurable cluster architecture, making it suitable for diverse compute-intensive applications. Each cluster can house up to six RISC-V CPU cores and eight I/O Coherence Units (IOCUs), with a total limit of eight agents per cluster. The Coherence Manager (CM) ensures cache coherence using a directory-based protocol, managing both Level 1 (L1) and Level 2 (L2) caches, with the latter offering sizes up to 8 MB. The architecture supports up to 64 clusters, scaling to 512 cores and 2048 hardware threads (harts). Flexibility is further enhanced through independent clocking domains, allowing customized performance and power efficiency for cores, CM, and I/O interfaces. Additionally, the Cluster Power Controller (CPC) offers dynamic power management, enabling core-level power gating and clock adjustments to optimize energy use.

Configurability is a hallmark of the P8700 MPS, with options for varying the number of cores, cache sizes, IOCUs, and memory configurations to meet specific application needs. L1 and L2 caches are customizable, supporting efficient memory management with features like ECC protection and cache-to-cache data transfers. The system supports both coherent and non-coherent setups, with AXI-4 and ACE interfaces for single and multi-cluster configurations, respectively. Debugging capabilities, including PDTrace and hybrid debug modes, enhance development and troubleshooting. With this robust architecture, the P8700 MPS is well-suited for applications in automotive, machine learning, networking, and high-performance embedded systems.

MIPS P8700 to be featured in MobileEye SoCs

The MIPS P8700 will be integrated into Mobileye’s system-on-chips (SoCs) designed for autonomous driving platforms. Mobileye has incorporated MIPS processors into multiple EyeQ generations, from EyeQ2 to EyeQ6H and EyeQ6L, and now into its next-generation EyeQ platform. This also includes the anticipated Mobileye EyeQ7 and some previous generations. The partnership was announced back in 2022.

MIPS P8700: specifications

- Instruction Set Architecture: RISC-V RV64GCZba_Zbb

- Privileged Modes: Supervisor, Machine, Debug

- Cores per Cluster: Up to 6

- Threads per Core: 1 or 2

- Scalability: Up to 64 clusters, 512 cores, 2048 threads

- Pipeline: 8-wide fetch, 4-wide decode, 7-wide issue

- L1 Instruction Cache: 32 KB or 64 KB

- L1 Data Cache: 32 KB or 64 KB

- L2 Cache: 256 KB to 8 MB

- MMU Page Sizes: Up to 512 GB

- IOCUs per Cluster: Up to 8

- Internal Data Paths: 512-bit

- Debug Support: EJTAG, RISC-V trace

- Power Management: Core and cluster-level power gating

- Functional Safety: ASIL-B(D) compliant

- System Bus Interface: AMBA ACE, AXI-4

MIPS has built functional safety and configurational capability into the MIPS P8700 MPS. It is compliant with ASIL-B (D) for industrial and automotive applications, and includes parity protection and SRAM error correction.

MIPS P8700 MPS IP is now available to the broader market and shipments with OEM launches will begin soon. MIPS’ website has more useful information including the datasheet and a programmer’s guide.

Samrudhi is an analyst at Wired and Wireless Technologies (WAWT). With a passion for IoT, electronics, and power electronics, Samrudhi has been involved in writing engaging technical content for about 2 years.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress