Altera, an independent subsidiary of Intel, has launched the Altera Agilex 3 SoC FPGA lineup built on Intel’s 7nm technology. According to Altera, these FPGAs prioritize cost and power efficiency while maintaining essential performance.

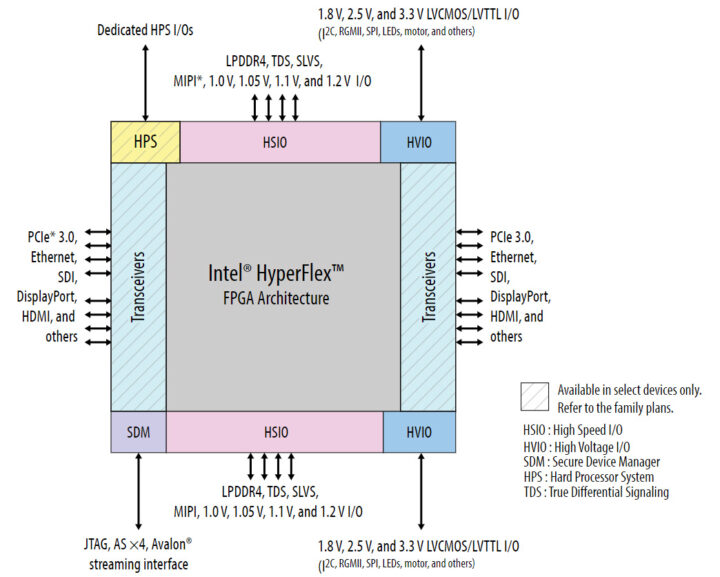

Key features include an integrated dual-core Arm Cortex A55 processor, AI capabilities within the FPGA fabric (tensor blocks and AI-optimized DSP sections), enhanced security, 25K–135K logic elements, 12.5 Gbps transceivers, LPDDR4 support, and a 38% lower power consumption versus competing FPGAs. Built on the Hyperflex architecture, it offers nearly double the performance compared to previous-generation Cyclone V FPGAs. These features make this device useful for manufacturing, surveillance, medical, test and measurement, and edge computing applications.

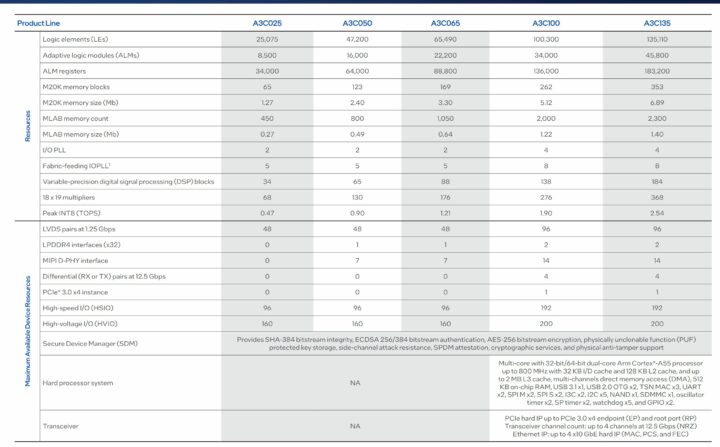

Altera’s Agilex 3 AI SoC FPGA specifications

- Device Variants

- B-Series – No definite information is available

- C-Series – A3C025, A3C050, A3C065, A3C100, A3C135 SoC FPGAs

- Hard Processing System (HPS) – Dual-core 64-bit Arm Cortex-A55 up to 800 MHz that supports secure boot, AES encryption, secure hash algorithms

- Field Programmable Gate Array (FPGA)

- 25,000 to 135,000 Logic Elements

- Up to 12.5 Gbps transceiver

- Up to 180 GFLOPS (single-precision)

- Variable precision DSP blocks (FP32, FP16, FP19, BFLOAT16, INT16 complex)

- AI Tensor Blocks (up to 2.54 INT8 TOPS)

- Memory

- Hard Processor System – 512 KB on-chip LPDDR4 RAM

- FPGA

- M20K – 20 kilobits with hard error correction code (ECC) support

- MLAB – 640-bit distributed LUTRAM

- 8.3 Mb total on-chip RAM in the C-Series devices

- External memory interface (supports up to 2,133 Mbps)

- Storage

- Supports SD/eMMC devices up to version 5.1 and SD devices up to version 6.1

- NAND flash controller supporting ONFI 1.x and 2.x, Toggle 1.x and 2.x specifications.

- Transceivers:

- Supports data rates up to 12.5 Gbps NRZ.

- Multiple Gigabit Ethernet (GbE) network interface connectivity.

- Hardened 10 GbE MAC, PCS, and FEC (with IEEE 1588 support).

- Support for PCIe 3.0 with up to x4 lanes.

- Ethernet – 3x 10 Mbps/100 Mbps/1 Gbps/2.5 Gbps Ethernet MACs with integrated DMA and Time-Sensitive Networking (TSN) support.

- USB

- USB 2.0 On-The-Go (OTG) with integrated DMA.

- USB 3.1 Gen 1.

- I/O and General Interfaces

- Up to 48 GPIOs (General-Purpose I/Os).

- Hardened PCIe support up to PCIe 3.0 x4

- MIPI D-PHY v2.5 at up to 2.5 Gbps (per lane).

- 1.25 Gbps low-voltage differential signaling (LVDS)

- 2x UART 16550-compatible controllers.

- 4x SPI controllers (two masters, two slaves).

- 5x I2C controllers.

- 2x I3C controllers.

- Timers

- Four general-purpose timers.

- Five watchdog timers.

- Security Features

- Secure boot with AES encryption.

- SHA and ECDSA authentications.

- Platform attestation with secure key provisioning.

- Package – 12 x 12 mm (lowest) in VPBGA package with 0.5 mm ball pitch

The company only provides information about the Agilex 3 C-Series SoC FPGAs on their product table from there I can see the lineup consists of 5 FPGAs including A3C025, A3C050, A3C065, A3C100, A3C135, but after searching for a little but I found out from Mouser that they also have a B-Series for which any information is not available at the time of writing.

Altera Agilex 3 chips use Altera’s 2nd generation of Hyperflex architecture, which doubles performance by adding “registers everywhere”. These bypassable registers enable faster signal routing, increasing speed and bandwidth. Combined with high-speed transceivers, Agilex 3 operates up to 12.5 Gbps and supports LPDDR4 memory, achieving 1.9x higher performance than Cyclone V.

In terms of software and tools, the company provides Quartus Prime Pro Edition design suite which streamlines FPGA design with its new compiler and Hyper-Aware flow. Additionally, Intel’s one API helps speed up software development for different types of hardware, on top of that Altera offers tools such as the Transceiver Toolkit, Platform Designer, DSP Builder, and Arms Development Studio specifically designed for Agilex 3.

Previously we have written about Agilex 7 FPGA F-Series back in 2019 when it was first introduced, then in 2024 alone, we have seen SBCs and modules like iW-RainboW-G58M, and Hitek eSOM5C-Ex based on intel Agilex 5 E-series.

At the time of writing the Agilex 3 SoC FPGA is not available for sale, but the company mentions that it will be available in Q1 2025. For more information about the Agilex 3 you can check out their product page and the press release. The company also announced 11 more new Agilex 5 FPGA-based development kits and system-on-modules (SoMs) which can be found on Altera’s Partner Showcase site.

Debashis Das is a technical content writer and embedded engineer with over five years of experience in the industry. With expertise in Embedded C, PCB Design, and SEO optimization, he effectively blends difficult technical topics with clear communication

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress