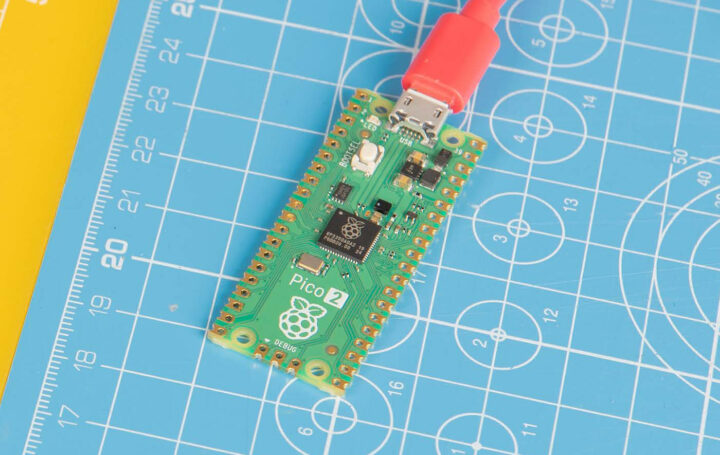

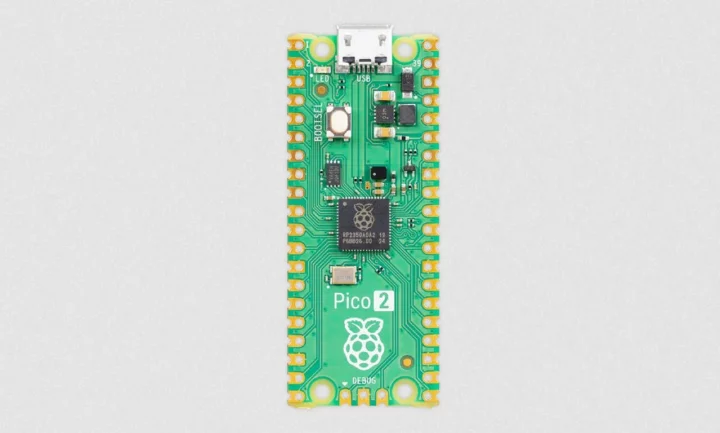

The Raspberry Pi Pico 2 is an MCU development board based on the new Raspberry Pi RP2350 dual-core RISC-V or dual-core Cortex-M33 microcontroller with 520 KB on-chip SRAM, a 4MB flash, a micro USB port for power and programming and the same GPIO headers as the Raspberry Pi Pico board with an RP2040 dual-core Cortex-M0+ microcontroller with 264KB SRAM.

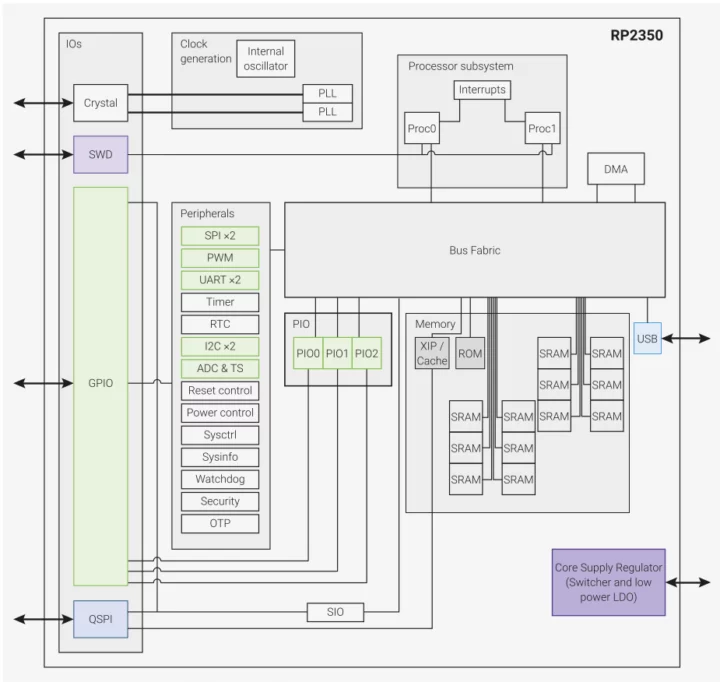

The RP2350 embeds both an open-source Hazard3 RISC-V dual-core CPU and a dual-core Cortex-M33, but only one cluster can be used at a given time. Apart from the faster MCU cores and higher SRAM capacity, the RP2350 is about the same as the RP2040, albeit it also adds one extra PIO block bringing the total to three. One important new feature is built-in security when using Arm Cortex-M33 cores with Trustzone and other security features.

Raspberry Pi RP2350 microcontroller

Let’s have a closer look at the RP2350 microcontroller, before checking out the Raspberry Pi Pico 2 board.

Raspberry Pi RP2350 specifications:

- CPU

- Memory – 520 KB on-chip SRAM

- Storage – Up to 16MB external QSPI flash

- Peripherals

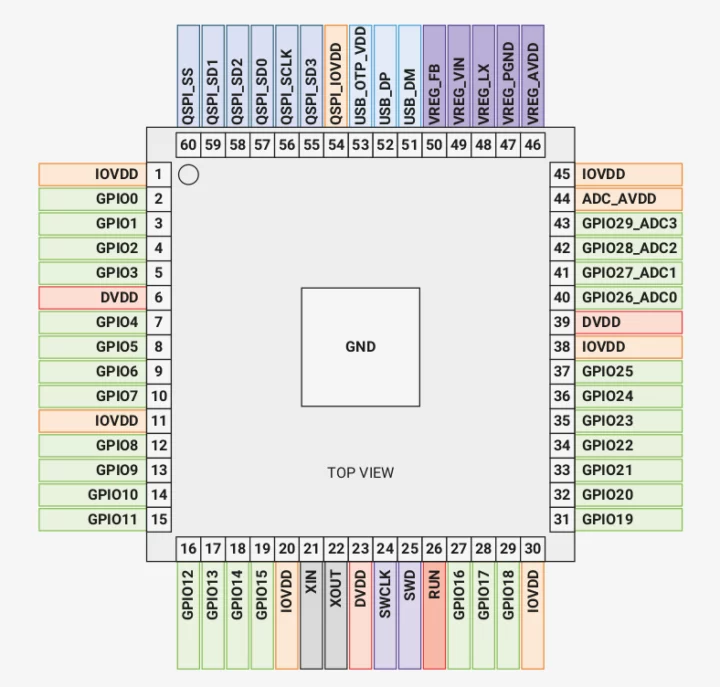

- RP2350A: up to 30x GPIOs, up to 4x ADC, up to 16x PWM channels

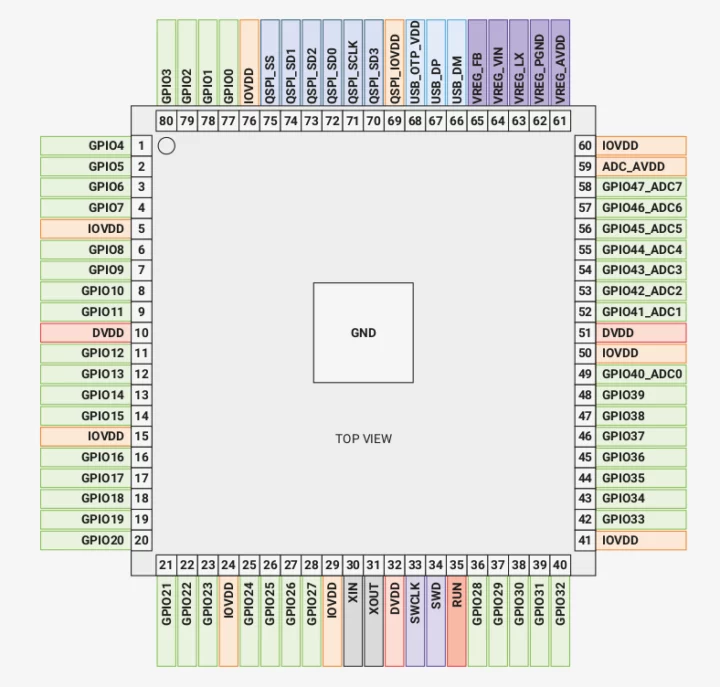

- RP2350B: up to 48x GPIOs, up to 8x ADC, up to 24x PWM channels

- USB 1.1 host/device

- 2x UART

- 2x SPI controllers

- 2x I2C controllers

- 3x PIO blocks, 12x PIO (Programmable IO) state machines

- HSTX (high-speed serial transmit) streams data from the system clock domain to up to 8 GPIOs (IO12-IO19) at a rate independent of the system clock.

- Temperature sensor

- Security

- 8KB of anti-fuse OTP for key storage

- SHA-256 acceleration

- Hardware TRNG

- Fast glitch detectors

- Debugging – SWD Debug interface

- Low power – Extended low-power sleep states with optional SRAM retention: as low as 10 μA DVDD

- Package

- RP2350A – QFN-60; 7×7 mm

- RP2350B – QFN-80; 10×10 mm

As I understand it, the RP2350A package offers also the same pinout as the RP2040 microcontroller, but the company now also adding a larger RP2350B package with additional GPIOs and analog inputs.

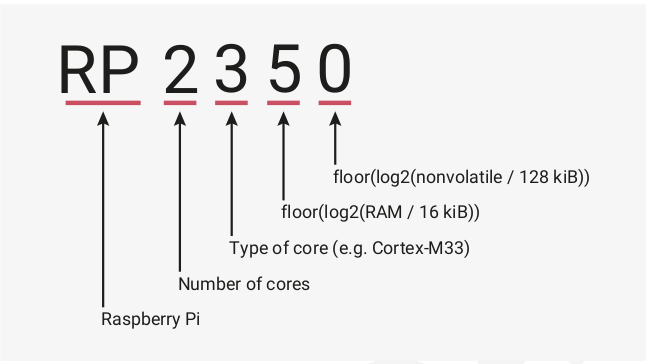

Raspberry Pi used the same method as for the RP2040 to derive the RP2350 name. RP stands for “Raspberry Pi”, “2” is the number of cores, “3” refers to the MCU core used (e.g. Cortex-M33), and the last two numbers “4” and “0” use floor(log2(x/16k)) formula to calculate a number representing the SRAM and non-volatile storage capacity inside the chip.

I can see some reference to RP235x online, so we may see an RP2354 or similar in the future with embedded flash. [Update: RP2354A and RP2354B packages will be sold with 2MB flash]

Arm/RISC-V switching is explained as follows in the datasheet:

RP2350 supports both Arm and RISC-V processor architectures. SDK-based programs which do not contain assembly code typically run unmodified on either architecture by providing the appropriate build flag.

There are two processor sockets on RP2350, referred to as core 0 and core 1 throughout this document. Each socket can be occupied either by a Cortex-M33 processor (implementing the Armv8-M Main architecture, plus extensions) or by a Hazard3 processor (implementing the RV32IMAC architecture, plus extensions).

When a processor reset is removed, hardware samples the ARCHSEL register in the OTP control register block to determine which processor to connect to that socket. The unused processor is held in reset indefinitely, with its clock inputs gated. The default and allowable values of the ARCHSEL register are determined by critical OTP flags:

1. If CRIT0_ARM_DISABLE is set, only RISC-V is allowed.

2. Else if CRIT0_RISCV_DISABLE is set, only Arm is allowed.

3. Else if CRIT1_SECURE_BOOT_ENABLE is set, only Arm is allowed.

4. Else if CRIT1_BOOT_ARCH is set, both architectures are permitted, and the default is RISC-V.

5. If none of the above flags are set, both architectures are permitted, and the default is Arm.

The presence of RISC-V cores is probably as a first try for experimentation, and future Raspberry Pi microcontrollers may end up being RISC-V only. Let’s wait and see.

Raspberry Pi Pico 2 specifications

- SoC – Raspberry Pi RP2350

- CPU

- Dual-core Arm Cortex-M33 @ 150 MHz with Arm Trustzone, Secure boot OR

- Dual-core RISC-V Hazard3 @ 150 MHz

- Memory – 520 KB on-chip SRAM

- Security

- 8KB of anti-fuse OTP for key storage

- Secure boot (Arm only)

- SHA-256 acceleration

- Hardware TRNG

- Fast glitch detectors.

- Package – QFN-60

- CPU

- Storage – 4 MB on-board QSPI flash

- USB – Micro USB 1.1 host/device connector for power and programming

- Expansion – 2x 20-pin headers with

- 26x GPIO

- 2x UART

- 2x SPI controllers

- 2x I2C controllers

- 16x PWM channels

- 4x ADC

- 3x PIO blocks, 12x PIO (Programmable IO) state machines

- Debugging – SWD debug interface

- Power Supply – 1.8 to 5.5V DC

- Dimensions – 51 x 21 mm

- Temperature Range – -20°C to +85°C

My Raspberry Pi Pico 2 should be delivered by DHL today or tomorrow, so I haven’t been able to play with it yet, but as I understand it, it will use the same C/C++ and Python SDK as for the Raspberry Pi Pico/RP2040 plus extra features for the security, and a new toolchain for the RISC-V if you’re going to use it. More details should now be available on the documentation website, as well as on GitHub with the Pico SDK and examples.

Third-party RP2350 boards will launch at the same time as the Raspberry Pi Pico 2 board, and I already have a Cytron MOTION 2350 PRO board for robot control with an RP2350A microcontroller on my desk…

Raspberry Pi Pico 2 is available as an individual unit, or in 480-unit reels, and will remain in production until at least January 2040, or a 16-year life cycle. The price is $5 before taxes and shipping or just one dollar more than the first-generation $4 Raspberry Pi Pico. [Update: some price information has been released for the RP2350 microcontroller. The RP2350A will be ten cents more expensive than the RP2040, costing $0.80 in 3,400-unit reels, or $1.10 in single-unit quantities. The RP2350B will cost ten cents more than the RP2350A, and the RP2354 variants with 2MB flash will cost just twenty cents more than the flashless RP2350 SKUs. The RP2350 will become available in volume by the end of 2024]

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

RISC-V FTW!

Does it have 2 CPUs each or just 2 instruction decoders each?

Two separate dual-core clusters for a total of four cores, but only one architecture can be used at a time.

Actually both architectures can be used at the same time. There’s no “clusters” per-se, there’s just a peripheral connected directly to the cores that allows the cores to communicate and a common memory bus. Each core complex has a mux between RISC-V and ARM core, and only one of them can be running at the time, but as there are two such complexes, you can mix and match ARM and RISC-V between them. See page 35 for more details.

Thanks for the correction ignaloidas.

4MB eMMC flash? I think something went a bit wrong here.

later it’s indeed written 4MB QSPI flash 🙂

If only it had some wifi or thread

Sure it would be nice if they had separate models with built-in native WiFi, Bluetooth, and/or Thread on the same chip, however as it stands now all and any manufacturers of RP2350-based boards/products still have the option to add one or more additonal chips for wireless communcation. There are for example already many RP2040-based boards that also add an ESP32, ATWINC1500, CYW43xxx, nRF52/nRF53 or other chip(s) from for WiFi, BLE, Thread, Zigbee, etc.

If you’re adding an ESP32, do you even need the RP2350? The ESP32 is not just a wifi chip but a serious competitor to the RP2350 with advantages and disadvantages. Obviously the ability to do wifi on its own is a major advantage…

Yeah i agree, if you need to add a esp32 you can probably just drop the RP, and i think most other wifi and thread chips also contain an arm or other soc

I’m a big fan of RISC-V, but the advantage of developing for it instead of ARM when both are available in the same MCU isn’t clear to me. Everything else being the same (clock, # of cores, etc as seems to be the case here) ARM is more established and usually more performant due to a more optimized toolchain and libraries.

I can see the motivation for the manufacturer (RISC-V pays no royalties), but not for the developer.

I suspect the goal is to count on the community to make the move to RISC-V and count on the Arm availability to rassure those who would not have considered a RISC-V for their project. At some point, some libs/drivers will probably be available for RISC-V and not yet for Arm or will just not be totally up to date there, and it’s possible that users will start to consider making the switch. After a few years it might be conceivable to drop the Arm cores and lower royalties. I anticipated that already with the SophGo SG2002 (risc-v+A53), and indeed,… Read more »

Pretty clear what the intention is, if you scroll waaaaay down on the launch announcement from Upton:

This looks interesting Two separate architectures to use on one platform.

To put things into perspective, the ARM cpu is quite a step up.

The M0(+) in the RP2040 is in the lowest range of the ARM cores and M33 is more on the upper end, closer to the very popular Cortex- M4: ARMv8 instruction set, optional FPU and DSP and the DMIPS/MHz and CoreMark/MHz are a ~70-80% increase. As always these are just numbers but this should significantly improve the performance/timings for some use-cases.

Is it known whether the 2350 has the DSP and FPU options?

See this comparison table: https://documentation-service.arm.com/static/61bb37962183326f2176f8cc?token=

According to the docs it does have hardware fpu

“The two Cortex-M33 instances are identical. They are configured with the Security, DSP and FPU extensions, as well as 8× SAU regions, 8× Secure MPU regions and 8× Non-secure MPU regions. Section 3.7 documents the Cortex-M33 processor as well as the specific configuration used on RP2350. The two Hazard3 instances are also identical to one another; see Section 3.8 for the features and operation of the Hazard3 processors.”

While it is a very big step up the fact that you must execute the code from QSPI might end up as a bottleneck. Which is why they put the cache for the QSPI flash but you would still likely find performance degradation over an ITCM flash.