Sipeed MaixCAM is an AI camera based on SOPHGO SG2002 RISC-V (and Arm, and 8051) SoC with a 1 TOPS NPU that takes up to 5MP camera modules and comes with a 2.3-inch color touchscreen display.

The development kit also comes with WiFi 6 and BLE 5.4 connectivity, optional Ethernet, audio input and output ports, a USB Type-C port, and two 14-pin GPIO headers for expansion that makes it suitable for a range of computer vision, Smart audio, and AIoT applications.

Sipeed MaixCAM specifications:

- SoC – SOPHGO SG2002

- CPU

- 1 GHz RISC-V C906 processor or Arm Cortex-A53 core (selectable at boot) running Linux

- 700 MHz RISC-V C906 core running an RTOS

- 25 to 300 MHz low-power 8051 processor

- NPU – 1 TOPS @ INT8 with support for models such as Mobilenetv2, YOLOv5, YOLOv8, etc…

- Video Codec – H.264, H.265, MJPEG hardware encoding and decoding up to 2K @ 30fps

- Memory – 256MB DDR3

- CPU

- Storage

- MicroSD card slot (bootable)

- SD NAND flash (bootable)

- Display – 2.3-inch IPS capacitive touchscreen display with 552×368 resolution; connected through a 31-pin, 2-lane MIPI DSI connector and a 6-pin capacitive touch connector

- Camera I/F – 4-lane MIPI CSI input via 22-pin connector for up to 5MP cameras. Supports 4MP GC4653 and OS04A10 cameras out of the box

- Audio Output – On-board power amplifier for 1W speakers via headers

- Audio Input – Onboard analog silicon microphone

- Networking

- WiFi 6 and BLE 5.4 module

- Customizable Ethernet version

- USB – USB 2.0 Type-C port

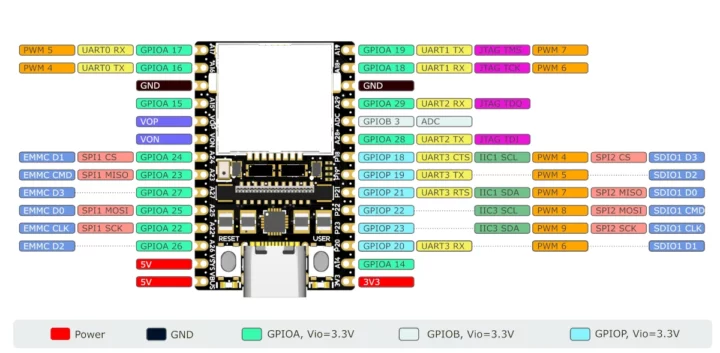

- Expansion – 2x 14-pin 2.54mm pitch GPIO headers with I2C, SPI, UART, ADC, PWM, WDT

- Misc –

- RST button, USER button

- Power indicator, user LED

- Power Supply – 5V via USB-C port

- Mechanical – 3D printed enclosure, two threaded holes

The MaixCAM builds on the company’s board based in LicheeRV-Nano board powered by the SG2002 SoC and all software for the board can run on the camera including the Debian and Qt-based Linux images. Willy – a regular CNX Software reader and commenter – tried one of those two months ago, but was rather unimpressed with usability (e.g. no SSH) and the delta compared to the latest Linux 5.10, and ended up rebasing the code to Linux 5.10.251. There’s a very large number of changes (about 25,000), and the git pull request has yet to be processed by SOPHGO.

There’s also software specific to the Sipeed MaixCAM which we are told won’t work on the LicheeRV-Nano or other SG2002 boards which are better suited for Linux development:

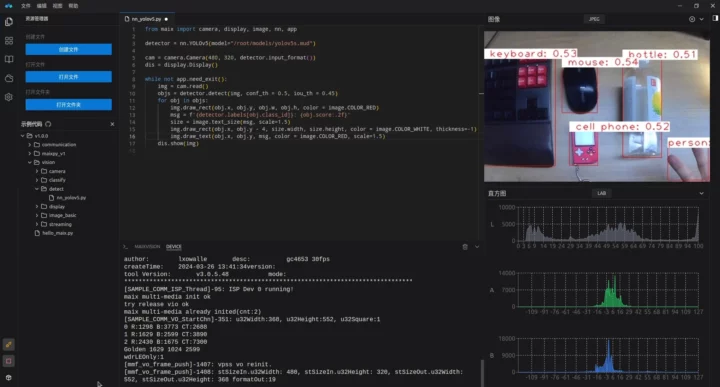

- MaixPy – Python development package with an API optimized for MaixCAM that supports hardware acceleration

- MaixVision – AI Vision IDE for programming, running code, real-time image preview, and even block-based programming

- MaixCDK – C++ version of MaixPy

You’ll find all three along with other technical details in the wiki. To make things even easier, Sipeed provides the MaixHub with a list of pre-trained AI models that can be directly uploaded to the MaixCAM hardware. Example apps include a simple HTTP streamer, face detection, fire detection, and a few others, as the list is not super long right now. You can also access those by tapping on the “App Store” button in the user interface on the 2.3-inch display.

Sipeed has started selling the MaxiCAM RISC-V AI camera on Aliexpress for about $40 for a kit with a 4MP camera and accessories.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress