With the Star64 and VisionFive 2 single board computers, we’ve already got two hardware platforms based on the StarFive JH7110 quad-core RISC-V processor, but somehow we did not get the detailed specifications of the new processor, and some details such as the presence of AI accelerators or exact PCIe specifications were lacking.

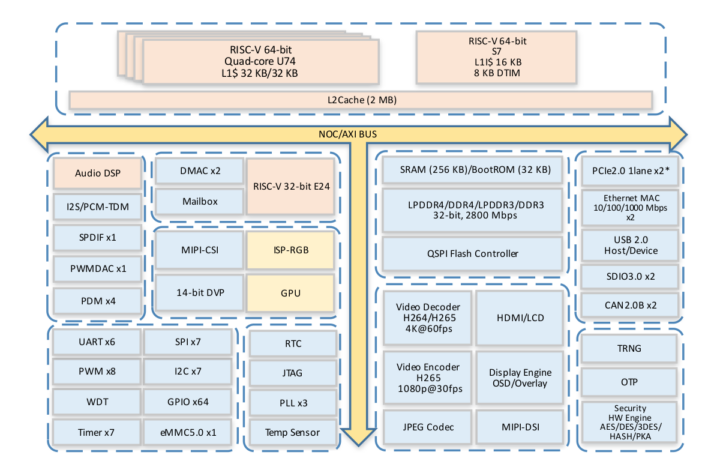

Some documentation for the StarFive JH7110 processor has been released and answers some of those questions. It’s actually an SoC with six RISC-V cores, of which four 64-bit RISC-V cores run the main OS, plus a 64-bit RISC-V monitoring core, and a 32-bit RISC-V real-time core. The AI accelerators found in the JH7100 (Neural Network Engine and NVDLA) appear to be gone for good, and there are two 1-lane PCIe 2.0 interfaces up to 5 Gbps each.

StarFive JH7110 specifications:

- CPU sub-system

- Quad-core 64-bit RISC-V SiFive U74 (RV64GC) processor @ up to 1.5 GHz with 32KB D-Cache, 32KB I-cache

- Single-core 64-bit RISC-V SiFive S7 (RV64IMAC) monitor core with 16KB I-cache, 8KB DTIM

- Single-core 32-bit RISC-V SiFive E24 (RV32IMFC) real-time control core with 16KB I-cache

- Up to 2MB L2 cache

- GPU – Imagination BXE-4-32 GPU with support for OpenCL 1.2, OpenGL ES 3.2, Vulkan 1.2

- Video Decoder – H.265, H.264 4K @ 60fps or 1080p @ 30fps, MJPEG

- Video Encoder – H.265/HEVC Encoder, 1080p @ 30fps

- Memory

- BUS RAM up to 256KB

- Up to 8GB DDR4/3, LPDDR4/3 at 2133/2800 Mbps

- Storage

- 2x SDIO/eMMC 5.0 host controllers

- QSPI controller for up to 16MB SPI flash, up to 2GB SPI NAND flash

- Display interfaces

- 1x HDMI 2.0 up to 4Kp30

- RGB656, RGB888 up to 1080p30

- MIPI DSI up to 2.5 Gbps or 1080p30

- 1x DPI (Parallel RGB Display)

- Camera interfaces

- 1x MIPI CSI-2 interface up to 6 lanes of 1.5 Gbps; support for 1x 4D1C or 2x 2D1C MIPI sensors up to 4Kp30

- 1x DVP sensor input interface

- Audio

- 32-bit audio DSP used for traditional audio/voice data algorithm processing

- 8-channel TX and RX I2S/PCM TDM

- 4x sets of I2S/PCM I/F with DMA support

- 2x sets of SPDIF I/F, RX and TX modes

- 4-channel PDM input for digital MIC

- DAC output with PWM interface

- Networking – 2x Gigabit Ethernet with RMII/RGMII

- USB – USB 3.0 host/device (multiple with one PCIe interface), USB 2.0 host/device

- PCIe – 2x PCIe 2.0 x1 up to 5 Gbps per lane (Note one of the PCIe 2.0 interface is multiplexed with USB 3.0)

- Other peripherals

- 6x UART, 7x I2C, 7x SPI

- 2x CAN 2.0B Bus up to 1 Mbps

- 7x 32-bit timers, 1x 32-bit WDT reset output

- 1x temperature sensor

- 3x GPCLK outputs

- 2x INTC

- 8x PWM outputs

- 64x GPIO

- Security

- Encryption: AES; DES/3DES; HASH; PKA

- Compliant with TRNG

- 256-bit random number generation

- 512 x 32-bit (2 KB) of OTP for key data on-die storage

- Clock sources

- 24 MHz for USB, GMAC, and system main clock source

- 32.768 kHz for RTC clock source

- Voltages

- 0.9V core voltage

- 1.8V/2.5V/3.3V I/O voltage

- Boot modes

- Boot Rom

- QSPI NOR/NAND Flash

- SD card/eMMC

- UART/USB/SD card update

- Package – 17 x 17 mm, 0.65 mm ball pitch, FCBGA package with 625 balls

Supported operating systems include Linux, VxWorks, and other RTOS.

Target applications for the StarFive JH7110 processor include single board computers, home NAS, routers with software routing, Smart Home appliances, industrial robots, drones, and video surveillance applications. The documentation website comes with a product brief and a datasheet, and a hardware design reference plus a software developer guide are also in the works.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress