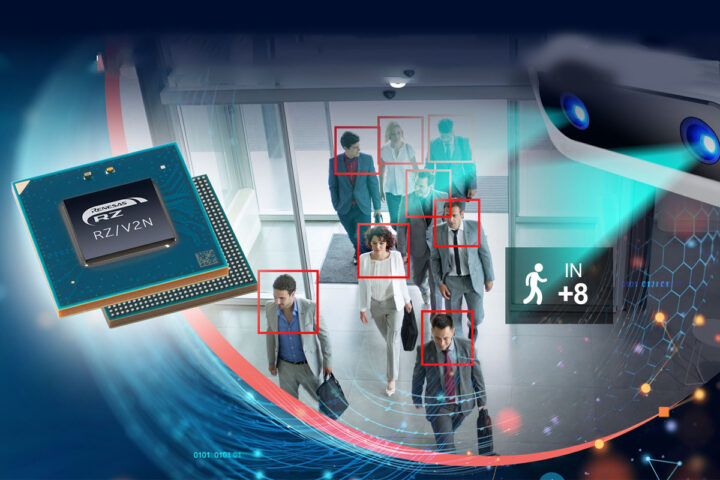

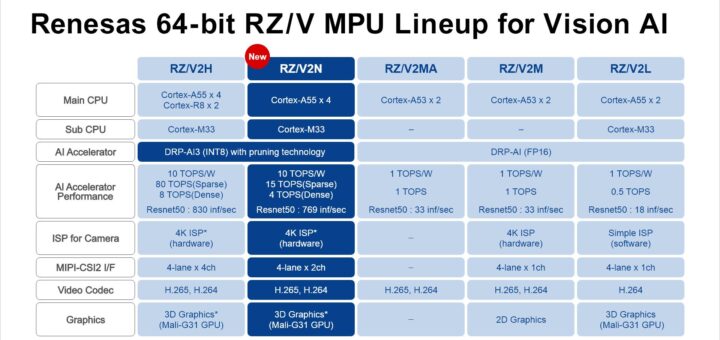

Renesas has recently introduced the RZ/V2N low-power Arm Cortex-A55/M33 microprocessor designed for machine learning (ML) and computer vision applications. It features the company’s DRP-AI3 coprocessor, delivering up to 15 TOPS of INT8 “pruned” compute performance at 10 TOPS/W efficiency, making it a lower-power alternative to the RZ/V2H.

Built for mid-range AI workloads, it includes four Arm Cortex-A55 cores (1.8GHz), a Cortex-M33 sub-CPU (200MHz), an optional 4K image signal processor, H.264/H.265 hardware codecs, an optional Mali-G31 GPU, and a dual-channel four-lane MIPI CSI-2 interface. The chip is around 38% smaller than the RZ/V2H MPU and operates without active cooling. The RZ/V2N is suitable for applications like endpoint vision AI, robotics, and industrial automation.

Renesas RZ/V2N specifications

- CPU

- Application Processor – Quad-core Arm Cortex-A55 @ 1.8 GHz (0.9V) / 1.1 GHz (0.8V)

- L1 cache – 32KB I-cache (with parity) + 32KB D-cache (with ECC) per core

- L3 cache – 1MB (with ECC, max frequency 1.26 GHz)

- Neon, FPU, MMU, and cryptographic extension (for security models)

- Armv8-A architecture

- System Manager – Arm Cortex-M33 @ 200 MHz

- FPU, DSP extension, and security extension

- Armv8-M architecture

- Application Processor – Quad-core Arm Cortex-A55 @ 1.8 GHz (0.9V) / 1.1 GHz (0.8V)

- AI accelerator – DRP-AI Up to 4 dense TOPS / 15 sparse TOPS

- 3D graphics engine (GE3D) (optional) – Arm Mali-G31

- Single-pixel shader core

- 8KB L2 cache

- Supports OpenGL ES 1.1/2.0/3.2, OpenCL 2.0 Full Profile

- Arm Mali-C55 Image signal processor (ISP) (optional)

- Supports 4K processing, HDR (2-exposure), and various image enhancements

- Max pixel rate – 630 Mpixels/s

- Input – RAW8/10/12/14/16/20

- Output – YUV422, YUV420, RGB

- Image scaling unit (ISU)

- Bilinear scaling down

- Max input/output resolution: 4096×4096

- Supports RGB/ARGB, YCbCr/YUV, RAW (Grayscale)

- Video codec unit (VCD)

- H.264 / H.265 encode & decode

- Max resolutions

- H.264: 1920×1080 @ 60 fps

- H.265: 3840×2160 @ 30 fps

- I-/P-slice support for both encoding & decoding

- Memory

- System RAM – 1.5MB (with ECC)

- External Memory – LPDDR4 / LPDDR4X-3200 (32-bit bus, up to 8GB, in-line ECC)

- Storage

- SDHI interface supporting eMMC/SD (1-, 4-, 8-bit bus width)

- xSPI controller for external flash (1x channel, 2x chip select)

- Display – 1x MIPI DSI display interface (1, 2, or 4 lanes)

- Camera – 2x MIPI CSI-2 camera interfaces (1, 2, or 4 lanes)

- Audio

- I2S (TDM) input/output interfaces

- 3x SPDIF input/output interfaces

- 6x Pulse density modulation (PDM) input interfaces

- Ethernet – 2x GbE LAN (10/100/1000BASE)

- USB – 1x USB 3.2 Gen2 host

- PCIe – 1x PCIe Gen3 (1-lane)

- Other Peripherals

- 3x SPI, 9x I2C, 1x I3C, 10x UART, 5x SCIF

- 6x CAN/CAN FD (ISO11898-1 compliant)

- 12-bit ADC (24 channels) with up to 2.5 Msps sampling rate

- 2x internal temperature sensors

- Debug – JTAG / SWD debug interface

- Security

- Arm TrustZone

- Secure Boot with RSA/ECC

- Crypto Engine

- TRNG, Unique ID

- Misc

- Boot – Selectable boot CPU from Cortex-M33 or Cortex-A55

- 4x Watchdog Timer (WDT)

- On-chip OTP (One-Time Programmable) memory

- RTC

- Direct Memory Access Controller (DMAC) – 80 channels

- Event Link Controller (ELC) – 461 event signals

- Interrupt Controller (GIC-600) for Cortex-A55

- Operating voltage – 3.3V I/O, 0.8V core voltage

- Packages – 840-pin FCBGA, 15mm × 15mm dimensions, 0.50mm pitch

- Junction temperature – -40°C to 125°C (industrial grade)

The RZ/V2N low-power AI MPU has support for various software and tools for AI, graphics, and embedded development. It includes the DRP-AI Translator for AI model conversion, AI SDKs for rapid AI application development, and ISP and video codec support packages. The Verified Linux Package ensures stable OS support, while the RZ MPU Graphics and Video Codec libraries enable GPU-accelerated rendering. The Smart Configurator simplifies software integration, and the e² studio IDE supports development with debugging tools. Additional resources include OpenCV acceleration, HTML5 frameworks, and security packages for Linux-based deployments. There is also a sample code available, which is also available on the products page.

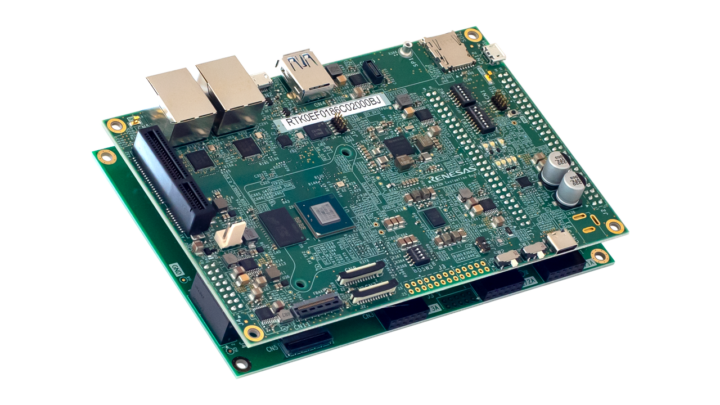

The RZ/V2N Evaluation Kit (RTK0EF0186C03000BJ) is designed for testing and development with the RZ/V2N quad-core vision AI MPU. It includes a CPU board, an expansion (EXP) board, and two sub-boards for microSD and eMMC storage. It provides high-speed interfaces, including Gigabit Ethernet, USB 3.2, PCIe Gen3, and MIPI CSI-2/DSI.

Previously we have written about the RZ/V2MA dual-core Arm Cortex-A53 MPU, the development boards based on the RZ/V2L MPUs for lower-end ML applications. Other low power AI MPUs include the Microchip PIC64HX1000 64-bit RISC-V AI MPU and Microchip SAMA7G54 AI MPU compatible with OpenCV for image processing.

Renesas says the RZ/V2N will be available from March 19, 2025. The company is showcasing it at Embedded World 2025 in Germany (Hall 1, Stand 234) and will highlight its solutions at upcoming industry events. More details are available on the product page and press release.

Debashis Das is a technical content writer and embedded engineer with over five years of experience in the industry. With expertise in Embedded C, PCB Design, and SEO optimization, he effectively blends difficult technical topics with clear communication

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress