Founded about three years ago, Akeana has just officially launched and announced three 32-bit and 64-bit RISC-V processor lines and SoC IP with the Akeana 100 series for 32-bit microcontrollers, the Akeana 1000 series for 64-bit processors with MMU, and the Akeana 5000 series with much higher single-thread performance and designed for laptops, data centers, and cloud infrastructure.

The company also introduced Scalable Coherent Interconnect, Interrupt Controller, and IOMMU IP for building out compute subsystems based on the aforementioned RISC-V cores, as well as AI-targeted Vector RISC-V Cores and Matrix Computation IP. The design team is said to have previously worked on Marvell’s ThunderX2 server chips.

Akeana 100 Series

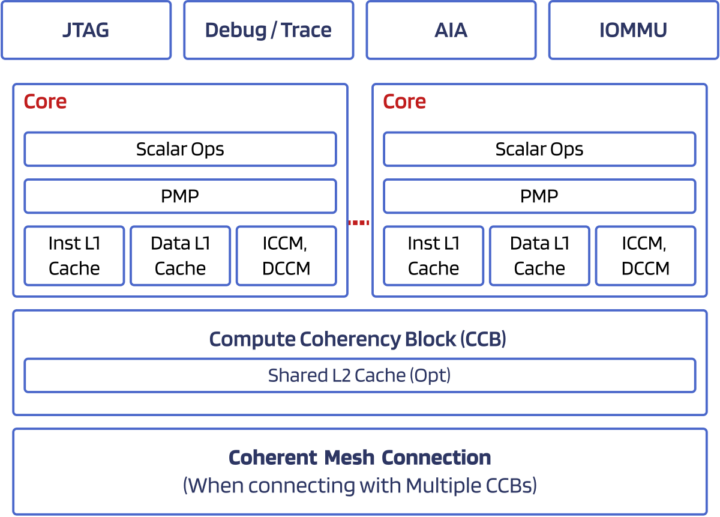

The Akeana 100 Series is a line of highly configurable processors with 32-bit RISC-V cores that support applications from embedded microcontrollers to edge gateways, to personal computing devices.

Four Akeana 100 RISC-V cores are available

- Akeana 110 for area- and power-constrained microcontrollers

- L1 I-cache: 8 KB/core

- RV32IMAC_Zicsr_Zifencei_Zicbo instruction set

- Up to 32 bits Physical Address range

- 4-stage, in-order pipeline

- Single-width instruction issue

- ICCM: 16 KB/core

- DCCM: 16 KB/core

- Akeana 120, 130, 140

- Common features

- L1 I-cache: 16 KB/core

- RV32IMAC_Zicsr_Zifencei_Zicbo instruction set

- Up to 32 bits Physical Address range

- Physical Memory Protection (PMP) with 8 entries

- Akeana 120 for area- and power-constrained microcontrollers

- 5-stage, in-order pipeline

- Single-width instruction issue

- ICCM: 64 KB/core

- DCCM: 64 KB/core

- Akeana 130 for microcontrollers

- 9-stage, in-order pipeline

- Dual instruction issue

- ICCM: 64 KB/core

- DCCM: 64 KB/core

- Branch predictor

- Secondary ALU for enhanced performance

- Akeana 140 for enhanced performance microcontrollers

- 9-stage, in-order pipeline

- Dual instruction issue

- L1 D-cache: 16 KB/core

- ICCM: 512 KB/core

- DCCM: 512 KB/core

- Branch predictor

- Secondary ALU for enhanced performance

- Common features

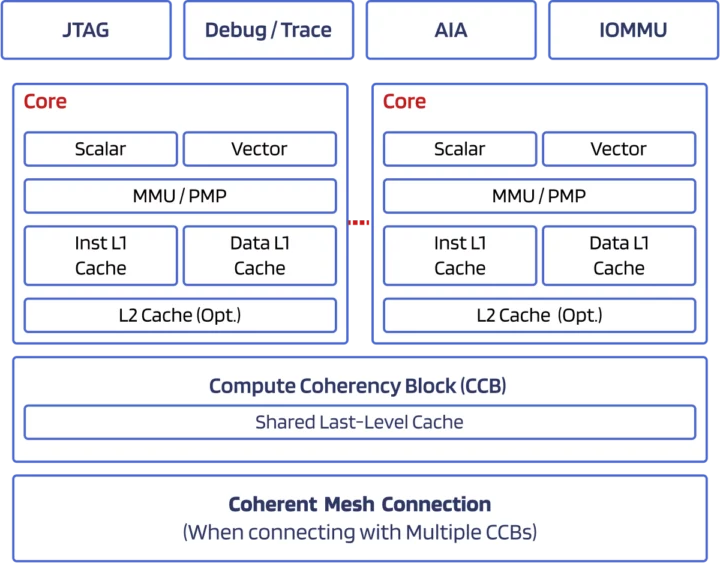

Akeana 1000 Series

Akeana 1000 Series is a processor line that includes 64-bit RISC-V cores and an MMU to support rich operating systems while maintaining low power and requiring low die area. These processors support in-order or out-of-order pipelines, multi-threading, vector extension, hypervisor extension, and other extensions that are part of recent and upcoming RISC-V profiles (e.g. RVA23), as well as optional AI computation extensions.

Three Akeana 1000 RISC-V cores are currently offered:

- Common features

- RV64GCB_Zicbo instruction set

- Full RVA22 RISC-V Profile

- Single- & double- precision floating-point

- User Mode

- Supervisor Mode

- 48 bits Virtual Address Range

- 39 bits Physical Address Range

- Scalable to fully coherent many-core clusters

- ECC support

- AXI/ACE (512 bits)

- Physical memory Protection (PMP) with 16 entries MU

- Akeana 1100 for high-end microcontrollers

- 9-stage, in-order pipeline

- Dual instruction dispatch

- L1 I-cache: 16 KB/core

- L1 D-cache: 16 KB/core

- MMU with 256-entry, 4-way TLB

- Akeana 1200 for edge gateway SoCs

- 9-stage, in-order pipeline

- 3-way instruction dispatch

- Secondary ALU in pipeline

- L1 I-cache: 32 KB/core

- L1 D-cache: 32 KB/core

- MMU with 256-entry, 4-way TLB

- Akeana 1300 for edge gateway SoCs, or as the “Little” core in Big/Little configurations with Akeana 5000 Series cores

- 12-stage, out-of-order pipeline

- 4-way instruction dispatch

- L1 I-cache: 32 KB/core

- L1 D-cache: 32 KB/core

- L2 cache: 256KB

- MMU with 512-entry, 4-way TLB

Akeana 5000 Series

Akeana 5000 Series is a line of high-performance RISC-V processors which the company claims outperforms “established competitors and the RISC-V ecosystem”. This line provides 64-bit RISC-V cores optimized for demanding applications in next-gen devices, laptops, data centers, and cloud infrastructure. These processors are compatible with the Akeana 1000 Series but with much higher single-thread performance.

Three Akeana 5000 Series RISC-V cores have been designed

- Common features

- RV64GCVBK_Zicbo + USH instruction set

- Full RVA23 RISC-V Profile

- Single and Double-Precision Floating-Point

- User Mode

- Supervisor Mode

- Hypervisor extension

- Vectorextension (128 bits)

- Vector Crypto extension

- 12-stage, out-of-order pipeline

- 48 bits Virtual Address Range

- 256K L2 cache

- Scalable to fully-coherent many-core clusters

- ECC support

- AXI/ACE (512 bits)

- Physical Memory Protection (PMP) with 16 entries

- MMU

- Akeana 5100 to be used as the “Big” core in Big/Little configurations with Akeana 1000 Series Little cores

- 4-way instruction dispatch

- L1 I-cache: 32 KB/core

- L1 D-cache: 32KB/core

- 33 bits Physical Address Space

- MMU with 512-entry, 4-way TLB

- Akeana 5200 to be used in laptop SoCs as the “Big” core in Big/Little configurations with Akeana 1000 Series Little cores

- 6-way instruction dispatch

- L1 I-cache: 32 KB/core

- L1 D-cache: 32 KB/core

- L2 cache prefetcher

- 39 bits Physical Address Space

- MMU with 1024-entry, 4-way TLB

- Akeana 5300 – A data center/infrastructure compute core

- 8-way instruction dispatch

- L1 I-cache: 64 KB/core

- L1 D-cache: 64 KB/core

- L2 cache prefetcher

- 39 bits Physical Address Space

- MMU with 2048-entry, 8-way TLB

Other IP blocks and software

The company also introduced “Processor System IP blocks” required for the design of SoCs, including a Coherent Cluster Cache, I/O MMU, and Interrupt Controller IPs. Akeana also provides Scalable Mesh and Coherence Hub IP (compatible with AMBA CHI) to build large coherent compute subsystems for data centers and other use cases. Finally a AI Matrix computation engine designed to offload Matrix Multiply operations for AI acceleration is also available.

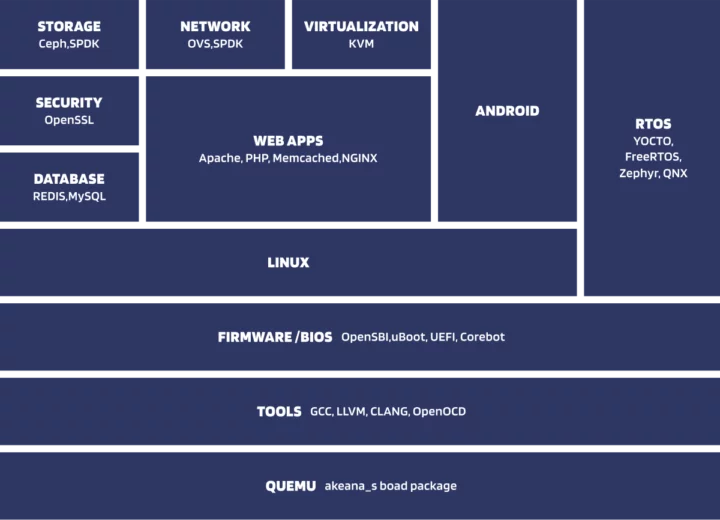

We have limited information about software, but Akeana provides an SDK with:

We can see Android and Linux are supported for application processors, and FreeRTOS, Zephyr, and QNX for microcontrollers.

Additional information may be found on the company’s website and in the announcement.

Thanks to TLS for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress