Microchip has introduced its first 64-bit RISC-V microprocessor family with the PIC64GX pin-to-pin compatible with the company’s PolarFire SoC FPGA devices and designed for edge designs for the industrial, automotive, communications, IoT, aerospace, and defense segments.

The PIC6GX MPU supports asymmetric multiprocessing (AMP) to run Linux, real-time operating systems, and bare metal in a single processor cluster with secure boot capabilities. The company further claims the PIC64GX MPU is “the first RISC-V multi-core solution that is AMP capable for mixed-criticality systems”. The first member of the PIC64GX RISC-V family is the PIC64GX1000 microprocessor.

Microchip PIC64GX1000 specifications:

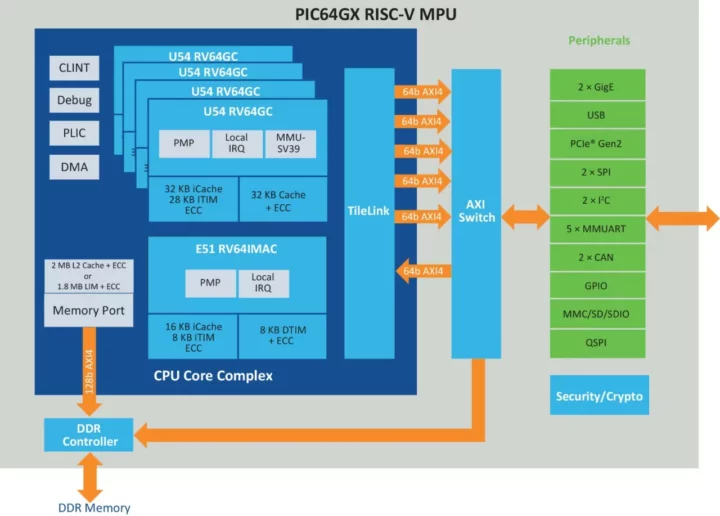

- CPU

- Quad-core SiFive U54 64-bit five-stage, single-issue, in-order pipeline RISC-V (RV64GC) processor at up to 625 MHz with AMP and deterministic latencies, PMP and MMU units

- Single-core SiFive E51 64-bit RISC-V (RV64IMAC) monitor processor core at up to 625 MHZ with PMP unit

- Cache

- L1 memory subsystem with Single-Error Correct, Double-Error Detect (SECDED)

- Flexible 2 MB L2 memory subsystem with SECDED configurable as:

- 128 KB of user Nonvolatile Memory (NVM) for boot Flash

- 56 KB of secure NVM for user data and key storage

- Memory

- Integrated 36-bit DDR4-1333/LPDDR4-1333 memory controller with SECDED, up to 32 Gbit per DDR interface

- 2 MB embedded SRAM for scratchpad memory

- Storage – MultiMedia Card (MMC) 5.1, SD, SDIO

- Video Output – HDMI 1.4 with dedicated I2C and HPD signals

- Camera I/F – Two-lane MIPI CSI-2 at 1 Gbps for connection to cameras and sensors

- Networking – 2x identical Gigabit Ethernet MACs (GEM)

- USB – 1x USB 2.0 OTG

- Expansion

- PCIe Gen 2 x4 (FCV) or x1 (FCS) root ports

- Coprocessor/Accelerator Interfaces

- Peripheral Interfaces – 2x SPI, 5x multi-mode UARTs, 2x I2C, 32x GPIOs, two CAN Bus, timers and watchdogs

- Security

- 256-bit AES/SHA, TRNG, HMAC, RSA, ECDSA

- Built-in tamper detectors and countermeasures

- DPA protection

- Standard secure boot and user-defined secure boot

- Spectre and Meltdown immunity

- Physical memory protection

- SECDED on all memories

- Packages

- FCSG325 (11 mm x11 mm , 0.5 mm) with 200x I/Os

- FCVG484 (19 mm x 19 mm, 0.8 mm) with 244x I/Os

- Temperature Range

- Commercial – 0 to +100°C

- Industrial – −40 to +100°C

The PCI64GX1000 is compatible with MPLAB IDE with RV64 and is supported by the Yocto Project Linux build system, Linux4Microchip, Canonical Ubuntu OS, and Zephyr RTOS. If we look into the product brief, we’ll find out other open-source RTOS are supported such as FreeRTOS, RTMES, Nuttx, and SafeRTOS, as well as commercial RTOS such as Siemens Nucleus, Sel4 uKernel, PikeOS, WindRiver VxWorks, and Greenhills µ-velOSity & Integrity. The PIC64GX GitHub account hosts bare-metal drivers, start-up code, RTOS, Linux build systems, BSP, and reference examples.

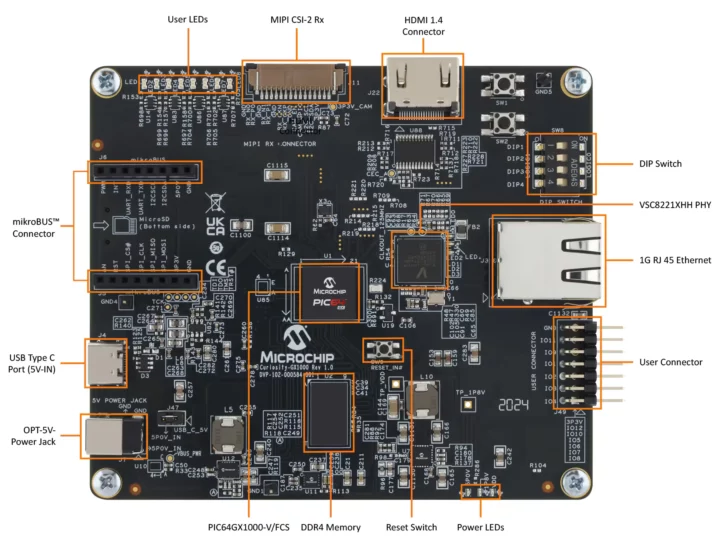

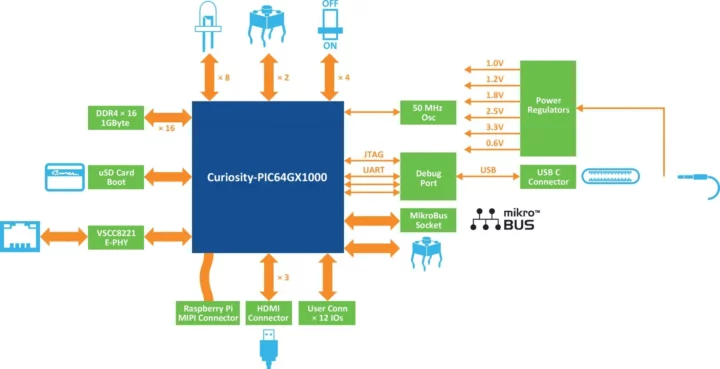

Engineers can get started with the 4×4-inch PIC64GX Curiosity Evaluation Kit powered by the PIC64GX1000-V/FCS microprocessor, equipped with 1GB DDR4 memory, and offering a range of interfaces including one Gigabit Ethernet, a MIPI CSI-2 connector compatible with Raspberry Pi cameras, HDMI 1.4 output, three UART, a microSD slot, a USB debug interface, and a mikroBus connector for expansion.

There’s no publicly available availability and pricing information for the PIC64GX microprocessor, but the PIC64GX Curiosity Kit is said to be available now with no price provided, and we are told to “contact Microchip Local Sales for pricing and availability”. More details can be found on the product page and the press release. There are also space-grade, radiation- and fault-tolerant PIC64 “High-Performance Spaceflight Computing” (PIC64-HPSC) MPUs based on the same design that should become available soon.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress