The PCI-SIG first unveiled the PCIe Express (PCIe) 7.0 specification at US DevCon in June 2022 with claims of bidirectional data rates of up to 512GB/s in x16 configuration, and the standard is now getting closer to the full release in 2025 with the release of the specification version 0.5.

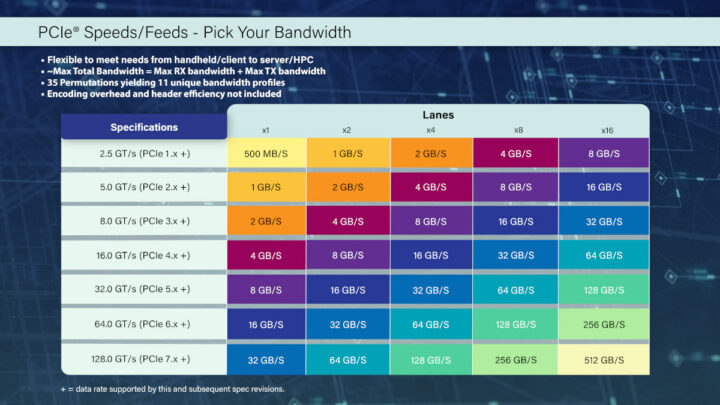

PCIe 7.0 increases data transfer speeds to 128 GT/s per pin doubling the 64 GT/s of PCIe 6.0 and quadrupling the 32 GT/s of PCIe 5.0, delivering up to 256 GB/s in each direction in x16 configuration, excluding encoding overhead. In other words, the total maximum bandwidth of a PCIe 7.0 x1 interface (32GB/s) would be equivalent to PCIe Gen3 x16 or PCIe Gen4 x8 as shown in the table below.

PCIe 7.0 highlights:

- 128 GT/s raw bit rate and up to 512 GB/s bidirectionally via x16 configuration

- PAM4 (Pulse Amplitude Modulation with 4 levels) signaling

- Doubles the bus frequency at the physical layer compared to PCIe 5.0 and 6.0, meaning around 30 GHz!

- Keep the 1b/1b FLIT mode encoding and the forward error correction (FEC) in PCIe 6.0

- Focuses on the channel parameters and reach

- Delivers low-latency and high-reliability targets

- Improves power efficiency

- Maintains backward compatibility with all previous generations of PCIe technology

PCIe 7.0 is probably a long way before getting into embedded systems and consumer products as it targets “data-intensive markets” such as 800Gbps Ethernet, Artificial Intelligence/Machine Learning, Hyperscale Data Centers, HPC, Quantum Computing, and the Cloud.

Anadtech says the next major step is finalization of the version 0.7 of the specification (aka the Complete Draft) which will freeze the standards’s features set. They also note that PCIe 6.0 went through 4 major drafts – 0.3, 0.5, 0.7, and 0.9 – before finally being finalized and that PCIe 7.0 might follow the same path before the final release in 2025. Even then, it will take a few years for datacenter-grade hardware to hit the shelves, and we are probably talking sometime in the 2030s before regular users can get their hands on PCIe 7.0 capable hardware.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress