Espressif ESP32-C5 microcontroller was announced in June 2022 as the first dual-band WiFi 6 IoT chip from the company. It’s been quiet since then, but things are about to change as the ESP32-C5 beta board’s documentation has very recently been released.

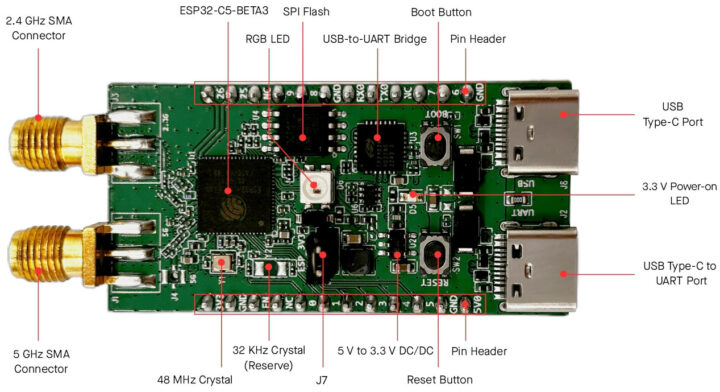

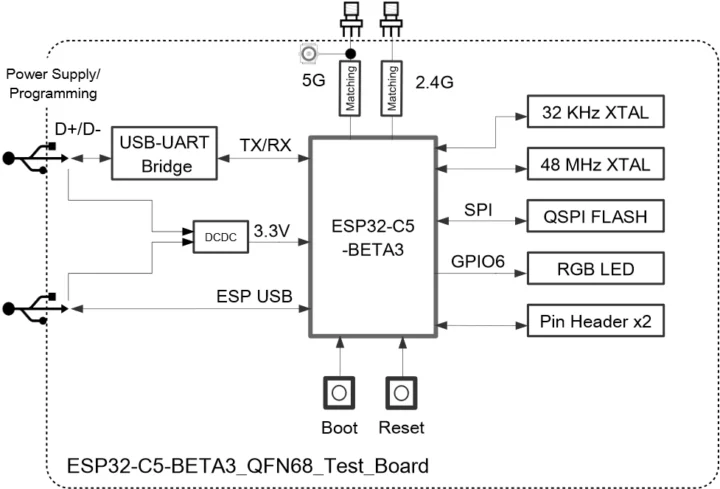

The ESP32-C5 was initially announced as a dual-band WiFI 6 and Bluetooth 5.0 LE SoC, but the user manual for the beta board indicates that it also supports Zigbee 3.0 and Thread 1.3, so there’s an 802.15.4 in the wireless microcontroller. The ESP32-C5 board itself features two SMA connectors for 2.4 GHz and 5GHz antennas or test equipment, two USB-C ports, two 12-pin GPIO header, Boot and Reset buttons, an RGB LED, and a 2-pin header for current measurements.

ESP32-C5 beta board specifications:

- SoC – ESP32-C5-BETA3

- CPU – Single-core 32-bit RISC-V processor @ up to 240 MHz

- Memory – 400KB SRAM on-chip

- Storage – 384KB of ROM on-chip, support for external flash

- Connectivity

- Dual-band 802.11ax WiFi 6 in the 2.4GHz and 5 GHz bands, with 802.11b/g/n WiFi 4 standard support for backward compatibility

- 20MHz bandwidth for the 802.11ax mode

- 20/40MHz bandwidth for the 802.11b/g/n mode

- OFDMA (Orthogonal Frequency Division Multiple Access) mechanism for both uplink and downlink

- MU-MIMO capability for downlink

- Target Wake Time (TWT) support allows devices to sleep for an extended time period (important for battery life)

- Bluetooth 5.0 Low Energy (LE )

- 802.15.4 radio for Zigbee 3.0 and Thread 1.3

- Dual-band 802.11ax WiFi 6 in the 2.4GHz and 5 GHz bands, with 802.11b/g/n WiFi 4 standard support for backward compatibility

- Storage – 4MB SPI flash

- Antennas

- 2.4 GHz SMA connector for 50-Ohm rod antenna or testing via RF cable

- 5 GHz SMA connector for 50-Ohm rod antenna or testing via RF cable

- USB

- USB Type-C port – USB Serial/JTAG port with USB 2.0 full speed up to 12 Mbps (480 Mbps high-speed transfer mode is not supported). Used to power the board, flash applications to the chip, communicate with the chip using USB protocols, as well as for JTAG debugging.

- USB Type-C to UART port – Used to power the board, flash applications to the chip, as well as communication with the ESP32-C5-BETA3 chip via the onboard USB-to-UART bridge (up to 3 Mbps).

- Expansion – J5 and J6 12-pin GPIO headers; breadboard compatible

- Misc

- Power LED

- RGB LED driven by GPIO6

- Boot and Reset buttons

- J7 jumper for current measurement

- 32.768 KHz (RTC) and 48 MHz crystals (Note: the 32 KHz crystal is not mounted by default, and the XTAL_32K_P and XTAL_32K_N pins are used as GPIO0 and GPIO1).

- Power Supply

- 5V via either USB-C ports or 5V and GND pins

- 3.3V via 3V3 and GND pins

- 5V to 3.3 V DC/DC switching regulator

- Dimensions – TBD

You’ll find more hardware details in the user guide (PDF). Nothing is written about software support except it will be supported by the ESP-IDF framework, and I can see some ESP32-C5 code has been added to the GitHub repo and the esptool utility in the last few weeks or months. Espressif Systems has not announced anything yet and the Aliexpress store does not have any ESP32-C5 module or board, but it’s probably a matter of a few weeks or months before beta samples become available, and I’d expect third-party boards to launch sometime in H2 2024.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress