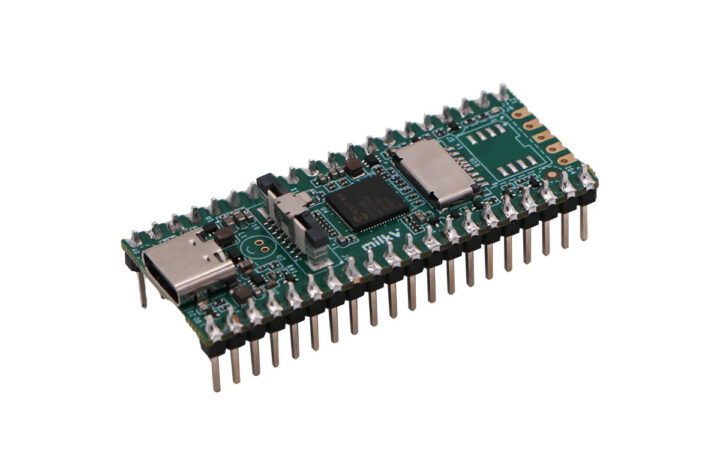

Duo 256M is a small board powered by SOPHGO SG2002 multi-architecture Arm/RISC-V/8051 SoC with 256MB of on-chip RAM and a 1 TOPS NPU, a microSD card for storage, a camera connector, a USB-C port for power and programming, and two headers for GPIO expansion.

We covered the SOPHGO SG2002 (and SG2000) Arm+RISC-V+8051 AI SoC earlier this month saying a couple of boards were expected very soon. We’ve already covered Sipeed LicheeRV Nano with optional Ethernet or WiFi 6, and now we’ll look at the Duo 256M designed by Milk-V Technology in more detail since it’s available now.

Duo 256M specifications:

- SoC – SOPHGO SG2002

- Main core – 1GHz 64-bit RISC-V C906 or Arm Cortex-A53 core (selectable)

- Minor core – 700MHz 64-bit RISC-V C906 core

- Low-power core – 25 to 300MHz 8051 MCU core

- NPU – 1 TOPS INT8, supports BF16

- Integrated 256MB DDR3 (SiP)

- Storage

- MicroSD card slot

- 32Gbit NAND flash (CSNP32GCR01)

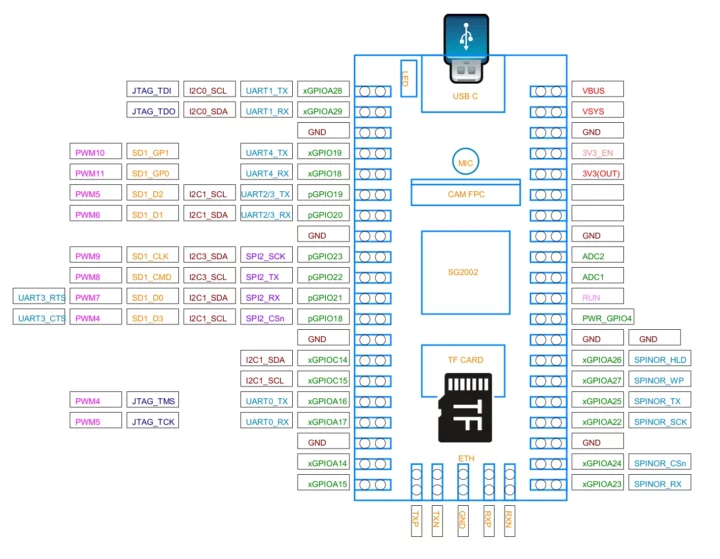

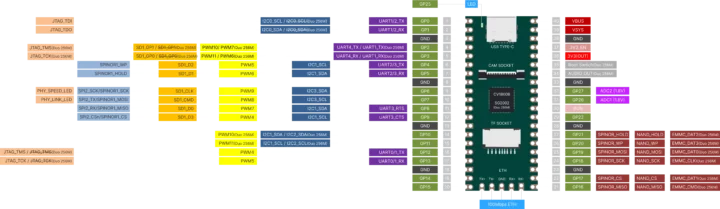

- Camera Interface – 4-lane MIPI CSI input connector

- Audio – Built-in microphone

- Networking – Support for 100Mbps Ethernet via adapter connected to 5x I/O pins

- USB – 1x USB Type-C port for power and programming

- Expansion – 2x 20-pin 2.54 pitch headers with access to GPIO, PWM, I2C, SPI, UART, JTAG, ADC, Audio, Arm/RISC-V switch signal

- Misc – Power LED

- Power Supply – 5V via USB-C port

- Dimensions – 51 x 21mm

You’ll find hardware documentation – including schematics, PCB layout, and datasheets – on GitHub. Instructions to getting started with buildroot (Linux 5.10 + FreeRTOS), the TDL SDK leveraging the NPU for computer vision workloads (e.g. face detection, face tracking, license plate recognition, gesture detection, etc…), and various code samples for GPIO and other features on the documentation website.

The Duo 256M board can be purchased for $7.99 plus shipping on Arace Tech. If you are interested in building your own board based on SG2000 or SG2002, samples of the chips can be purchased for respectively $6 and $5 each in packs of 5 pieces ($30 and $25).

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress