Arm Cortex-M52 is a new microcontroller core featuring Arm Helium technology and designed to bring AI capabilities to smaller and lower-cost IoT devices than what is already possible with SoCs based on the Arm Cortex-M55 core.

Arm Cortex-M52 key features and specifications:

- Architecture – Armv8.1-M

- Bus interfaces

- AMBA 5 AXI 32-bit or AMBA 5 AHB 32-bit Main system bus

- AMBA 5 AHB 32-bit Peripheral bus

- AMBA 5 AHB 32-bit TCM Access bus (subordinate port)

- Pipeline – 4-stage pipeline

- Security

- Arm TrustZone technology (optional), with optional Security Attribution Unit (SAU) of up to 8 regions. Stack limit checking.

- Optional support for PACBTI extension (Pointer Authentication, Branch Target Identification)

- Memory Protection – Optional Memory Protection Units (MPU) for process isolation with up to 16 MPU regions and a background region – if TrustZone is implemented, there can be a Secure and a Non-secure MPUs.

- DSP extension – 32-bit DSP/SIMD extension

- Optional single-beat Helium, supporting up to

- 1 x 32-bit MACs/cycle

- 2 x 16-bit MACs/cycle

- 4 x 8-bit MACs/cycle

- Floating-point Unit (FPU) – Optional FPU with support for half-precision (fp16), single precision (fp32), and double precision (fp64) floating-point operations.

- Accelerator support

- Optional coprocessor interface (64-bit) supporting up to 8 coprocessor units for custom compute accelerators

- Optional Arm Custom Instructions

- Instruction cache – Up to 64kB with ECC (optional)

- Data cache – Up to 64kB with ECC (optional)

- Instruction TCM (ITCM) – Up to 16MB with ECC (optional)

- Data TCM (DTCM) – Up to 16MB with ECC (optional)

- Interrupts – Integrated Nested Vectored Interrupt Controller (NVIC) supporting up to 480 interrupts + Non-maskable interrupt (NMI). Number of priority levels configurable from 8 to 256.

- Wake-up Interrupt Controller (WIC) – Internal and/or external (optional) WIC for waking up the processor from state retention power gating or when all clocks are stopped.

- Low power support

- Architecturally defined Sleep and Deep Sleep modes

- Integrated wait for event (WFE) and wait for interrupt (WFI) instructions with Sleep On Exit functionality

- Sleep and Deep Sleep indication signals

- Multiple power domains with optional retention support for memories and logic

- Performance efficiency: 4.3 CoreMark/MHz and 1.6 DMIPS/MHz

- Debug

- Hardware and software breakpoints

- Performance Monitoring Unit (PMU)

- Trace

- Optional Instruction trace with Embedded Trace Macrocell (ETM), Data Trace (DWT) (selective data trace), and Instrumentation Trace (ITM) (software trace)

- Robustness

- ECC on instruction cache, data cache, instruction TCM, data TCM (optional)

- Dual core lock step (optional)

- Bus interface protection (optional)

- PMC-100 (Programmable MBIST Controller, optional)

- Reliability, availability and serviceability (RAS) extension

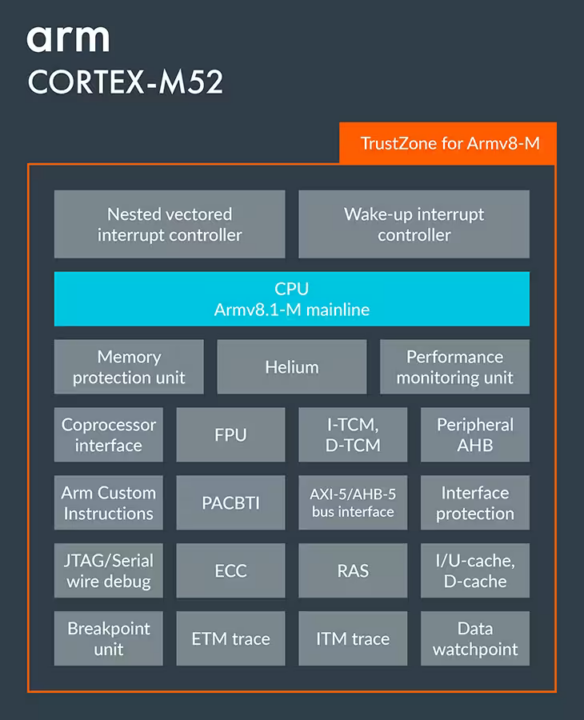

The block diagram of the Cortex-M52 is virtually identical to the one for the Cortex-M55, apart from the PACBTI block showing up instead of the DSP block, the “AXI-5 master” string is replaced by “AXI-5/AHB-5 bus interface”. So there doesn’t seem to be that many differences but Arm provides a comparison table for all Arm Cortex-M processors which I reproduced with the Armv8 cores and the Cortex-M7 to better understand the differences. (smartphone users may want to rotate their phone in landscape mode to read the table)

| Feature | Cortex- M33 | Cortex- M35P | Cortex-M52 | Cortex-M55 | Cortex-M7 | Cortex-M85 |

|---|---|---|---|---|---|---|

| Instruction Set Architecture | Armv8-M Mainline | Armv8-M Mainline | Armv8.1-M Mainline | Armv8.1-M Mainline | Armv7-M | Armv8.1-M Mainline |

| TrustZone for Armv8-M | Yes (option) | Yes (option) | Yes (option) | Yes (option) | No | Yes |

| Helium (M-Profile Vector Extension) | No | No | Single-beat (option) | Dual-beat (option) | No | Dual-beat (option) |

| PACBTI Extension | No | No | Yes (option) | No | No | Yes (option) |

| Floating-Point Unit (FPU) | SP (option) | SP (option) | HP, SP, DP (option) | HP, SP, DP (option) | SP, DP (option) | HP, SP, DP (option) |

| Digital Signal Processing (DSP) | Yes (option) | Yes (option) | Yes | Yes | Yes | Yes |

| Hardware Divide | Yes | Yes | Yes | Yes | Yes | Yes |

| Arm Custom Instructions | Yes (option) | No | Yes (option) | Yes (option) | No | Yes (option) |

| Coprocessor Interface | Yes (option) | Yes (option) | Yes (option) | Yes (option) | No | Yes (option) |

| DMIPS/MHz | 1.54 | 1.50 | 1.60 | 1.69 | 2.31 | 3.13 |

| CoreMark/MHz | 4.10 | 4.10 | 4.30 | 4.40 | 5.29 | 6.28 |

| Maximum # External Interrupts | 480 | 480 | 480 | 480 | 240 | 480 |

| Maximum MPU Regions | 16 | 16 | 16 | 16 | 16 | 16 |

| Main Bus | AHB (32-bit) | AHB (32-bit) | AXI (32-bit) or AHB (32-bit) | AXI (64-bit) | AXI (64-bit) | AXI (64-bit) |

| Instruction Cache | No | 2-16KB | 0-64KB | 0-64KB | 0-64KB | 0-64KB |

| Data Cache | No | No | 0-64KB | 0-64KB | 0-64KB | 0-64KB |

| Instruction TCM | No | No | 0-16MB | 0-16MB | 0-16MB | 0-16MB |

| Data TCM | No | No | 0-16MB | 0-16MB | 0-16MB | 0-16MB |

| Dual Core Lock-Step (DCLS) Configuration | No | Yes | Yes (option) | Yes (option) | Yes (option) | Yes (option) |

We can indeed see some more differences between the Cortex-M52 and Cortex-M55 with the former supporting single-beat Helium against dual-beat Helium for the latter, and the main bus is 32-bit for the new part, while the Cortex-M55 supports a 64-bit AXI bus. This may explain why Arm says the Cortex-M52 provides a simplified migration path from the Cortex-M33 and Cortex-M4 for AIoT applications in automotive and industrial control, predictive maintenance, and wearable sensor fusion.

The Cortex-M52 provides better efficiency, a smaller footprint, and a lower price point compared to the Cortex-M55 and Cortex-M85 cores at the cost of delivering lower performance. But the company still claims that “developers can benefit from an uplift in both ML and DSP performance, with up to 5.6x performance uplift for ML and up to 2.7x performance uplift for digital signal processing compared to previous Cortex-M generations”, which I’d assume would be the aforementioned Cortex-M33/Cortex-M4 cores.

Arm Cortex-M52 will replace traditional (very) edge AI solutions comprised of a CPU, a DSP, and an NPU that require three separate toolchains, compilers, debuggers, etc… and enable developers to write with unified development flow with a single toolchain and other development tools for traditional, DSP and ML workloads. It also remains fully software-compatible with the Cortex-M55 and Cortex-M85 cores. Since it may take a while before actual silicon becomes available, the Cortex-M52 will soon be available on Arm Virtual Hardware to kickstart software development ahead of time.

It may take a while before Arm Cortex-M52 microcontrollers are brought to market, and I’d expect announcements starting in 2025. More information may be found on the product page and in the announcement.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress