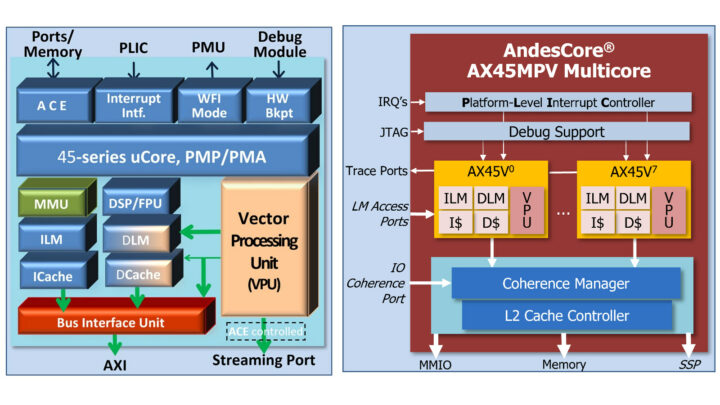

Andes Technology has recently announced the general availability of the AndesCore AX45MPV RISC-V CPU which builds upon the AX45MP multicore processor and adds RISC-V Vector Extension 1.0.

Equipped with RISC-V vector processing and parallel execution capability, the new RISC-V CPU core targets SoCs processing large amounts of data for applications such as ADAS, AI inference and training, AR/VR, multimedia, robotics, and signal processing.

Diagram (right)

AX45MPV key features and specifications:

- 64-bit in-order dual-issue 8-stage CPU core with up to 1024-bit Vector Processing Unit (VPU) – compliant with RISC-V V-extension (RVV) 1.0 + custom extensions

- Supports clusters of up to 8 cores

- L2 cache and coherence support

- High bandwidth vector local memory (HVM)

- AndeStar V5 Instruction Set Architecture (ISA)

- Compliant with RISC-V GCBPV extensions

- Andes performance extension

- Andes CoDense extension for further compaction of code size

- Separately licensable Andes Custom Extension (ACE) for customized scalar and vector instruction

- 64-bit architecture for memory space over 4GB

- Branch predication to speed up control code

- Memory Management Unit (MMU), Physical Memory Protection (PMP), and programmable Physical Memory Attribute (PMA)

- Andes-enhanced Platform-Level Interrupt Controller (PLIC) for system events and real-time performance

- Platform-level Interrupt Controller (PLIC) support with an arrangement of preemptive interrupts

- ECC or Parity for SRAM error protection

- Configurable VPU vector length (VLEN) and datapath length (DLEN)

- StackSafe hardware to help measure the stack size and detect runtime overflow/underflow

- Versatile configurations to trade off between core size and performance requirements

- PowerBrake and WFI (Wait For Interrupt) for different power-saving occasions

Thanks to TLS for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress