The Sipeed Tang Nano 20K is a low-cost FPGA development board based on Gowin GW2AR-18 FPGA with 20,736 logic cells and 64Mbit RAM, which coupled with 64MBit QSPI flash provides enough resources to simulate a 32-bit RISC-V core booting Linux or playing retro games in an emulator.

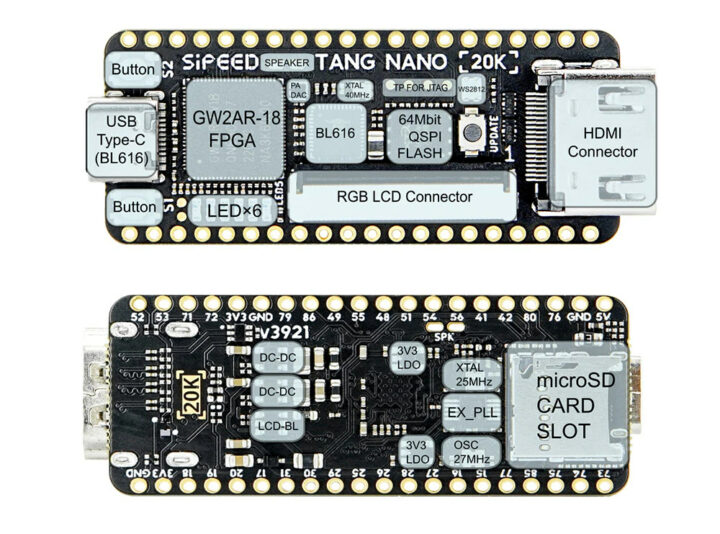

The FPGA board comes with a USB-C port for power and to load the FPGA bitstream through a BL616 microcontroller that also acts as a USB to serial chip, an HDMI port and an RGB LCD interface for video output, two user buttons, and two rows GPIOs to connect peripherals such as gamepads (through adapters).

Sipeed Tang Nano 20K specifications:

- FPGA – Gowin GW2A-LV18QN88C8I7 with

- 20,736 logic units (LUT4)

- 15,552 flip-flops (FF)

- RAM

- 41,472 shadow SRAM (S-SRAM)

- 828K block SRAM (B-SRAM)

- Numbers of B-SRAM – 46

- 64Mbit 32-bit SDR SDRAM

- 48x 18×18 multipliers

- 2x PLLs

- 8x I/O Bank

- Onboard debugger – Bouffalo Labs BL616 32-bit RISC-V CPU (RV32IMAFCP) @ up to 320 MHz, 480KB SRAM, embedded flash for

- JTAG for FPGA

- USB to UART for FPGA

- USB to SPI for FPGA communication

- Control frequency generated by the MS5351

- Clock generator – MS5351 provides 3 extra clocks for the FPGA

- Storage – 64Mbit QSPI flash to save the FPGA bitstream, microSD card slot for data

- Display interfaces

- 40-pins RGB LCD connector

- HDMI port

- Audio – MAX98357A PCN amplifier, 2-pin header for speaker

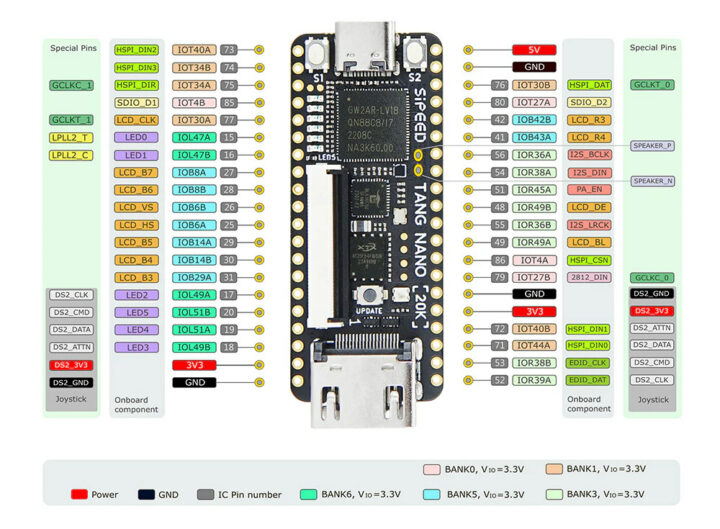

- Expansions – 40-pin GPIO header with SPI, SDIO, I2S, LCD, HDMI EDID, etc…

- Misc – 6x LEDs, 1x RGB LED (WS2812), 2x user keys, update button

- Power Supply – 5V via USB-C port

- Dimensions – 54.04 x 22.55mm

The company has showcased a 48MHz 32-bit RISC-V VexRiscv softcore (Litex firmware) running on the FPGA and booting a minimal Linux image in the Twitter video embedded below. You’ll also find various samples to control HDMI and RGB LCD interfaces, audio output, UART, and the LEDs on GitHub. Another fun project is the NESTang FPGA Nintendo Entertainment System working on Sipeed Tang Nano 20K and Primer 20K boards. Programming is done through the Gowin IDE, and you’ll find the resources to get started and further hardware documentation (schematics, datasheets, etc…) in the wiki.

#FPGA Tang Nano 20K run #RISCV RV32IMA, boot up #Linux ! pic.twitter.com/gMOeps4Kf2

— Sipeed (@SipeedIO) May 18, 2023

Sipeed has just started selling the Tang Nano 20K development board on Aliexpress for $25 and up. You’ll also find accessories there such as 4.3-inch or 5-inch displays, and even a full retro game kit (about $48) with the board, two joysticks with adapters, a breadboard, and a USB cable to run the NESTang bitstream and play some NES games using the HDMI port at 720p resolution and with audio.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress