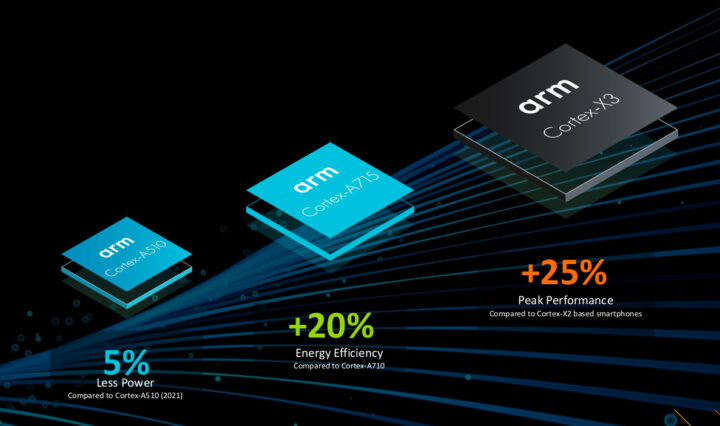

Besides announcing the new Immortalis-G715, Mali-G715, and Mali-G615 GPUs, Arm has also introduced the second-generation of Armv9 cores with the Cortex-A715 and Cortex-X3 cores with respectively a 20% energy-efficiency improvement (and smaller 5% performance uplift) over the Cortex-A710 core and a 25% peak performance boost against the Cortex-X2 flagship core.

The announcement also includes a “refresh” of the Cortex-A510 core announced last year with a 5% improvement in efficiency and the same level of performance. The Cortex-X3 will also be used in (Windows 11) laptop processors with the single-thread performance improved by up to 34% in that case.

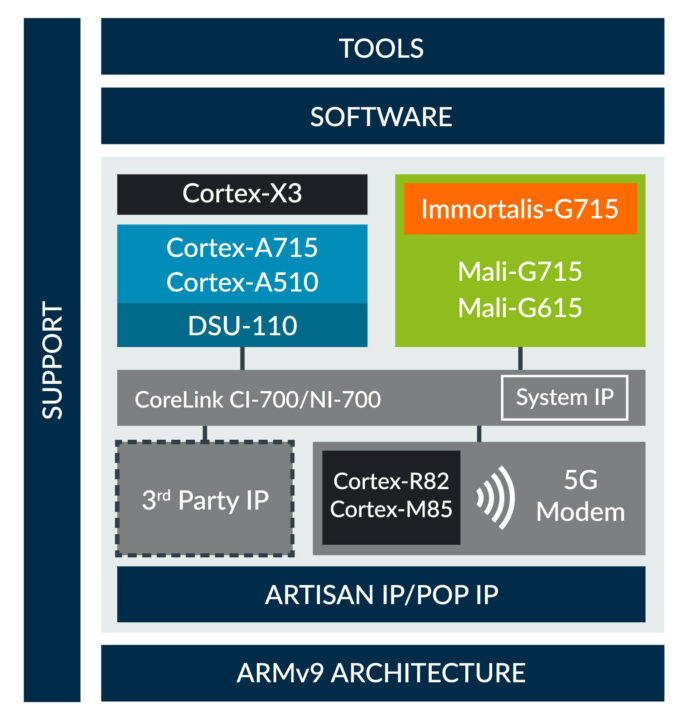

Armv9 mobile SoC (Total Compute) in 2023

Future Armv9 flagship mobile SoC worked on this year, and released in 2023 should have a combination of Cortex-X3, Cortex-A715, and Cortex-A510 cores, an Immortalis-G715 GPU, a new DSU-110 “DynamIQ Shared Unit” that supports 50% more cores in CPU clusters (or up to 12 cores per clusters) with up to 16MB L3 cache, and a 5G modem equipped with Cortex-R82 and/or Cortex-M85 cores.

Future Armv9 flagship mobile SoC worked on this year, and released in 2023 should have a combination of Cortex-X3, Cortex-A715, and Cortex-A510 cores, an Immortalis-G715 GPU, a new DSU-110 “DynamIQ Shared Unit” that supports 50% more cores in CPU clusters (or up to 12 cores per clusters) with up to 16MB L3 cache, and a 5G modem equipped with Cortex-R82 and/or Cortex-M85 cores.

Arm expects up to 28% more performance and up to 16% power reduction across a range of workloads, such as gaming, to enable longer play time. Processors will be offered with up to 8x Cortex-X3 CPU cores and 4 Cortex-A715 CPU cores for premium laptops delivering up to 120% performance improvement in GeekBench 5 compared to existing (2021) Arm-based laptops with 1x Cortex-X2, 3x Cortex-A710, 4x Cortex-A510. Another interesting tidbit is that the Cortex-A715 now matches the performance of the Cortex-X1 announced in 2020.

More technical details may be found in a post on Arm’s community website.

Arm CPU & GPU roadmap to 2024

Arm also divulged a simplified roadmap for 2023 and 2024 designs with new cores codenamed Hunter, Chaberton, and Hayes (LITTLE core), a new Hayden DSU (for even larger clusters?), and a new interconnect codenamed “Tower” appearing in the 2024 IP. The new GPUs for 2023 and 2024 also have their own codenames, respectively Titan and Krake. There aren’t any public details, but at least we’ll roughly know that those are if they appear in silicon vendor roadmaps.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress